開源RISC-V Hummingbird E203(蜂鳥E203)的仿真工具是開源的iverilog,這里利用vcs+verdi仿真工具進行仿真;

蜂鳥 E200 主要面向極低功耗與極小面積的場景,非常適合于替代Cortex-M 系列內核應用于IoT或其他低功耗場景。

E200系列處理器核使用Verilog語言,采用兩級流水線結構,通過一流的處理器架構設計CPU的功耗與面積均優于同級ARM Cortex-M核, 實現業界最高的能效比與最低的成本;

E200 系列處理器核能夠運行RISC-V指令 ,支持RV321/E/A/M/C/F/D 等指令子集的配置組合,支持機器模式(Machine Mode Only);

E200 系列處理器核提供標準的JTAG調試接口以及成熟的軟件調試工具;

E200 系列處理器核提供成熟的GCC編譯工具鏈;

E200 系列處理器核配SoC提供緊耦合系統 IP 模塊,包括中斷控制器、計時器UART,QSPI,PWM等,即時能用(Ready-to-Use)的soc平臺與PPGA原型系統。

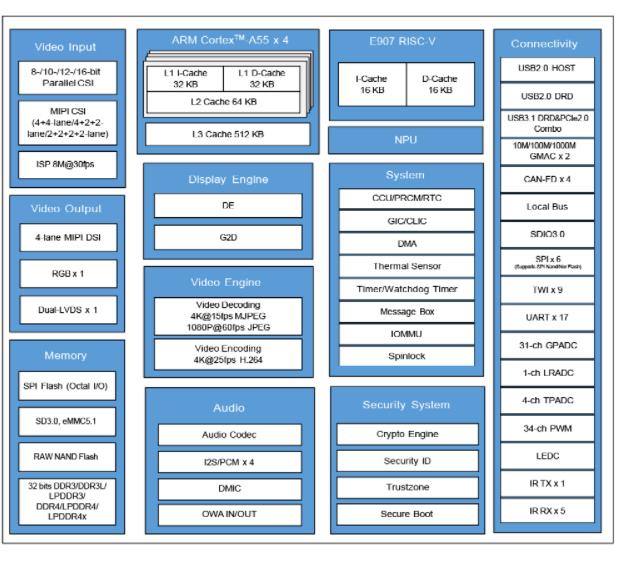

E200系列處理器Soc示意圖

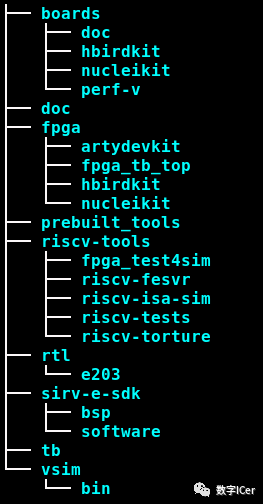

目錄:

項目目錄

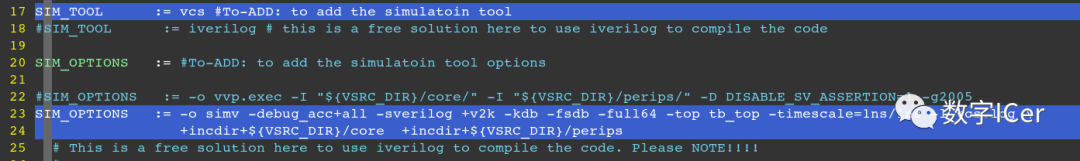

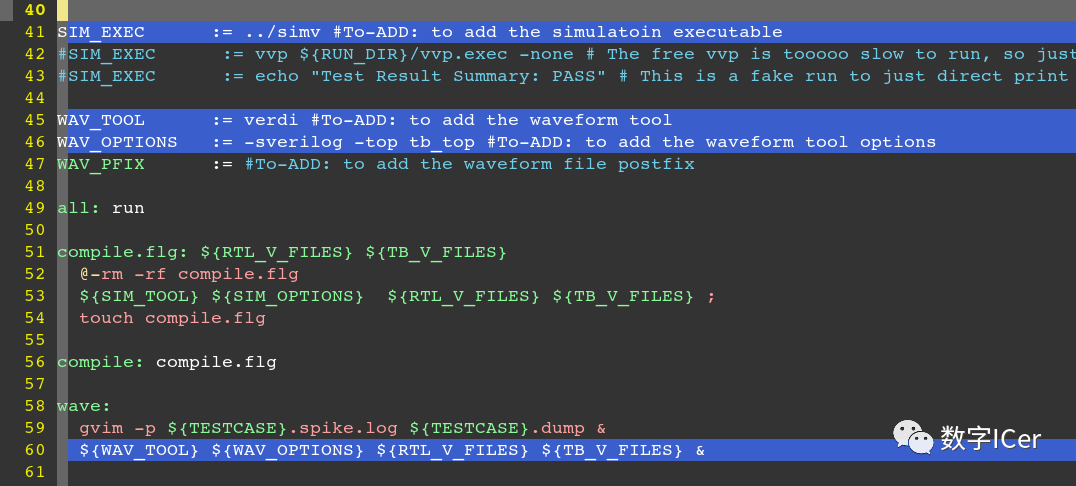

修改

1.修改e200_opensource-master/vsim/bin文件中的run.makefile,修改vcs,verdi仿真工具和仿真選項,如下:

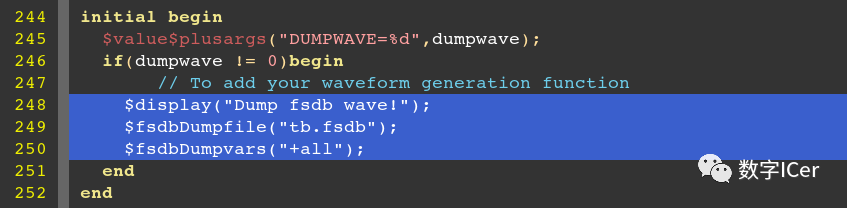

2.e200_opensource-master/tb/tb_top.v增加dump波形

仿真

步驟1:編譯 RTL 代碼,使用如下命令:

進入到 e200_opensource 目錄文件夾下面的 vsim 目錄。

make install CORE=e203

運行該命令指明需要為e203進行編譯,該命令會在vsim目錄下生成一個install子文件夾,在其中放置所需的腳本,且將腳本中的關鍵字設置為e203。

make compile

運行該命令編譯Core和 SoC的RTL代碼

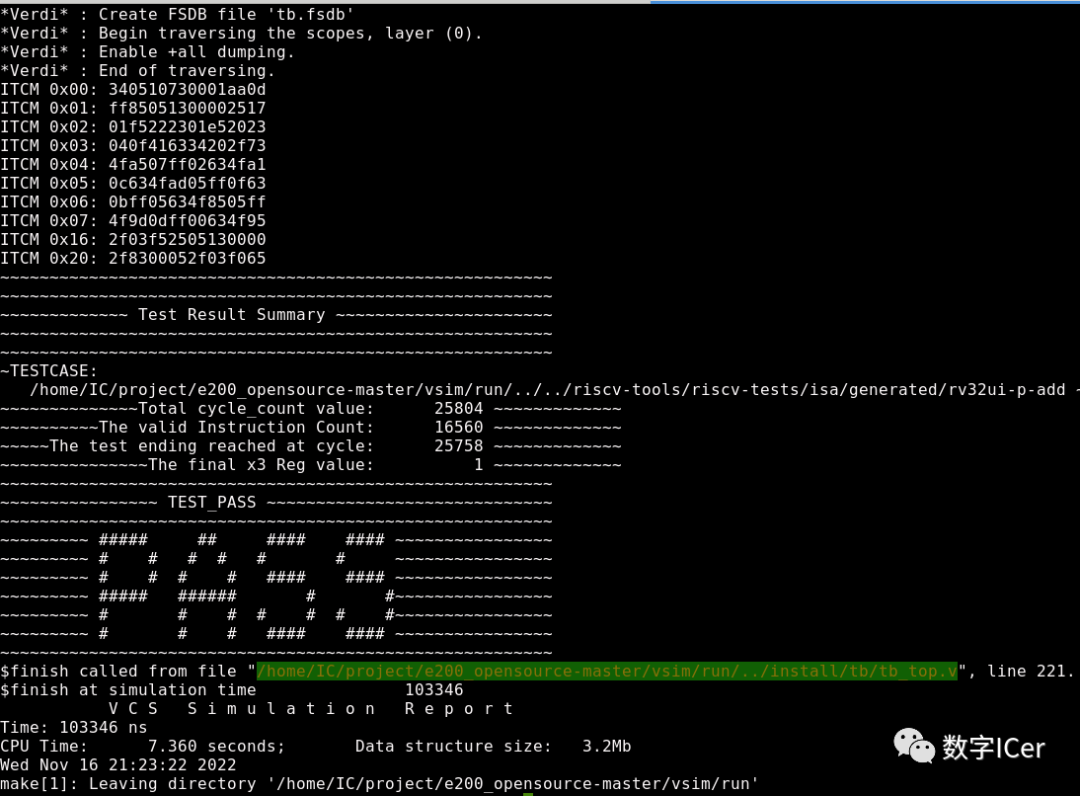

步驟2:運行默認的一個testcase(測試用例),使用如下命令:

make run_test

make run_test將執行e200_opensource/riscv-tools/riscv-tests/isa/generated目錄中的一個默認testcase,如果測試用例運行通過則打印PASS,并生成波形,如下圖,

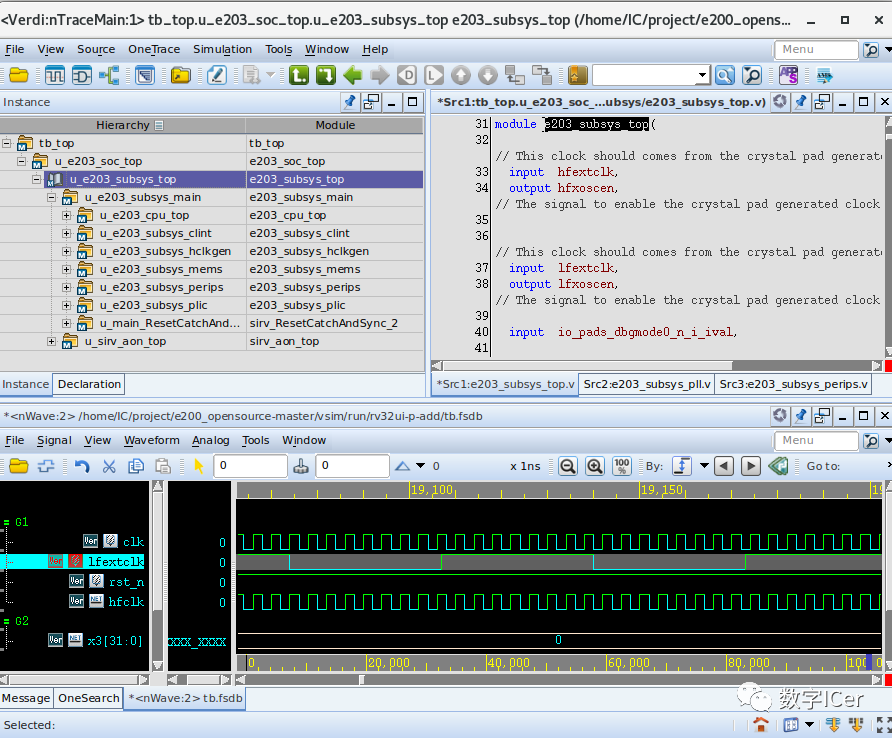

步驟3:打開verdi,加載波形

使用如下命令:make wave

如果希望運行所有的回歸測試,請參見步驟4。

步驟4 運行回歸 regression 測試集 ,使用如下命令

make regress_run CORE=e203

該命令使用e200_opensource/riscv-tools/riscv-tests/isa/generated目錄中E203 Core testcases 逐個的運行各testcase.

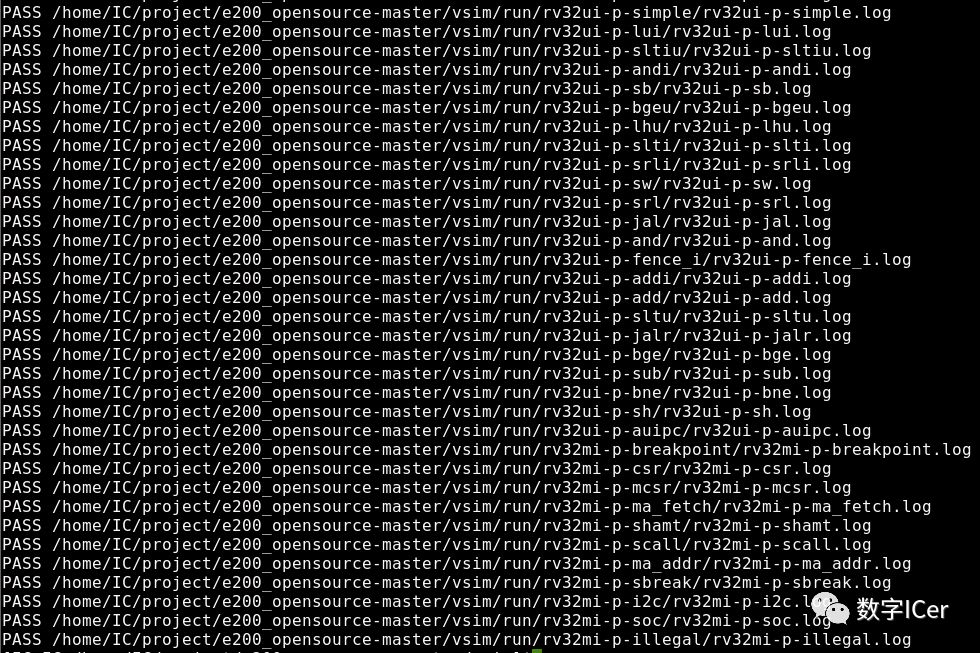

步驟5:查看回歸測試結果

make regres_ collect CORE=e203

該命令將收集步驟4中運行的測試集的結果,每行對應一個測試用例,如果測試用例運行通過則打印 PASS ,如果運行失敗則打印 FAIL;

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19349瀏覽量

230324 -

仿真

+關注

關注

50文章

4102瀏覽量

133746

原文標題:開源RISC-V Hummingbird E203 | vcs+verdi仿真

文章出處:【微信號:數字ICer,微信公眾號:數字ICer】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EE-304:使用Blackfin處理器SPORT仿真SPI接口

EE-307: Blackfin處理器利用VisualDSP++工具的調試方法

車載總線監控分析及仿真工具 - VBA

全志T536系列處理器特性概述 集成RISC-V E907協處理器

英特爾發布酷睿Ultra 200S系列臺式機處理器

技嘉發布X870E/X870系列主板,專為AMD Ryzen 9000系列處理器設計

英特爾酷睿Ultra 200V系列處理器發布

仿真器的使用方法有哪些

【龍芯2K0300蜂鳥板試用】第一章:上電串口調試器

免費好用的在線仿真工具Wokwi

熱仿真工具Ansys Discovery的使用案例

利用vcs+verdi仿真工具蜂鳥E200系列處理器仿真分析

利用vcs+verdi仿真工具蜂鳥E200系列處理器仿真分析

評論