時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?如何用硬件配置pll? 時鐘發生器是指通過特定的電路設計產生適合各種電子設備使用的時鐘信號的器件。時鐘發生器由多個部分組成,其中最核心的是鎖相環

2023-10-13 17:39:50 99

99 9ZXL1951D PCIe 時鐘發生器評估板用戶指南

2023-07-07 19:19:11 0

0 電子發燒友網站提供《使用AD9850模塊和Arduino制作頻率信號發生器.zip》資料免費下載

2023-06-25 10:37:14 3

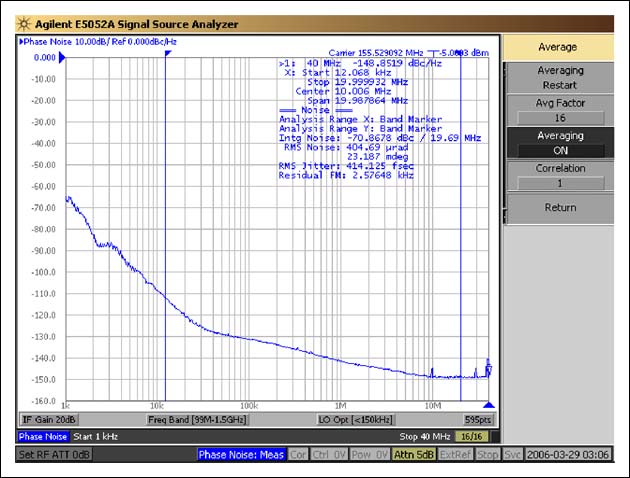

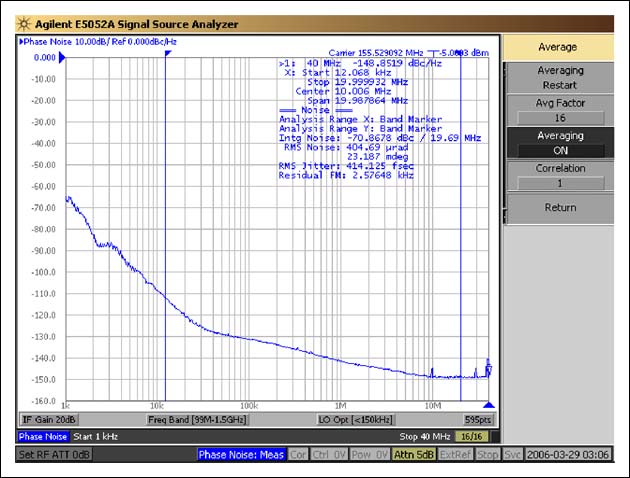

3 本文討論電源噪聲干擾對基于PLL的時鐘發生器的影響,并介紹幾種用于評估由此產生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 478

478

9ZXL1951D PCIe 時鐘發生器評估板用戶指南

2023-03-21 19:21:13 0

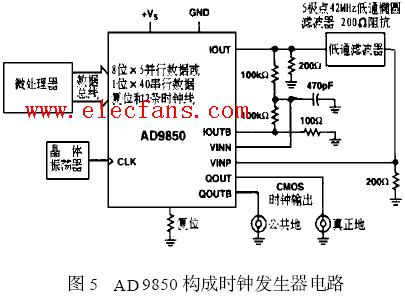

0 AD9850是一款高度集成的器件,采用先進的DDS技術,內置一個高速、高性能數模轉換器和比較器,共同構成完整的數字可編程頻率合成器和時鐘發生器。以精密時鐘源作為基準時,AD9850能產生頻譜純凈

2023-02-15 09:47:26

與典型的“本地”時鐘解決方案相比,使用集成的多輸出時鐘發生器具有許多優勢。本文討論集中式時鐘發生器(如MAX9489和MAX9471)在降低系統成本、良好信號完整性和消除干擾方面的優勢。它包括電路板設計,說明如何使用中央時鐘源克服一些基本設計挑戰。

2023-02-09 11:57:14 706

706

超低抖動時鐘發生器如何優化串行鏈路系統性能

2022-11-04 09:50:15 0

0 這是帶有板上芯片(COB)的1Hz時鐘發生器電路。通常,為數字時鐘和計數器電路應用產生1Hz時鐘的電路將IC與晶體和微調電容器等結合使用。

2022-06-07 10:43:50 1598

1598

。Cypress時鐘發生器兼容大量增值性能,如VCXO,擴頻和輸出相位校準,及其兼容流行接口標準的參考時鐘/3.0,如PCIe1.0/2.0/3.0、10GbE、SATA1.0/2.0和USB1.0

2022-04-22 09:02:09 679

679 時鐘發生器AD9516-0技術手冊

2022-01-25 15:59:42 4

4 本帖最后由 gk320830 于 2015-3-5 22:47 編輯

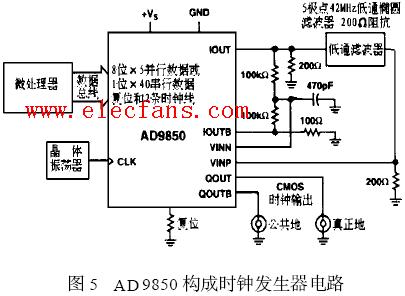

圖2 AD9850電路設計

2009-04-08 23:17:27

集成2.5 GHz壓控振蕩器數據表的AD9517-1 12輸出時鐘發生器

2021-06-17 15:57:38 6

6 集成2.0 GHz壓控振蕩器數據表的AD9518-3 6輸出時鐘發生器

2021-06-17 15:38:27 3

3 集成2.2 GHz壓控振蕩器數據表的AD9517-2 12輸出時鐘發生器

2021-06-17 12:31:30 3

3 AD9850 FS制革文件

2021-06-17 11:49:56 5

5 AD9517-0 12輸出時鐘發生器,集成2.8 GHz壓控振蕩器數據表

2021-06-16 12:14:49 4

4 AD9516-3:14輸出時鐘發生器,集成2.0 GHz壓控振蕩器數據表

2021-05-25 12:00:10 2

2 超低抖動時鐘發生器和分配器最大限度地提高數據轉換器的信噪比

2021-05-18 20:57:30 0

0 AD9576:雙鎖相環異步時鐘發生器數據表

2021-05-16 12:57:55 0

0 AD9531:3通道時鐘發生器,24輸出數據表

2021-05-15 15:24:07 11

11 AD9575:網絡時鐘發生器,雙輸出數據表

2021-05-09 11:06:44 1

1 AD9517-4:12輸出時鐘發生器,集成1.6 GHz壓控振蕩器數據表

2021-04-30 15:51:42 10

10 AD9547:雙/四輸入網絡時鐘發生器/同步器數據表

2021-04-30 08:48:14 10

10 集成2.2 GHz VCO數據表的AD9522-2:12 LVDS/24 CMOS輸出時鐘發生器

2021-04-29 20:28:12 11

11 AD9522-5:12 LVDS/24 CMOS輸出時鐘發生器數據表

2021-04-28 10:53:01 0

0 AD9551:多業務時鐘發生器數據表

2021-04-28 10:30:52 0

0 AD9516-5:14-輸出時鐘發生器數據表

2021-04-27 21:41:19 5

5 AD9520-5:12 LVPECL/24 CMOS輸出時鐘發生器數據表

2021-04-27 21:31:55 2

2 HMC1031:0.1 MHz至500 MHz時鐘發生器,帶整數N PLL數據表

2021-04-23 20:15:29 6

6 AD9548:四/八路輸入網絡時鐘發生器/同步器數據表

2021-04-16 11:41:04 10

10 AD9571:以太網時鐘發生器,10個時鐘輸出

2021-04-16 10:21:56 3

3 ADF4360-9:集成壓控振蕩器數據表的時鐘發生器PLL

2021-04-14 14:10:44 0

0 AD9517-0:12輸出時鐘發生器,集成2.8 GHz壓控振蕩器數據表

2021-04-13 12:10:21 0

0 AD9517-1:12輸出時鐘發生器,集成2.5 GHz壓控振蕩器數據表

2021-04-13 12:02:55 1

1 AD9517-2:12輸出時鐘發生器,集成2.2 GHz壓控振蕩器數據表

2021-04-13 11:57:48 0

0 AD9850 FS制革文件

2021-04-13 11:50:53 4

4 AD9518-3:6輸出時鐘發生器,集成2.0 GHz壓控振蕩器數據表

2021-04-13 11:13:25 2

2 AD9540:655 MHz低抖動時鐘發生器數據表

2021-03-22 19:57:57 0

0 AD9518-1:6輸出時鐘發生器,集成2.5 GHz壓控振蕩器數據表

2021-03-22 19:55:03 0

0 AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 主要對AD9850信號發生器模塊進行介紹說明。

2021-03-18 09:44:25 24

24 系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2020-11-22 11:34:38 2489

2489

新型AEC-Q100認證的時鐘發生器、緩沖器、PCIe時鐘和緩沖器滿足廣泛的車輛自動化應用需求。

2019-09-24 14:25:08 828

828 AD9523:14路LVPECL/LVDS/HSTL輸出 或29路LVCMOS輸出 低抖動時鐘發生器

2019-07-04 06:18:00 3365

3365 據麥姆斯咨詢報道,Microchip推出了業界尺寸最小的MEMS時鐘發生器DSC613。這款新器件可在電路板上最多替換掉三個晶振和振蕩器,從而減少高達80%的時鐘元件布板空間。

2018-11-15 16:38:26 3736

3736 Microchip基于MEMS的時鐘發生器

2018-07-08 01:23:00 3691

3691 Microchip基于MEMS的時鐘發生器

2018-06-07 13:46:00 4241

4241

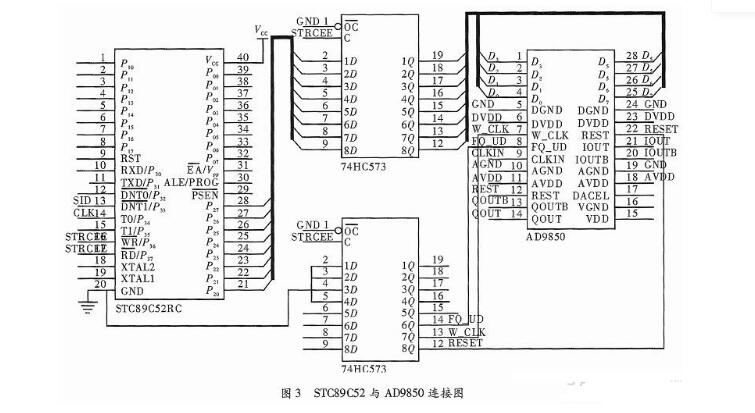

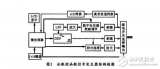

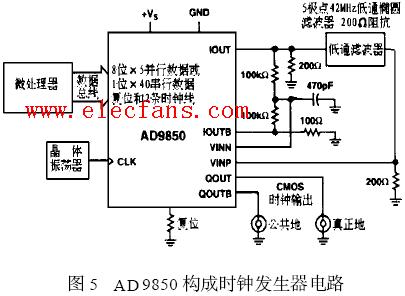

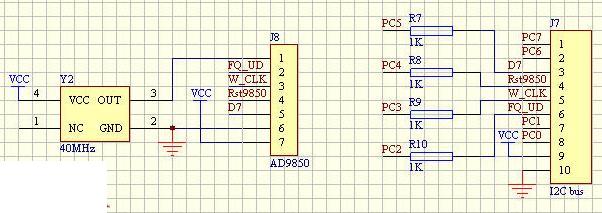

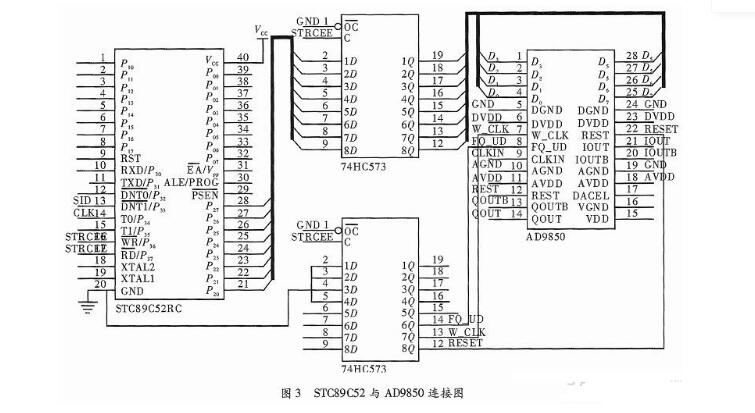

本文主要介紹了六款ad9850應用電路,其中包括了ad9850構成的信號發生器電路與與單片機的接口電路。

2018-04-13 15:21:53 12524

12524

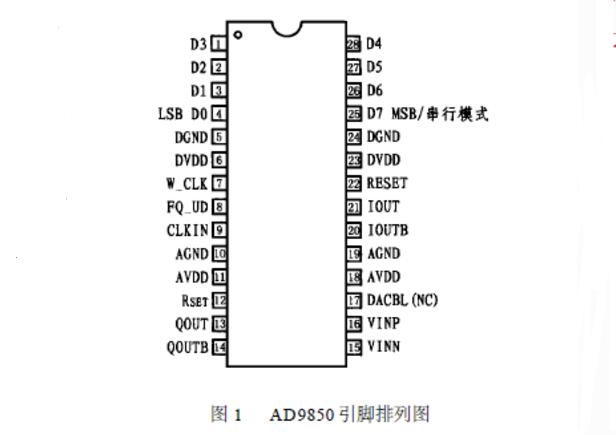

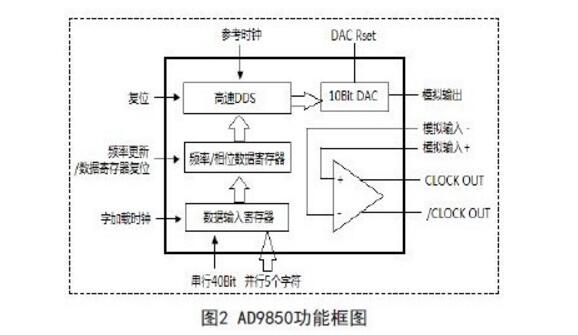

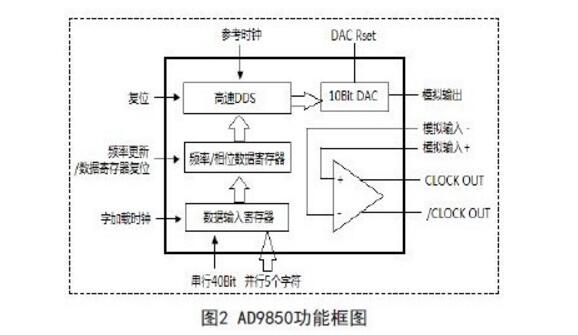

AD9850是AD公司生產的最高時鐘為125 MHz、采用先進的CMOS技術的直接頻率合成器。本文主要介紹了AD9850芯片的原理與工作方式以及關于它的設計。

2018-04-13 15:00:18 46847

46847

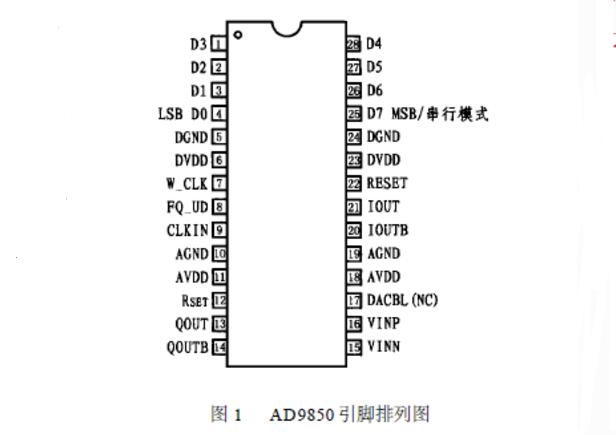

本文開始介紹了AD9850內部結構與AD9850的工作原理,其次介紹了AD9850引腳功能與AD9850的控制字與控制時序,最后介紹了四款AD9850的應用電路。

2018-04-13 14:34:32 40221

40221

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。

2017-11-17 02:00:58 671

671

信號發生器是一種能提供各種頻率、波形和輸出電平電信號的設備。在測量各種電信系統或電信設備的振幅特性、頻率特性、傳輸特性及其它電參數時,以及測量元器件的特性與參數時,用作測試的信號源或激勵源。

2017-11-05 10:49:37 6532

6532

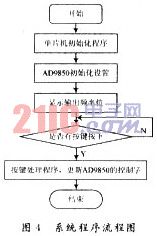

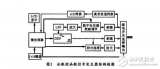

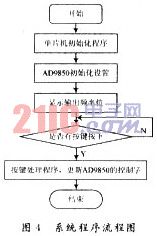

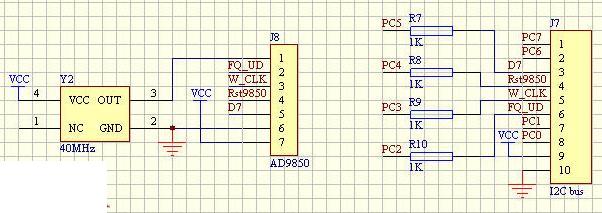

論文設計開發了基于 AD9850 構成的 DDS 正弦波信號發生器的硬件系統,其頻率范圍為 0~30MHz,根據軟件設計的總體構想并結合硬件電路,給出了總體以及子模塊的流程圖,并用 C 語言編制相應

2017-11-04 09:50:53 20

20 Silicon Labs(亦稱“芯科科技”)最新發布的Si538x 系列無線時鐘發生器利用我們的最新第四代

2017-10-17 09:36:30 6830

6830 10GHz擴頻時鐘發生器的設計_胡帥帥

2017-01-07 21:28:58 1

1 一種占空比可調的兩相非重疊時鐘發生器_張學敏

2017-01-05 15:06:09 5

5 本系統采用數字合成芯片AD9850完成整個系統設 計. AD9850內含可編程DDS系統和高速比較器,能實現 全數字編程控制的頻率合成 .可編程DDS系統的核心是相 位累加器,它由一個加法器和一個N

2016-10-25 18:04:42 17

17 AD9850學習資料,有需要的下來看看。

2016-08-09 16:50:33 28

28 雙環路時鐘發生器可清除抖動并提供多個高頻輸出

2016-01-04 17:41:13 17

17 Silicon Laboratories (芯科實驗室有限公司)日前宣布擴展其PCI Express(PCIe)時鐘發生器和時鐘緩沖器產品組合。

2012-02-02 09:31:56 1356

1356 MAX3636是一個高度靈活,高精度鎖相環(PLL)時鐘發生器為下一代網絡設備的要求低抖動時鐘發生器和強大的高速數據傳輸的分布進行了優化。

2011-10-11 11:15:22 1267

1267

德州儀器(TI)日前宣布推出一款具有業界最佳抖動性能的高度集成的時鐘發生器。LMK03806可以幫助設計人員運用一個低成本晶體合成所需的時鐘頻率

2011-10-10 09:19:30 1072

1072 本文主要介紹的是微型的DDS信號發生器的原理和設計,整個系統是以AT89S51為控制,外部ROM為存儲,AD9850芯片和溫度補償晶體振蕩器構成的微型DDS信號發生器,采用DM-162點陣液晶顯示模塊

2011-05-05 15:55:36 121

121 介紹基于直接數字頻率合成器(DDS)AD9850的倍頻器設計,倍頻倍數N可以在限定范圍內自行設置。系統主要模塊CPLD/FPGA、DDS(AD9850)和單片機(80C51)之間可以并行通信,具有編程控制簡

2010-12-11 17:39:15 92

92 在電力系統、CDMA2000、DVB、DMB等系統中,高精度的GPS時鐘發生器(GPS同步時鐘)對維持系統正常運轉有至關重要的意義。

那如何利用GPS OEM來進行二次開發,產生高精度時鐘發生

2010-09-17 22:02:44 1233

1233 如何利用GPS OEM來進行二次開發,產生高精度時鐘發生器是一個研究的熱點問題。在電力系統、CDMA2000、DVB、DMB等系統中,高精度的GPS

2010-07-24 15:45:26 748

748 MAX3679A高性能四路輸出時鐘發生器(Maxim)

Maxim推出用于以太網設備的高性能、四路輸出時鐘發生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 722

722 采用AD9850的信號發生器的設計方案

概述:介紹ADI公司出品的AD9850芯片,給出芯片的引腳圖和功能。并以單片機AT89S52為控制核心設計了一個串行控制

2010-03-24 11:31:57 2385

2385

MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

概述

MAX3625B是一款低抖動、精密時鐘發生器,優化用于網絡設備。器件內置晶體振蕩器和鎖相環(PLL)

2010-03-01 08:56:18 1282

1282

MAX3625B是一款低抖動、精密時鐘發生器,優化用于網絡設備。器件內置晶體振蕩器和鎖相環(PLL)時鐘倍頻器,以產生高頻時鐘輸出,用于以太網、10G光纖通道及其它網絡設備。Ma

2010-03-01 08:54:52 126

126 MAX3624 低抖動、精密時鐘發生器,提供四路輸出

概述

MAX3624是一款低抖動精密

2009-09-18 08:56:41 632

632

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

本文介紹了電源噪聲對基于PLL的時鐘發生器的干擾,并討論了幾種用于評估確定性抖動(DJ)的技術方案。推導出的關系式提

2009-09-18 08:46:32 1424

1424

MAX3625A 低抖動、精密時鐘發生器,提供三路輸出

2009-08-13 13:01:27 805

805

ad9850外圍電路

2009-08-07 21:49:37 2563

2563

ad9850電路

2009-08-07 21:13:35 1149

1149

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-05-03 11:07:05 616

616

本文介紹了74HC4046的工作原理以及采用—74HC4046鎖相環芯片組成的圖象數字化電路中的行鎖相象素時鐘發生器,該發生器的過渡過程快,捕獲時間短,跟蹤精度高,本文給出了實用電路.

2009-04-28 14:05:37 15

15 摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-04-22 10:11:53 392

392

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL內核和三種不同輸出(LVPECL, HSTL,LVDS)的高精度時鐘發生器。MAX945x時鐘發生器具有四個主要的特點:集成VCXO,工作頻率范圍寬,PLL

2009-04-22 09:42:01 913

913

振蕩器時鐘發生器電路圖

2009-04-13 08:54:22 699

699

精密時鐘發生器電路圖

2009-03-25 09:35:22 960

960

Si5338 業界首個任意頻率、任意輸出的時鐘發生器

高性能模擬與混合信號領導廠商Silicon Laboratories日前發表全新的時鐘發生器和緩沖器系列,可為業

2008-11-10 09:39:44 1654

1654 MAX9489/MAX9471多輸出時鐘發生器構建集成時鐘源

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如

2008-10-04 20:43:25 865

865

用ad9850激勵的鎖相環頻率合成器山東省濟南市M0P44 部隊Q04::00R 司朝良摘要! 提出了一種ad9850和ad9850相結合的頻率合成方案! 介紹了ad9850芯片ad9850的基本工作原理" 性能特點及

2008-07-17 22:44:22 4

4

ad9850 應用源程序

2008-04-23 09:18:27 104

104

電子發燒友App

電子發燒友App

評論