LMK1C1104DQF 時(shí)鐘緩沖器 計(jì)時(shí) 評估板

2024-03-14 23:22:15

LMK6 時(shí)鐘發(fā)生器 計(jì)時(shí) 評估板

2024-03-14 23:22:15

時(shí)鐘 時(shí)鐘緩沖器 IC 2:8 2 GHz 40-VFQFN 裸露焊盤

2024-03-14 23:22:01

時(shí)鐘 時(shí)鐘緩沖器 IC 2:8 2 GHz 40-VFQFN 裸露焊盤

2024-03-14 23:22:01

AD9834 波形發(fā)生器 時(shí)鐘定時(shí) mikroBUS? Click? 平臺評估擴(kuò)展板

2024-03-14 23:11:38

CS2200-CP 時(shí)鐘發(fā)生器 時(shí)鐘定時(shí) mikroBUS? Click? 平臺評估擴(kuò)展板

2024-03-14 23:11:37

Si5350,Si5351 時(shí)鐘發(fā)生器 計(jì)時(shí) 評估板

2024-03-14 22:30:46

Si5348 時(shí)鐘發(fā)生器 計(jì)時(shí) 評估板

2024-03-14 22:30:44

Si50122-A5 時(shí)鐘發(fā)生器 計(jì)時(shí) 評估板

2024-03-14 22:30:31

ICS501 時(shí)鐘發(fā)生器 時(shí)鐘定時(shí) mikroBUS? Click? 平臺評估擴(kuò)展板

2024-03-14 22:03:12

Si5351A 時(shí)鐘發(fā)生器 時(shí)鐘定時(shí) STEMMA QT 平臺評估擴(kuò)展板

2024-03-14 20:37:59

電子發(fā)燒友網(wǎng)站提供《CDCE6214超低功率時(shí)鐘發(fā)生器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-02-28 15:38:40 0

0 。時(shí)鐘發(fā)生器芯片廠家可輸出差分100MHz,125MHz,156.25MHz和單端33.33MHz CPU時(shí)鐘,同時(shí)輸出6路25MHz緩沖參考時(shí)鐘。? 主要特性l 7路單

2024-02-04 11:41:14

電子發(fā)燒友網(wǎng)站提供《毫微微時(shí)鐘網(wǎng)絡(luò)同步器、抖動衰減器和時(shí)鐘發(fā)生器RC32112A 數(shù)據(jù)表.pdf》資料免費(fèi)下載

2024-01-31 10:09:17 0

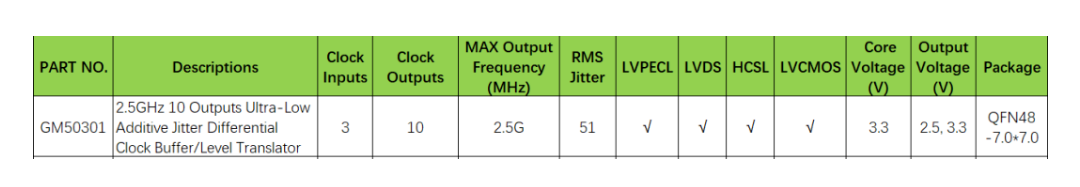

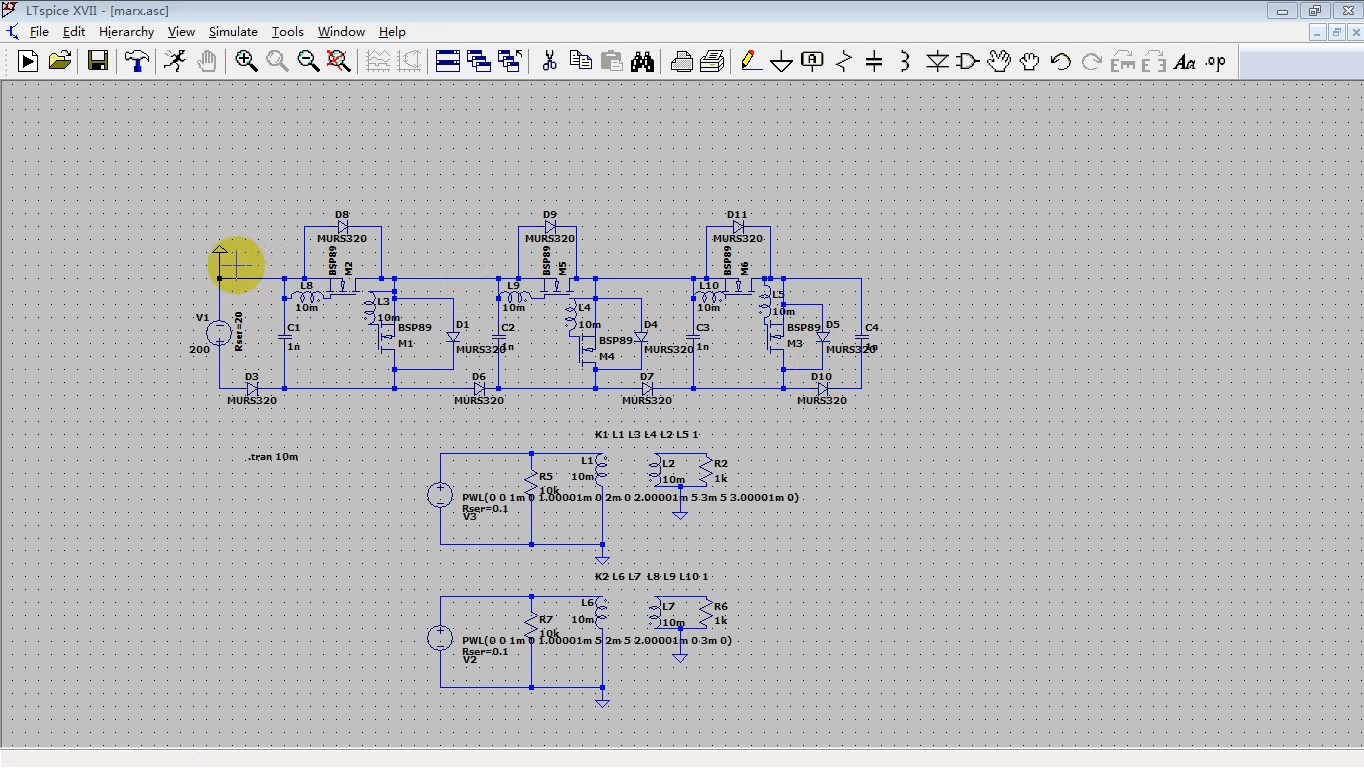

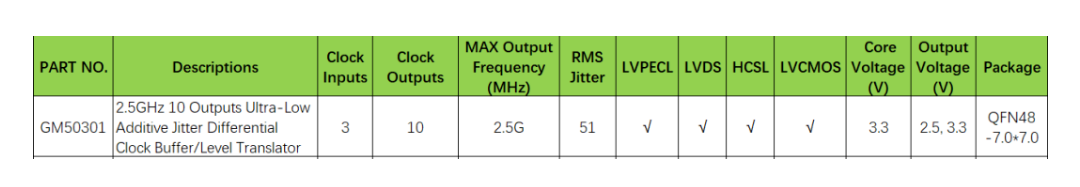

0 時(shí)鐘緩沖器芯片 10路單端buffer是一款高性能、低噪聲的LVCMOS房出緩沖器,此緩沖器可以從單端、差分或晶體輸入中分配出10路超低抖動時(shí)鐘。典型應(yīng)用場景:· RRU基準(zhǔn)分布· SONET

2024-01-26 11:09:00

? ? ? ?RS2CG5705B是一款符合PCI Express 3.0和以太網(wǎng)要求的擴(kuò)頻時(shí)鐘發(fā)生器。該電路用于PC或嵌入式系統(tǒng),以顯著減少電磁干擾(EMI)。RS2CG5705B提供

2024-01-25 09:41:32 0

0 RS2CG5705B是一款符合PCI Express 3.0和以太網(wǎng)要求的擴(kuò)頻時(shí)鐘發(fā)生器。該電路用于PC或嵌入式系統(tǒng),以顯著減少電磁干擾(EMI)。RS2CG5705B提供4對差分(HCSL)或

2024-01-24 17:31:16

波特率發(fā)生器是一種用于控制串行數(shù)據(jù)通信速率的設(shè)備,它可以生成特定波特率的時(shí)鐘信號。在嵌入式系統(tǒng)、通信設(shè)備和計(jì)算機(jī)硬件中,波特率發(fā)生器的使用十分常見。波特率發(fā)生器通常使用定時(shí)器來實(shí)現(xiàn)時(shí)鐘信號的生成

2024-01-24 09:56:20 265

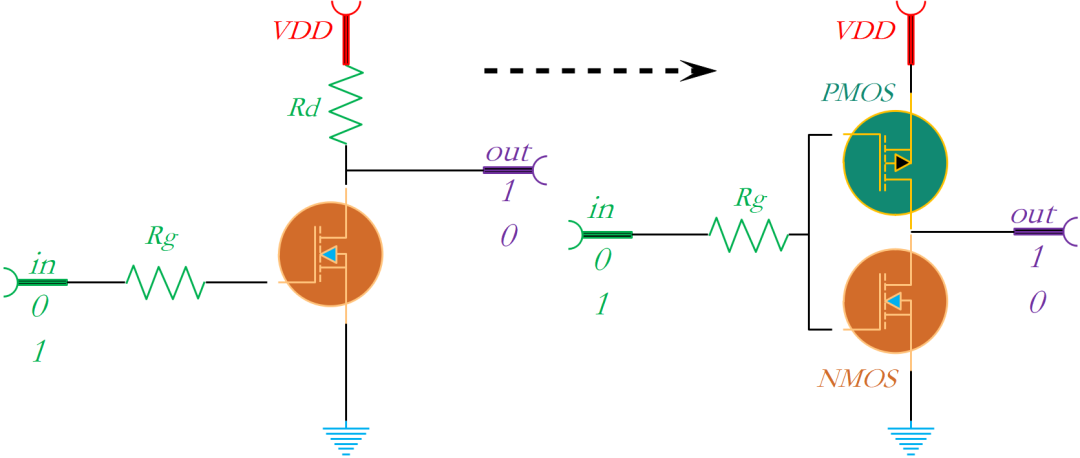

265 組合邏輯產(chǎn)生的時(shí)鐘可能有毛刺,會被錯誤地當(dāng)成有效時(shí)鐘邊沿,在設(shè)計(jì)中會導(dǎo)致功能錯誤。因此,不要使用組合邏輯的輸出作為時(shí)鐘。

2024-01-22 09:30:50 168

168

核芯互聯(lián)近日發(fā)布了一款專為高性能服務(wù)器和計(jì)算中心應(yīng)用打造的支持PCIe 6.0的高性能時(shí)鐘發(fā)生器——CLG440。這款產(chǎn)品符合CK440Q標(biāo)準(zhǔn),旨在滿足下一代服務(wù)器和數(shù)據(jù)中心的需求。

2024-01-16 16:09:07 445

445 “核芯互聯(lián)CLG440是一顆專為高性能服務(wù)器、計(jì)算中心應(yīng)用推出的支持PCIe 6.0、符合CK440Q標(biāo)準(zhǔn)的高性能時(shí)鐘發(fā)生器。

2024-01-16 15:57:40 279

279

節(jié)點(diǎn)上的時(shí)鐘與參考時(shí)鐘保持同步,從而保證系統(tǒng)的穩(wěn)定性和準(zhǔn)確性。 當(dāng)涉及到分布式系統(tǒng)時(shí),每個(gè)節(jié)點(diǎn)都有自己的本地時(shí)鐘,它們依賴于硬件的時(shí)鐘發(fā)生器。然而,由于硬件的制造差異、溫度變化等原因,每個(gè)節(jié)點(diǎn)的時(shí)鐘可能會走

2024-01-16 14:37:23 188

188 電子發(fā)燒友網(wǎng)站提供《FemtoClock2抖動衰減器和時(shí)鐘發(fā)生器RC325008A數(shù)據(jù)手冊.pdf》資料免費(fèi)下載

2024-01-14 10:55:06 0

0 生成時(shí)鐘包括自動生成時(shí)鐘(又稱為自動衍生時(shí)鐘)和用戶生成時(shí)鐘。自動生成時(shí)鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時(shí)鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 396

396

PCIe授時(shí)卡時(shí)鐘板卡支持多種參考輸入和輸出,可根據(jù)需求采用不同的組合為計(jì)算機(jī)系統(tǒng)提供高精度時(shí)間信息,同時(shí)也可對外授時(shí)。支持GPS/北斗、PTP輸入、B碼(DC)作為參考源,輸出10M、B(DC)碼

2024-01-09 13:28:11

。時(shí)鐘發(fā)生器芯片廠家可輸出差分100MHz,125MHz,156.25MHz和單端33.33MHz CPU時(shí)鐘,同時(shí)輸出6路25MHz緩沖參考時(shí)鐘。? 主要特性l 7路單

2023-12-29 09:29:50

時(shí)鐘緩沖器芯片時(shí)鐘芯片是一種基于PLL的時(shí)鐘發(fā)生器,采用ADPLL(全數(shù)字鎖相環(huán))技術(shù),以實(shí)現(xiàn)的高頻低相噪性能,并具備低功耗和高PSNR能力,可實(shí)現(xiàn)小于0.3ps RMS的相位抖動性能。可輸出差分

2023-12-28 13:46:09

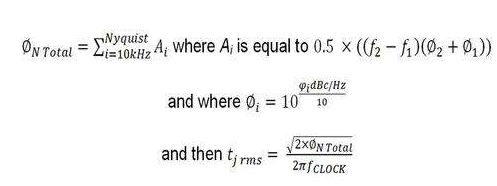

100fs-300fs之間?

疑問3:是不是使用PLL類型的時(shí)鐘發(fā)生器芯片帶來的抖動誤差會比較大?針對14位的ADC輸入差分時(shí)鐘有此類型的參考嗎?

模擬輸入部分:

疑問1:參考文檔中使用AD8138差分驅(qū)動芯片

2023-12-22 08:19:31

電子發(fā)燒友網(wǎng)站提供《551S低傾斜1到4時(shí)鐘緩沖器數(shù)據(jù)表.pdf》資料免費(fèi)下載

2023-12-21 10:41:18 0

0 電子發(fā)燒友網(wǎng)站提供《低傾斜1到4時(shí)鐘緩沖器524S數(shù)據(jù)表.pdf》資料免費(fèi)下載

2023-12-21 10:37:32 0

0 高性能20路PCIe時(shí)鐘緩沖器新品推介SQ82100PCI-Express(PCIe)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),主要用于擴(kuò)充計(jì)算機(jī)系統(tǒng)總線數(shù)據(jù)吞吐量以及提高設(shè)備通信速度。目前服務(wù)器

2023-12-20 08:19:38 240

240

AC1571 是用于 5G 基站應(yīng)用的基于 PLL的時(shí)鐘發(fā)生器,該芯片采用全數(shù)字鎖相環(huán)技術(shù),以實(shí)現(xiàn)最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應(yīng)用場景:· 無線基站·

2023-12-12 14:25:17

單端模式下,AD7328模擬輸入端是不是必須加緩沖器,緩沖器選什么型號

2023-12-06 06:52:14

依據(jù)數(shù)據(jù)手冊表示,外加Rsense可最大達(dá)到+80mA的電流范圍,若需80+以上需加緩沖器。

請問使用緩沖器后最大的安電流可達(dá)到多少?電流過大是否需要衰減后再流入AD5522?

2023-12-04 07:24:23

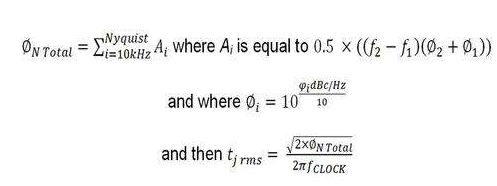

的時(shí)鐘發(fā)生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時(shí)鐘發(fā)生器。然而,如果不慎重考慮時(shí)鐘發(fā)生器、相位噪聲和抖動性能,數(shù)據(jù)轉(zhuǎn)換器、動態(tài)范圍和線性度性能可能受到嚴(yán)重的影響。...

2023-11-28 14:33:57 0

0 電子發(fā)燒友網(wǎng)站提供《ADI電源管理產(chǎn)品組合.pdf》資料免費(fèi)下載

2023-11-24 11:48:45 0

0 我想在一項(xiàng)應(yīng)用中使用ad8221 ad8221,目的是放大接收自2個(gè)電極的不同電位。為消除高頻噪聲,我在儀表放大器輸入前使用了一個(gè)RC濾波器,您認(rèn)為在濾波器和放大器輸入之間使用一個(gè)電壓緩沖器是否會更好。在此情況下,您建議使用哪種模擬器件IC作為電壓緩沖器。

2023-11-24 07:19:57

Silicon Labs(亦稱“芯科科技”)宣布推出新的BB5 8位微控制器(MCU)系列產(chǎn)品,該系列MCU針對價(jià)格和性能進(jìn)行了優(yōu)化,進(jìn)一步擴(kuò)展了芯科科技強(qiáng)大的MCU開發(fā)平臺。

2023-11-17 09:50:51 369

369 Synopsys, Inc.11月8日宣布擴(kuò)展其 ARC處理器 IP 產(chǎn)品組合,納入新的RISC-V ARC-V 處理器 IP,使客戶能夠從各種靈活、可擴(kuò)展的處理器選項(xiàng)中進(jìn)行選擇

2023-11-09 12:41:33 468

468 時(shí)鐘合成器和時(shí)鐘發(fā)生器是兩種用于產(chǎn)生時(shí)鐘信號的電子器件,它們在功能和應(yīng)用上有一些區(qū)別。

2023-11-09 10:26:56 298

298 Silicon Labs無線接收器Si4355可以同時(shí)支持傳輸速率為2.4/9.6Kbps的數(shù)據(jù)嗎?

2023-10-28 08:25:24

Silicon Labs時(shí)鐘芯片Si5332如何更改時(shí)鐘輸出頻率??

2023-10-28 07:28:03

方法來使不同步的時(shí)鐘信號同步。下面我們就來詳細(xì)講解這些方法。 1. 時(shí)鐘緩沖器同步法 時(shí)鐘緩沖器同步法是指通過一個(gè)時(shí)鐘緩沖器來同步兩個(gè)不同步的時(shí)鐘信號。其原理是將一個(gè)時(shí)鐘信號通過一個(gè)緩沖器反轉(zhuǎn),產(chǎn)生一個(gè)相反的信號,

2023-10-18 15:23:48 771

771 SI5338Q-B-GM,SILICON/芯科,I2C可編程任意頻率、任意輸出 四路時(shí)鐘發(fā)生器SI5338Q-B-GM,SILICON/芯科,I2C可編程任意頻率、任意輸出 四路時(shí)鐘發(fā)生器

2023-10-17 17:02:33

僅當(dāng)存在待發(fā)送數(shù)據(jù)時(shí)串行時(shí)鐘波特發(fā)生器才產(chǎn)生對應(yīng)數(shù)據(jù)位模式的時(shí)鐘脈沖嗎?如果緩沖區(qū)沒數(shù)據(jù),串行時(shí)鐘就一直空閑嗎?

2023-10-17 08:20:06

使用環(huán)形緩沖器的目的是什么

2023-10-15 07:16:39

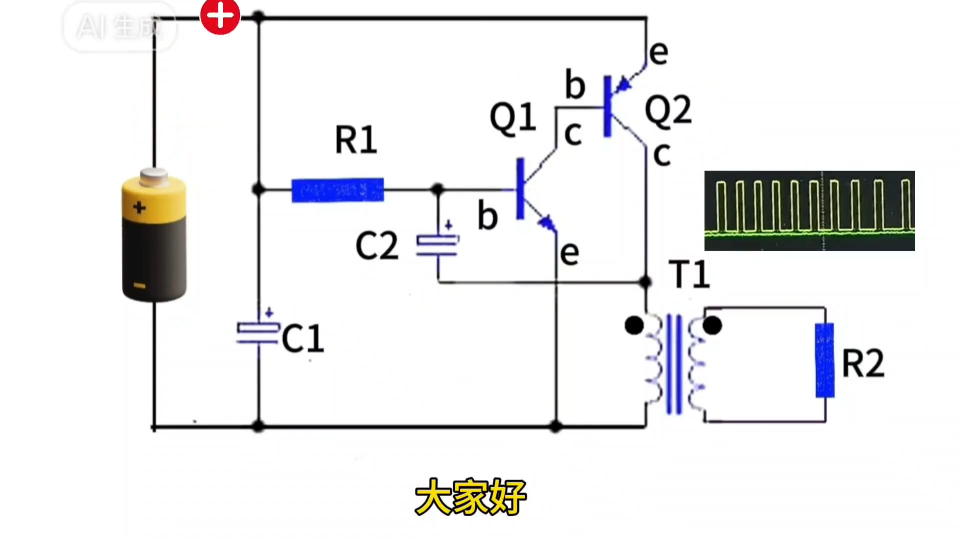

時(shí)鐘發(fā)生器由哪些部分組成?鎖相環(huán)pll的特點(diǎn)是什么?如何用硬件配置pll? 時(shí)鐘發(fā)生器是指通過特定的電路設(shè)計(jì)產(chǎn)生適合各種電子設(shè)備使用的時(shí)鐘信號的器件。時(shí)鐘發(fā)生器由多個(gè)部分組成,其中最核心的是鎖相環(huán)

2023-10-13 17:39:50 443

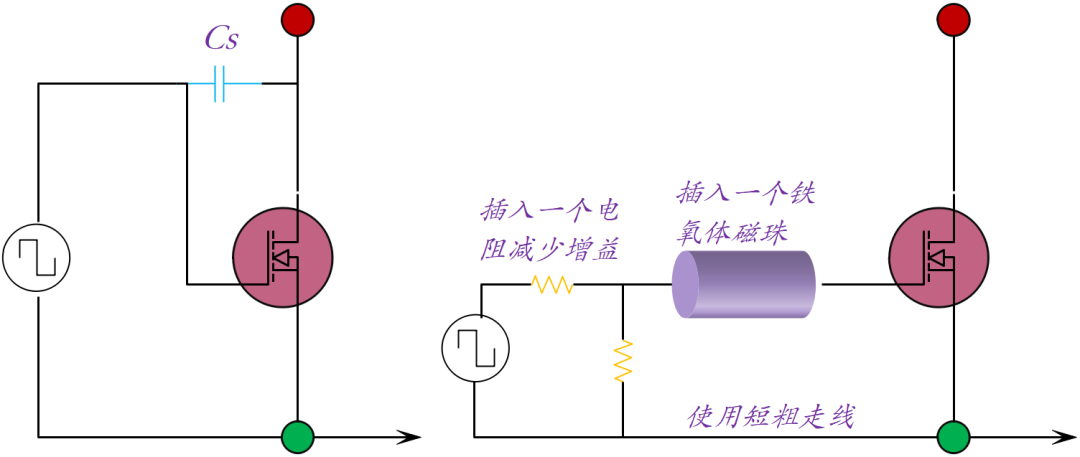

443 引言:一位朋友要求更一期Snubber的詳細(xì)介紹,這個(gè)拖更好久了,今天就補(bǔ)上!切斷電路中的電流時(shí),電路中的雜散電感會導(dǎo)致電壓急劇增加,緩沖器電路提供保護(hù),以抑制這個(gè)浪涌電壓,吸納在關(guān)閉時(shí)發(fā)生

2023-09-26 15:53:07 616

616

三態(tài)輸出的緩沖器有哪些用途? 三態(tài)輸出緩沖器是一種電子元件,其主要作用是將一個(gè)輸入信號轉(zhuǎn)換成一個(gè)可以控制多個(gè)輸出設(shè)備的信號。這種緩沖器可以被用于一系列的應(yīng)用,包括數(shù)碼電路、計(jì)算機(jī)、消費(fèi)電子設(shè)備、通信

2023-09-21 15:55:36 1599

1599 時(shí)鐘發(fā)生器IC 200MHz 2 MSOP10_3X3MM

2023-09-18 15:10:50

引言:在異步邏輯器件中,信號不與時(shí)鐘信號同步,或者說該信號壓根就沒有對位的時(shí)鐘信號。本節(jié)簡述基本的異步邏輯--->1位拓?fù)浜投辔煌負(fù)涞?b class="flag-6" style="color: red">緩沖器、反相器、驅(qū)動器和收發(fā)器。

2023-09-04 15:59:03 1596

1596

Silicon Labs的全球授權(quán)代理商。自2006年起,貿(mào)澤與Silicon Labs攜手合作,支持全球貿(mào)澤客戶在物聯(lián)網(wǎng) (IoT)、照明和AI/ML應(yīng)用領(lǐng)域的產(chǎn)品開發(fā)流程。 貿(mào)澤是專注于引入新品的全球半導(dǎo)體

2023-08-31 15:21:21 256

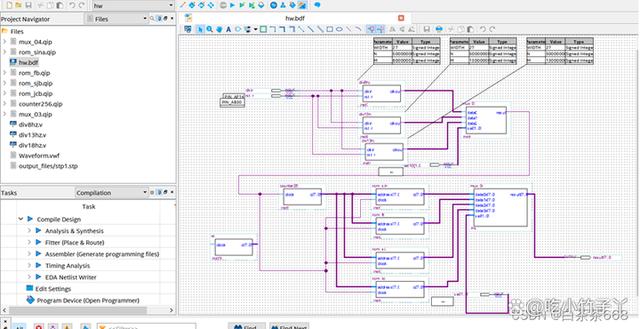

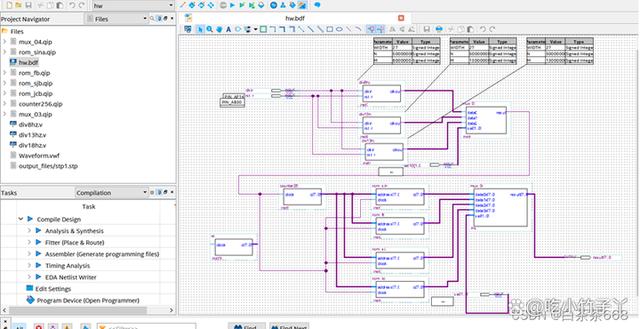

256 多功能信號發(fā)生器的原理框圖如圖所示。其中,CLKGEN是分頻器,提供的50MHz的主頻率進(jìn)行分頻,以得到滿足多功能信號發(fā)生器設(shè)計(jì)需要的時(shí)鐘頻率。

2023-08-25 16:34:51 1291

1291

電子發(fā)燒友網(wǎng)站提供《PI6CDBL401B低功耗PCIe時(shí)鐘芯片.pdf》資料免費(fèi)下載

2023-07-25 14:41:49 0

0 9ZXL1951D PCIe 時(shí)鐘發(fā)生器評估板用戶指南

2023-07-07 19:19:11 0

0 在本例中,我們將研究如何利用低抖動時(shí)鐘發(fā)生器AD9643對雙通道14位250 MSPS ADC進(jìn)行計(jì)時(shí)。使用這些特定產(chǎn)品的常見時(shí)鐘頻率為9523.245 MHz,因此我們將為AD76使用30.72 MHz基準(zhǔn)電壓源(外部振蕩器),并設(shè)置內(nèi)部寄存器,為AD9523生成低抖動時(shí)鐘輸出。

2023-06-30 16:59:52 798

798

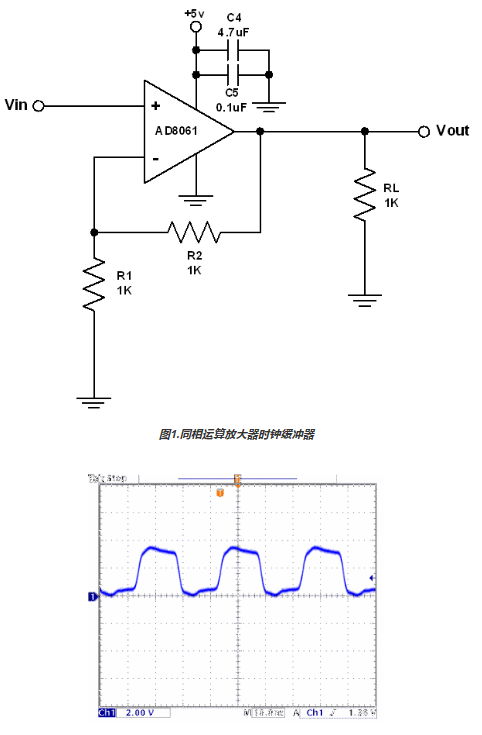

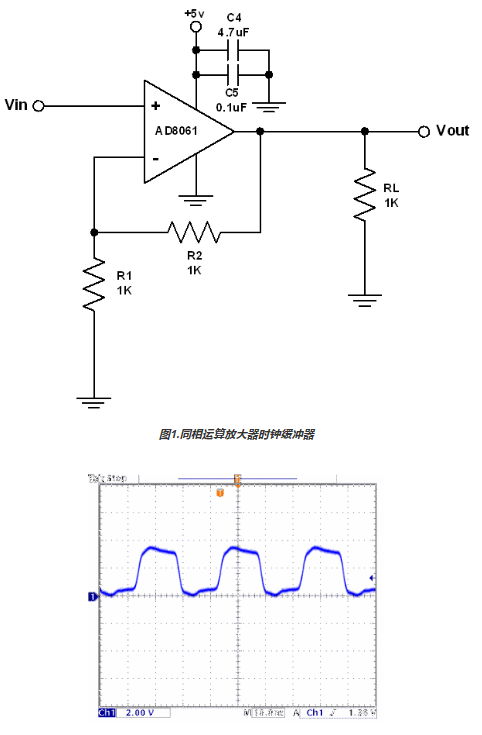

在消費(fèi)電子應(yīng)用中,與典型的時(shí)鐘緩沖應(yīng)用相比,其頻率往往較低,要求也更低,廉價(jià)的高速運(yùn)算放大器(~100 MHz帶寬)可以為傳統(tǒng)時(shí)鐘緩沖器提供有吸引力的替代方案。高速放大器可能比傳統(tǒng)時(shí)鐘緩沖器便宜,但它們可以適應(yīng)各種設(shè)計(jì)配置。

2023-06-17 17:29:14 704

704

高性能的時(shí)鐘器件是高帶寬、高速率、高算力、大模型的基礎(chǔ)。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應(yīng)用的超低抖動全新20路LP-HCSL差分時(shí)鐘緩沖器CLB2000,其業(yè)界領(lǐng)先的附加抖動性能遠(yuǎn)超PCIe Gen 5和PCIe Gen 6的標(biāo)準(zhǔn)。

2023-06-08 15:30:21 526

526

高性能的時(shí)鐘器件是高帶寬、高速率、高算力、大模型的基礎(chǔ)。核芯互聯(lián)近日推出面向下一代數(shù)據(jù)中心應(yīng)用的超低抖動全新20路LP-HCSL差分時(shí)鐘緩沖器CLB2000,其業(yè)界領(lǐng)先的附加抖動性能遠(yuǎn)超PCIe Gen 5和PCIe Gen 6的標(biāo)準(zhǔn)。

2023-06-08 15:29:55 805

805

HMC7043是一種高性能時(shí)鐘緩沖器,用于為具有并行或串行(JESD204B型)接口的高速數(shù)據(jù)轉(zhuǎn)換器分配超低相位噪聲參考。

2023-05-31 10:47:57 1636

1636 參考時(shí)鐘獨(dú)立,參考時(shí)鐘不需要穿越背板和連接器,從而使PCB設(shè)計(jì)變得更為簡單,使得架構(gòu)更加的靈活。

2023-05-29 12:49:49 5074

5074

Nexperia | 擴(kuò)展用于汽車以太網(wǎng)的 ESD 保護(hù)解決方案產(chǎn)品組合 Nexperia(安世半導(dǎo)體)宣布擴(kuò)展其備受贊譽(yù)的汽車以太網(wǎng) ESD 保護(hù)器件產(chǎn)品組合。 近日,基礎(chǔ)半導(dǎo)體器件領(lǐng)域的專家

2023-05-29 10:33:19 363

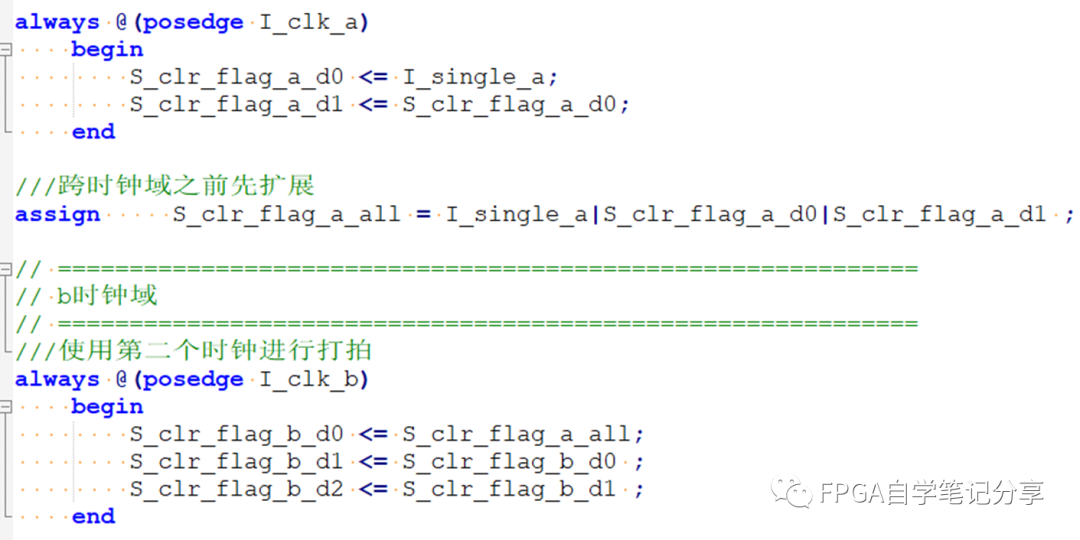

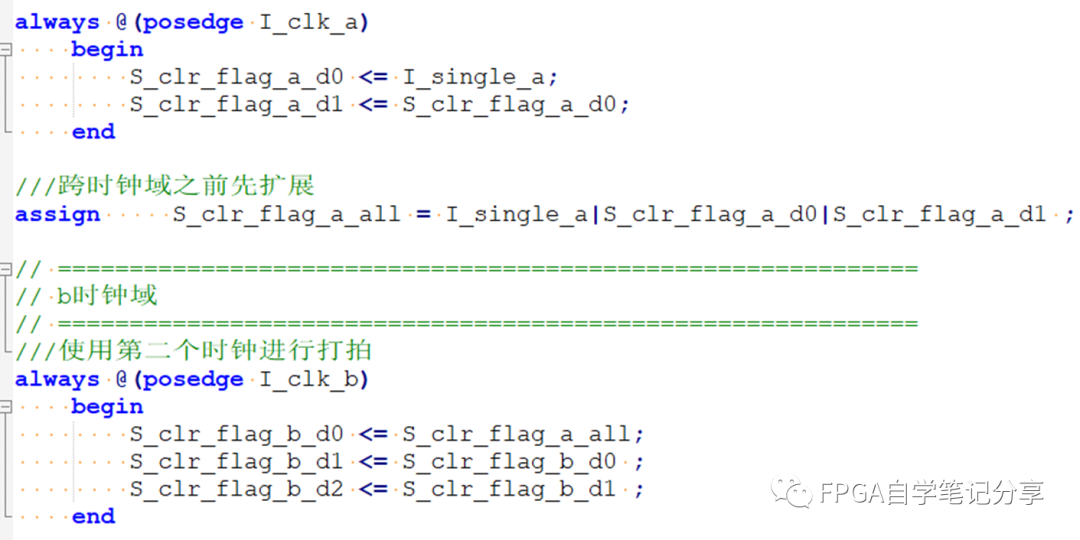

363 中的S_clr_flag_a_all信號,就是在擴(kuò)展時(shí)不小心使用了組合邏輯,這種情況下由于競爭冒險(xiǎn),會導(dǎo)致跨時(shí)鐘域后的b信號出現(xiàn)一個(gè)clk的異常電平。

2023-05-24 15:11:32 670

670

我使用 I2S 接口制作了一個(gè)簡單的時(shí)鐘/脈沖發(fā)生器用于測試目的。

一個(gè)庫創(chuàng)建了一組循環(huán)的緩沖區(qū),這些緩沖區(qū)不斷地被 DMA 輸出。

緩沖器被填滿并選擇時(shí)鐘分頻器以提供范圍從 2Hz 到 20MHz

2023-05-22 07:34:51

。作為一家專注于物聯(lián)網(wǎng)的企業(yè),Silicon Labs在不斷為業(yè)界提供多種無線產(chǎn)品組合的同時(shí),也十分注重與開發(fā)

2023-05-08 17:58:25 404

404 基礎(chǔ)半導(dǎo)體器件領(lǐng)域的高產(chǎn)能生產(chǎn)專家 Nexperia(安世半導(dǎo)體)近日宣布推出全新 16 通道 I2C 通用輸入輸出(GPIO)擴(kuò)展器產(chǎn)品組合,旨在提高電子系統(tǒng)的靈活性和重復(fù)利用能力。其中

2023-05-04 17:34:04 898

898

器產(chǎn)品組合,旨在提高電子系統(tǒng)的靈活性和重復(fù)利用能力。其中一款GPIO擴(kuò)展器NCA9595采用可通過寄存器配置的內(nèi)部上拉電阻,可根據(jù)實(shí)際需要自定義以優(yōu)化功耗。當(dāng)需要擴(kuò)展I/O數(shù)量時(shí),利用該產(chǎn)品組合可實(shí)現(xiàn)簡潔的設(shè)計(jì),同時(shí)盡可能減少互連。這有助于設(shè)計(jì)工程師增添新功能,而且不會增加

2023-04-28 10:37:19 612

612

液壓緩沖器強(qiáng)度是否能夠調(diào)節(jié),取決于液壓緩沖器的種類,目前市面上較為常用的液壓緩沖器包括可調(diào)液壓緩沖器、不可調(diào)液壓緩沖器,這兩種緩沖器調(diào)節(jié)強(qiáng)度的實(shí)際效果是不一樣的。

2023-04-24 16:12:01 2147

2147 CLG5908是一顆高性能的任意頻率任意輸出格式通用時(shí)鐘發(fā)生器,可以支持1~750M任意頻點(diǎn)輸出,頻率精度 < 0.001 PPM,并且jitter性能優(yōu)越,通常模式下RMS jitter<200fs,同時(shí)支持Down-Spread和Center-Spread SSC。

2023-04-23 14:43:12 626

626

) 頻帶內(nèi)和頻帶外 (VCO) 噪聲的影響。基準(zhǔn)時(shí)鐘發(fā)生器的相位噪聲性能需要在PLL環(huán)路帶寬內(nèi)和帶寬外都表現(xiàn)得很出色,以符合更加嚴(yán)格的抖動技術(shù)規(guī)格要求。

2023-04-17 10:37:30 357

357

本文討論電源噪聲干擾對基于PLL的時(shí)鐘發(fā)生器的影響,并介紹幾種用于評估由此產(chǎn)生的確定性抖動(DJ)的測量技術(shù)。派生關(guān)系顯示了如何使用頻域雜散測量來評估時(shí)序抖動行為。實(shí)驗(yàn)室臺架測試結(jié)果用于比較測量技術(shù),并演示如何可靠地評估參考時(shí)鐘發(fā)生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 810

810

在時(shí)鐘芯片方向,有容微電子基于優(yōu)秀的時(shí)鐘芯片團(tuán)隊(duì)、卓越的時(shí)鐘芯片技術(shù),著眼于滿足不同客戶、不同應(yīng)用的差異化需求,致力于向廣大客戶提供具有完全自主知識產(chǎn)權(quán)的國產(chǎn)化時(shí)鐘解決方案。

2023-04-07 15:08:00 930

930

時(shí)鐘發(fā)生器/PLL頻率合成器 VQFN32_5X5MM_EP 3V~3.6V 683.28MHz

2023-04-06 12:10:37

會退出總線繁忙狀態(tài)和失敗。 出于好奇,我嘗試將時(shí)鐘頻率配置為 400MHz 并使用分頻器 2 來獲得 200M 的值。 我想知道 RFDR 中的這個(gè)值表示什么以及誰負(fù)責(zé)更新? 如果我使用分頻器值 3,則操作成功,RFDR[0] 值為 0x80,依此類推各種循環(huán)序列的變化。

2023-04-03 09:01:11

利用運(yùn)算放大器構(gòu)成的脈沖序列發(fā)生器和積分器構(gòu)成三角波發(fā)生器。可是我怎么將匹配器件的參數(shù),調(diào)出三角波的波形呢。現(xiàn)在怎么調(diào)都 沒法弄在線性工作區(qū)。。。。

2023-03-31 13:53:44

”和“Peripheral clock”來生成相關(guān)的硬件配置。原始生成的配置設(shè)置將出現(xiàn)“HardFault_Handler”。我發(fā)現(xiàn)所有的 PORTA_CLK ~ PORTE_CLK 好像都沒有時(shí)鐘。因此

2023-03-30 08:23:23

12 LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器,集成2 GHz VCO

2023-03-28 18:26:07

CDCLVC1102 低抖動 1:2 LVCMOS 扇出時(shí)鐘緩沖器

2023-03-28 18:26:07

CDCM61002 1:2 超低抖動晶體時(shí)鐘發(fā)生器

2023-03-28 18:26:06

時(shí)鐘發(fā)生器/PLL頻率合成器 QFN24_4X4MM_EP 3~5.2V 8GHz

2023-03-28 18:26:06

14輸出時(shí)鐘發(fā)生器,集成2.0 GHz VCO

2023-03-28 18:12:38

2.5 V/3.3 V, 4個(gè)LVPECL輸出,SiGe時(shí)鐘扇出緩沖器

2023-03-28 15:01:21

時(shí)鐘發(fā)生器 MSOP10 3~3.6V

2023-03-28 12:54:08

帶LDO的四正弦波時(shí)鐘緩沖器

2023-03-23 05:01:44

結(jié)合時(shí)鐘發(fā)生器輸出和FTDICHIP-ID TM安全加密狗

2023-03-23 04:59:11

電子發(fā)燒友App

電子發(fā)燒友App

評論