每當我去買一個新的大件裝置時,我總是權衡我的選擇。有時我讓這讓我癱瘓,最后做出一個我后來后悔的消費決定。但在決定如何在下一個PCB中布線信號時,不一定要這樣。

當你的PCB上有許多元件和互連時,你需要權衡你的選擇。密集布線既是科學又是技術,在您的選項上盡可能多地提供信息將有助于確保您為下一個電路板實施最佳布線策略。

跡線和元件密度

隨著跡線密度和元件密度的增加,電路板周圍的布線跡線變得越來越復雜。只要您沒有在高引腳數器件之間布線并且組件之間有足夠的空間,您的電路板就可能完全在單層上布線。即使在使用中等到高速電路時,仍然可以在一層上布線所有內容。

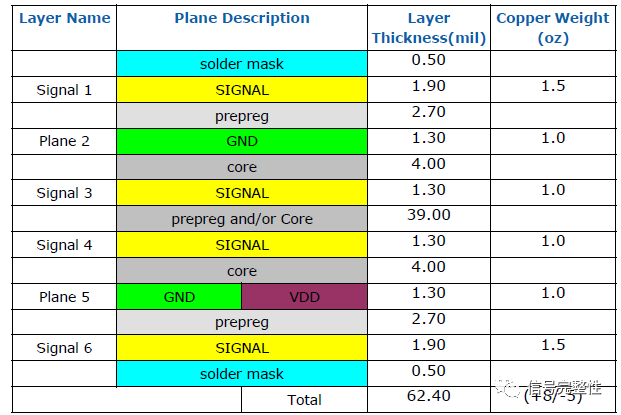

隨著跡線密度和元件密度的增加,單層布線變得更加困難甚至在數學上都不可能,你必須繼續多層設計。必須在內層上路由信號,并且可以使用過孔訪問內層。在某些器件中,特別是在HDI設計中,這是繼續將更多互連和元件封裝到單個PCB中而不增加其尺寸的唯一方法。

由于使用過孔是訪問內層的唯一方法多層電路板,這就引出了一個問題:何時應該使用過孔來建立更短的連接,而不是在信號層中布設更長的走線?

具有長度匹配差分對的PCB

注意您的頻譜

過孔是非常有用,因為它們可以極大地簡化其他組件的布線,或者當電路板上存在高密度的互連時。具有BGA封裝的FPGA等組件通常使用過孔進行轉義路由。所有過孔都有一些電容和電感,就像PCB走線一樣。這通常在很寬的頻率和開關速度范圍內被忽略,因為與通路的其余部分相比,通孔的長度通常非常小。

所有數字信號的功率集中在高于開關頻率。與高頻模擬信號相比,即使是中等速度的數字信號,由于更高頻率的功率譜,在通過過孔時也會產生信號完整性問題。通孔的小幾何形狀使它們具有高的基本共振頻率(100到MHz到GHz)。通孔中的諧振會導致高頻(> 100 MHz)模擬或中等到高速數字信號的EMI問題。

顯然,當路由高速/高電平時,最簡單的方法是避免過孔中的信號完整性問題 - 頻率信號是為了避免在關鍵互連上使用過孔。至少,應盡可能在這些設備中最小化通過過孔的布線。選擇更長的走線可能是更好的選擇,但隨著走線長度的增加,請注意轉換到傳輸線的行為。

在許多現代PCB中,過孔的使用將是不可避免的。在低速或低頻設備中,使用過孔使路由更容易更容易接受。數字信號中的頻譜和這些設備中的模擬信號頻率太低而不會引起諧振和隨后的EMI問題。延長這些器件中的走線長度也是合適的,因為較長的長度不太可能導致轉換為傳輸線行為。

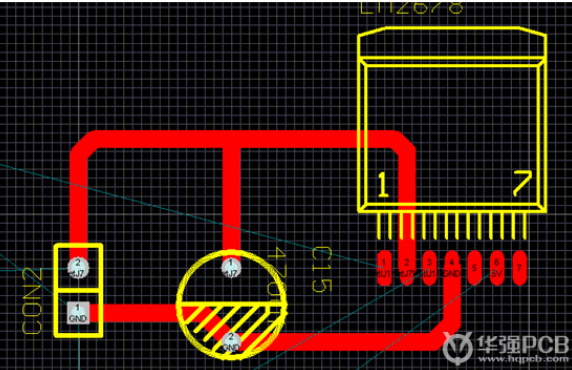

使用差分對

差分對需要精確的長度匹配以保持信號定時。它們還需要精確的間距和對稱性,以便完全抑制串擾。差分對可以擴展而不是通過過孔路由,但是如果對沒有精確匹配的長度,你需要注意可能累積的偏斜。

確保差分信號正確定時

如果您正在嘗試決定是否延長差分對的長度或使用過孔作為快捷方式,您應該將您的設計選擇應用于整個信號網。差分對中的兩條跡線必須長度匹配,以便最大限度地抑制串擾并消除偏斜。如果整個網絡不是長度匹配的,則偏移將在擴展差分對中累積。

因此,如果必須通過過孔路由,則可以考慮通過過孔路由網絡中的每個差分對,因為這可以幫助確保信號網絡的長度匹配。差分對的兩端應通過過孔布線以確保對稱性,從而抑制EMI。您還可以通過其他過孔路由一些互連,有些互連通過表面層,但是您應該始終確保保持長度匹配以減少偏斜。

如果必須增加差分對的長度為了避免過孔引起的信號完整性問題,需要放置所需的互連,注意過渡到傳輸線的行為,尤其是高速/高頻信號。一旦跡線長度超過臨界長度,跡線開始表現為傳輸線,必須終止以避免進一步的信號完整性問題。

-

pcb

+關注

關注

4324文章

23156瀏覽量

399227 -

電路設計

+關注

關注

6678文章

2462瀏覽量

205088

發布評論請先 登錄

相關推薦

PCB設計中布線的要點總結

pcb設計中如何密集布線

pcb設計中如何密集布線

評論