賽靈思宣布推出業界領先的高級設計工具 System Generator for DSP 2015.3 版,該工具可讓系統工程師運用賽靈思 All Programmable 器件設計高性能的 DSP 系統。借助新的 System Generator,算法開發人員可在其熟悉的 MATLAB 和 Simulink 模型化設計環境中創建生產質量級的 DSP 實現方案,而且相校傳統 RTL 可大幅縮短設計時間。最新版提供了更高級的設計抽象,并可通過新型的模塊集中、更快的仿真和編譯運行時間,將無線電算法的設計生產力提高 7 倍。

更 高級的設計抽象

新版 System Generator 配合 Vivado Design Suite, 可讓系統設計人員不通過 HDL Coder 與 System Generator 模塊層級之間的互操作性實現更高級的設計抽象,這種方法能提供高級目標優化代碼的靈活組合,從而達到最佳實現結果。全新流程能在 System Generator 中提供可復用的數據路徑實現方案,能方便地連接到包含 JESD204 和 CPRI 接口以及無線電 IP(如峰值因數抑制)的 SoC 平臺。

“MathWorks 將繼續擴展代碼生成、驗證和平臺支持功能,充分滿足賽靈思 FPGA 和 All Programmable SoC 的無線電算法需求。增強型 System Generator 能配合 HDL Coder 使用,實現快速原型設計,其生成的量產級 IP 能用于 Vivado IP Integrator,并用 Simulink 仿真高級行為算法和優化的 IP,從而大幅縮短我們共同客戶的產品上市時間。”

——Jim Tung,MathWorks公司研究員 增 強型模塊集將驗證編譯速度提升 7 倍

System Generator 數字上下變頻 (DUC/DDC)模塊集的易用性大幅提升,使得更加便于無線算法開發。這些新型模塊還添加了有助于加速驗證和編譯運行時間的增強功能,所有這些模塊提供了七八種參數設置。FIR 數字濾波器模塊與 MathWorks 的濾波器設計分析工具緊密集成在一起,可打造出面積優化的濾波器,包括定點分數插值濾波器或抽取濾波器。正弦波和復數乘積模塊能大幅簡化用于高采樣頻率下頻率轉換的調制解調器的設計。再量化模塊支持數據類型的快速操作,能在數據路徑任何節點上實現動態范圍的最大化。

加 速設計探索和迭代設計收斂

開發人員能用 System Generator 波形觀測儀方便地交叉探測多個時鐘域上的模塊。最新交互式交叉探測技術不僅能加速設計探索,而且還可支持迭代設計收斂。利用時序分析交叉探測技術,算法開發人員能快速識別關鍵路徑并找出影響算法吞吐量和時延的瓶頸問題,從而快速做出調整。該新版本還有一個新的提升之處,那就是 System Generator 基于硬件的協同仿真功能,可將驗證和運行時間縮短 45 倍。

供貨情況 System Generator for DSP 2015.3 版本 現已開始供貨,其不僅支持賽靈思 7 系列和 UltraScale 器件,而且還可提供對 UltraScale+ FPGA 和 MPSoC 的早期試用支持。歡迎登錄:china.xilinx.com/download,下載 System Generator 和 Vivado Design Suite 2015.3。歡迎觀看System Generator快速入門視頻,您也可報名參加培訓,充分利用 UltraFast 設計方法來立即提升您的生產力。

-

濾波器

+關注

關注

161文章

7927瀏覽量

179631 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131743 -

高級設計

+關注

關注

0文章

2瀏覽量

6730

發布評論請先 登錄

相關推薦

VirtualLab Fusion應用:光導布局設計工具

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

易靈思FPGA產品的主要特點

安森美系統設計工具介紹

賽思快訊 | 發展新質生產力問道賽思?賽思如何下好“創新棋”?

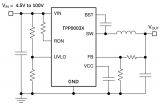

思瑞浦正式宣布推出全新高壓Buck—TPP0003X系列產品

賽靈思宣布推出高級設計工具 System Generator for DSP 2015.3版

賽靈思宣布推出高級設計工具 System Generator for DSP 2015.3版

評論