我是MCU的長期用戶和狂熱者,特別是對多功能低成本MCU上有著濃厚的興趣,這種MCU模塊能夠通過單芯片實現優秀的通信能力。我做過很多有意思的小玩意,包括:MP3播放器、鬧鐘、無線地面濕度控制系統、寵物活動監視器、低功耗藍牙姿態控制等。在這些小項目中,MCU實現信息的收集和傳輸,用起來十分方便。

最近,我接手一個項目,這個項目不僅要求我使用FPGA,而且還要求我使用功能更強大的ARM。這都是我從未接觸過的領域。在這個系列博客中,我將介紹我是如何將自己現有的MCU知識和經驗運用到FPGA中的。本文是系列博客的在第一篇,我將從FPGA的優點和缺點入手,并介紹Terasic DE10 Nano開發套件,以及IP核在FPGA設計中的作用。

關于FPGA

如果你開發的項目一直與MCU有關,你一定會發現MCU的學習曲線并不陡峭,所用的開發工具都可以輕易獲得,開發和調試的過程簡單,設計很容易上手。不過,你也會發現,MCU在處理復雜事務、運行速度和接口的多樣性上是很有限的。我個人所經歷的項目,由于功能既不復雜,也沒有重要的處理需求,因此,一直以來MCU是很理想的選擇。

FPGA是包含可編程邏輯元件(LE)的集成電路,其可編程單元已經內置在芯片中,功能十分靈活。

例如,他們可以通過編程作為加速器或RAM來提高系統性能,可以通過編程實現新的標準或算法,也可以根據需求添加各種通信接口,所有的這些都有助于降低系統成本并延長產品生命周期。但這種設計的缺點是學習曲線非常陡峭,對于MCU開發人員來說,在剛剛學習FPGA的時候,因IO端口和編碼方式的變化,學習起來還是很困難的。對于MCU來說,在同一時刻,只能實現一個或一組IO的翻轉,并且所有的IO只有一個電壓標準。而FPGA的IO是并行處理的,并且不同bank的IO可以遵循不同電壓標準。

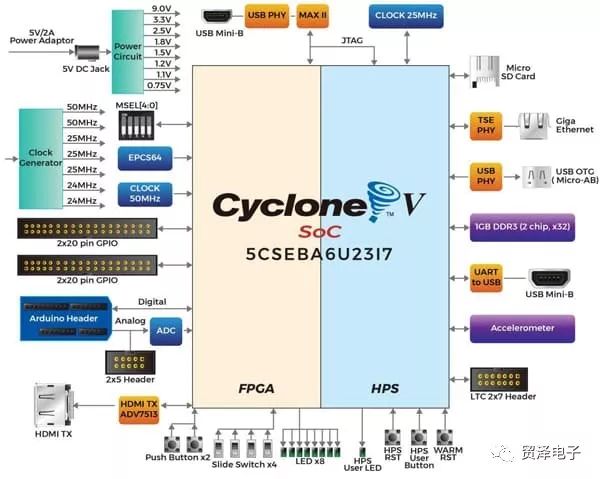

幸運的是,我發現了Intel Cyclone V SoC DE10 Nano開發套件。英特爾Cyclone V SoC將FPGA與雙核ARM Cortex A9結合,允許使用多種方式配置FPGA,開發套件包含顯示和通信端口、按鈕和開關、引腳映射和快速配置工具、JTAG調試器以及來自Terasic和Intel的文檔說明和指南。

規劃FPGA開發

在規劃MCU開發的時候,我們首先確定需要哪些接口,如SPI,I2C,Wi-Fi等,然后根據MCU的電壓,引腳數量,提供的通信接口,支持的庫和價格作出MCU的選型。在使用FPGA的時候,所有的通信接口都是依靠編程來實現的,因此無需考慮通信接口的限制。其限制因素是邏輯單元的數量,因為所需要的端口,軟核或存儲器單元都是基于這些邏輯單元創建的。因此,需要做權衡的是,邏輯單元數目越大,FPGA的能力越強,其成本也越高。雖然FPGA通常具有較高的初始成本,但由于它們可以實現多個芯片組件的功能,并且還能夠節省大量板上空間,所以綜合來看其成本并不高。

我發現自己正處在一個關鍵時刻:我要如何確定我的設計需要多少邏輯單元?

答案是,這取決于對IP核的需求,IP核由協議、功能、代碼以及外部模塊執行的特定任務組成。幾乎所有的FPGA都是由邏輯單元LE,寄存器和I / O bank組成。具體來說:

邏輯單元LE是可編程的,是FPGA內部的門陣列,每一個邏輯單元都具有一定數量的查找表,觸發器和多路復用器。

寄存器是一組觸發器,能夠保存數據并實現諸如定時器等功能。

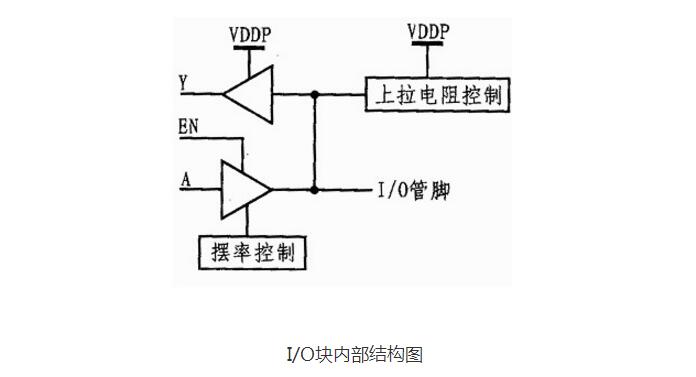

I / O bank是一組連接外部電路的輸入/輸出引腳。每個bank都有一個獨立的電壓標準,并且有電流大小的限制。

最初我并沒有意識到IP核的重要性,因為我還沒有領會到這樣一個事實:IP核實現了一種能夠代替物理設備的能力,這些設備包括MCU、通信控制器或者其他一些我會使用另一個芯片實現的東西。

如圖1所示,Cyclone V 包含FPGA層和HPS層,在DE10 Nano上FPGA層主要用作低延遲的I/O擴展。所有這一切體現了FPGA的另一個設計特點:它可以在單個芯片上實現多個PCB板上芯片的功能,從而,使得后續的設計更加靈活。

圖1:Terasic DE10 Nano Cyclone V FPGA和硬件處理器系統(HPS)的接口布局。(來源:Terasic)

大部分低級I / O端口通過FPGA進行控制和連接,這就降低了CPU等待低級別I/O端口的時間,同時也允許數據在傳遞到HPS之前進行相應的處理或調整。

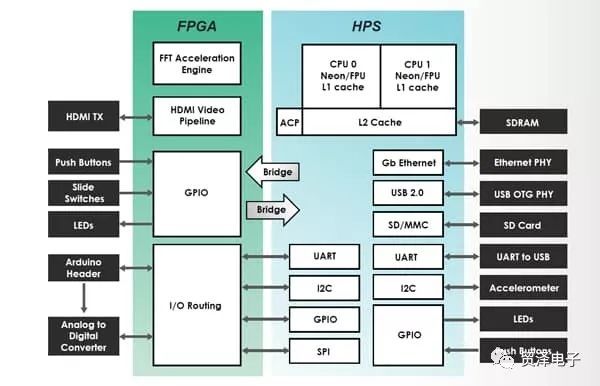

這是一種多么完美的設計,Cyclone V FPGA的接口可擴展,而且能夠實現加速器的功能,這種設計架構提高了HPS層的處理能力。在這種情況下,正如圖2所示,HDMI接口是非HPS本地接口,因此用作HDMI的MCU資源并不多。

圖2:FPGA和HPS的接口布局(來源:Terasic)

HDMI的輸出在FPGA上運行,這降低CPU負載并添加了非本地接口;

存在一個OpenCV加速示例,這是為了體現兩種類型處理器結合的優勢;

Terasic已經實現了基本的通信功能范例,并且有一個預定義的引腳映射列表,該列表定義了電壓和電流限制。

總的來說,我很喜歡FPGA,并且對它的擴展和加速功能十分感興趣。不過,我也想知道他們到底有哪些局限性。他們能運行到高的頻率?他們可以支持哪些協議?他們會消耗多少LE?總的來說,IDE比我用過的其他軟件更簡單,并且包含了令人驚嘆的文檔。硬件似乎非常強大,現在我正在設計一個項目,這個項目能夠測試板上的硬件限制。

-

電流

+關注

關注

40文章

6937瀏覽量

132522 -

加速器

+關注

關注

2文章

806瀏覽量

38015 -

電壓

+關注

關注

45文章

5637瀏覽量

116118

發布評論請先 登錄

相關推薦

FPGA如何從入門到高手?

求助,關于TRAVEO MCU閃存啟動流程的問題求解

FPGA 22年從配角到主角

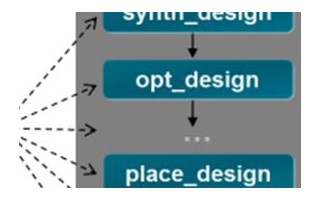

FPGA設計流程“又臭又長”?從eda工具理解超級簡單!

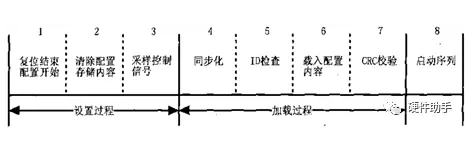

關于Xilinx FPGA的配置流程淺析

關于FPGA它的開發流程是怎樣的

從PCB到完整的物聯網項目:關于MCU的選擇

關于從MCU到FPGA的教學流程

關于從MCU到FPGA的教學流程

評論