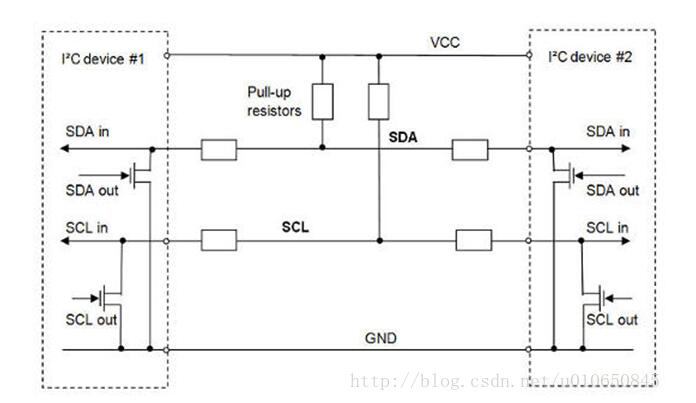

IIC 開發于1982年,當時是為了給電視機內的CPU和外圍芯片提供更簡易的互聯方式。電視機是最早的嵌入式系統之一,而最初的嵌入系統是使用內存映射(memory-mapped I/O)的方式來互聯微控制器和外圍設備的。要實現內存映射,設備必須并聯入微控制器的數據線和地址線,這種方式在連接多個外設時需大量線路和額外地址解碼芯片,很不方便并且成本高。為了節省微控制器的引腳和和額外的邏輯芯片,使印刷電路板更簡單,成本更低,位于荷蘭的Philips實驗室開發了 ‘Inter-Integrated Circuit’,IIC 或 IIC ,一種只使用二根線接連所有外圍芯片的總線協議。最初的標準定義總線速度為100kbps。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605197 -

cpu

+關注

關注

68文章

10901瀏覽量

212672 -

協議

+關注

關注

2文章

606瀏覽量

39303

發布評論請先 登錄

相關推薦

【小梅哥FPGA進階教程】第十六章 IIC協議詳解+UART串口讀寫EEPROM

`十六、IIC協議詳解+Uart串口讀寫EEPROM本文由杭電網友曾凱峰根據小梅哥FPGA IIC協議基本

發表于 04-08 16:04

FPGA零基礎學習:IIC協議驅動設計

不多說,上貨。IIC協議驅動設計本篇實現基于叁芯智能科技的SANXIN -B01 FPGA開發板,以下為配套的教程,如有入手開發板,可以登錄官方淘寶店購買,還有配套的學習視頻。叁芯智能科技 F

發表于 03-21 17:56

FPGA基礎知識之IIC協議讀寫解析

很多數字傳感器、數字控制的芯片(DDS、串行ADC、串行DAC)都是通過IIC總線來和控制器通信的。不過IIC協議仍然是一種慢速的通信方式,標準IIC速率為100kbit/s,快速模式

發表于 05-05 10:17

?8282次閱讀

一文解讀IIC總線的FPGA實現原理及過程

本文首先介紹了IIC總線概念和IIC總線硬件結構,其次介紹了IIC總線典型應用,最后詳細介紹了IIC總線的

發表于 05-31 10:56

?6757次閱讀

FPGA設計中時序分析的基本概念

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

FPGA進階教程:IIC協議若干基礎概念

FPGA進階教程:IIC協議若干基礎概念

評論