在惡劣的環(huán)境中,為了安全,功能或改善的抗噪能力,需要對外部接口進(jìn)行電隔離。其中包括用于工業(yè)測量和控制的數(shù)據(jù)采集模塊中使用的模擬前端,以及處理節(jié)點(diǎn)之間的數(shù)字接口。

過去,高達(dá)幾Mb的帶寬足以用于轉(zhuǎn)換器接口或工業(yè)背板,從而允許使用光耦合器隔離諸如串行外圍接口(SPI)或RS-485之類的協(xié)議。數(shù)字隔離器改善了此類隔離接口的安全性,性能和可靠性,并提供了集成隔離和I / O。但是,諸如工業(yè)4.0和物聯(lián)網(wǎng)(IoT)之類的趨勢要求更廣泛的測量和控制,以及更高的速度和精度,從而導(dǎo)致對增加帶寬的更大需求。

由于與物理域的數(shù)字交互越來越多,因此對電流隔離的需求也在激增,需要保護(hù)其免受電動(dòng)機(jī)和電源系統(tǒng),人類操作員和靜電放電以及諸如雷擊引起的電涌等外部因素的影響。精密測量還可能需要與噪聲源隔離,例如局部和微型電源電路以及高速數(shù)字處理。

低壓差分信號(hào)(LVDS)是高性能轉(zhuǎn)換器和高帶寬FPGA或ASIC I / O的普遍存在的高速接口。差分信號(hào)由于反相和同相信號(hào)之間的相互耦合而具有較高的抗外部電磁干擾(EMI)的能力,這也相應(yīng)地使LVDS信號(hào)產(chǎn)生的任何EMI最小化。為LVDS接口增加隔離功能可提供透明解決方案,可將其插入現(xiàn)有信號(hào)鏈中,以進(jìn)行高速和高精度測量以及控制應(yīng)用。

今天存在哪些選擇?

對于轉(zhuǎn)換器和處理器接口的電流隔離,標(biāo)準(zhǔn)的數(shù)字隔離器仍然比光耦合器具有更快,更強(qiáng)大,更可靠的解決方案。但是,支持高速或精密轉(zhuǎn)換器的典型LVDS數(shù)據(jù)速率為數(shù)百M(fèi)b,而最快的標(biāo)準(zhǔn)數(shù)字隔離器則支持高達(dá)150 Mbps。

為了支持更高帶寬的隔離,系統(tǒng)設(shè)計(jì)人員(到現(xiàn)在為止)已轉(zhuǎn)向定制設(shè)計(jì)密集型解決方案,例如使用變壓器或電容器的反序列化或離散解決方案。這些增加了成本和設(shè)計(jì)時(shí)間,反序列化甚至可能僅需要針對該功能的額外簡單FPGA。變壓器和電容器需要對LVDS信號(hào)進(jìn)行仔細(xì)的信號(hào)調(diào)理,從而導(dǎo)致需要交流平衡編碼的特定于應(yīng)用和數(shù)據(jù)速率的解決方案。進(jìn)一步的解決方案是使用光纖通信鏈路,但是由于成本和增加的復(fù)雜性,它更適合于千兆位的要求。高速隔離的選擇范圍如圖1所示,其價(jià)值主張(取決于設(shè)計(jì)的難易程度和成本)與實(shí)現(xiàn)的最大速度相對應(yīng)。

圖1.隔離器實(shí)現(xiàn)的價(jià)值主張與隔離器速度的關(guān)系

與此相反,如圖2,ADI公司引入了家庭投遞LVDS隔離器:ADN4650/ADN4651/ADN4652,使用我耦合器?增強(qiáng)的技術(shù),最高可運(yùn)行600 Mbps。除了符合TIA / EIA-644-A LVDS的I / O,完整的隔離器信號(hào)鏈也是完全差分的,從而實(shí)現(xiàn)了高抗擾度和低排放解決方案。提供了兩個(gè)隔離的LVDS通道,一個(gè)發(fā)送和一個(gè)接收(ADN4651,反之亦然,對于ADN4652)或兩個(gè)發(fā)送或接收(ADN4650)。內(nèi)部高速電路工作在2.5 V電壓下,在工業(yè)系統(tǒng)中可能不會(huì)作為電源軌使用,因此提供了內(nèi)部低壓降穩(wěn)壓器(LDO)(如圖3所示)以允許單個(gè)寬體SOIC解決方案,即使使用3.3 V電源供電也是如此。

圖2. ADN4651 600 Mbps LVDS隔離器框圖。

圖3. ADN4651的眼圖和直方圖。

這些新型LVDS隔離器是否是嵌入式解決方案?

為了確保可以將這些LVDS隔離器插入轉(zhuǎn)換器到處理器的接口,或者以高達(dá)600 Mbps的速度運(yùn)行的處理器內(nèi)鏈路,ADN465x系列具有精確的時(shí)序和超低的抖動(dòng)。這很重要,因?yàn)樵?00 Mbps時(shí),單位間隔(UI,例如位時(shí)間)僅為1.6 ns,因此邊緣上的任何抖動(dòng)都必須仍留有足夠的時(shí)間讓接收組件采樣該位。假設(shè)誤碼率為1×10-12,ADN465x的典型總抖動(dòng)為70 ps,或者在600 Mbps時(shí)<5%UI?。

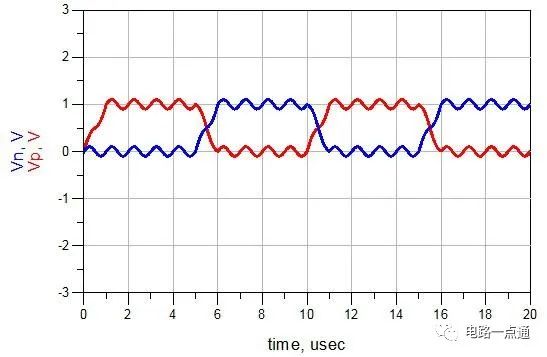

如何量化抖動(dòng)

觀察抖動(dòng)的最基本方法是使用差分探頭測量LVDS信號(hào)對,并在上升沿和下降沿均觸發(fā),并將示波器設(shè)置為無限余輝。這意味著高到低和低到高的過渡被疊加,從而可以測量交叉點(diǎn)。分頻器的寬度對應(yīng)于到目前為止測得的峰峰值抖動(dòng)或時(shí)間間隔誤差(TIE)(比較圖3所示的眼圖和直方圖)。有些抖動(dòng)是由隨機(jī)源引起的(例如熱噪聲),這種隨機(jī)抖動(dòng)(RJ)意味著示波器上看到的峰峰值抖動(dòng)受到運(yùn)行時(shí)間的限制;直方圖的尾巴將隨著運(yùn)行時(shí)間的增加而增加。

相比之下,確定性抖動(dòng)(DJ)的源是有界的,例如由于脈沖偏斜引起的抖動(dòng),與數(shù)據(jù)速率有關(guān)的抖動(dòng)(DDJ)和符號(hào)間干擾(ISI)。由于高到低和低到高傳播延遲之間的差異而產(chǎn)生脈沖偏斜。這可以通過偏移分頻來觀察,以便在0 V時(shí),兩個(gè)邊緣分開(通過圖3的直方圖中的分離很容易看出)。DDJ是由整個(gè)工作頻率上的傳播延遲差異引起的,而ISI是由于先前的過渡頻率對當(dāng)前過渡的影響而引起的(邊沿時(shí)序通常在1 sec或0 sec序列與1010模式之后會(huì)有所不同)。

為了完全估計(jì)給定誤碼率(TJ @ BER)的總抖動(dòng),可以基于對測量的TIE分布的模型擬合來計(jì)算RJ和DJ。一種這樣的模型是對偶Dirac模型,該模型假設(shè)高斯隨機(jī)分布與對偶Dirac delta函數(shù)(兩個(gè)Dirac delta函數(shù)之間的間隔對應(yīng)于確定性抖動(dòng))卷積。對于具有明顯確定性抖動(dòng)的TIE分布,分布將在視覺上近似該模型。一種復(fù)雜情況是,某些確定性抖動(dòng)可能會(huì)影響高斯分量,這意味著雙重Dirac可能會(huì)低估確定性抖動(dòng),而會(huì)高估隨機(jī)抖動(dòng)。但是,對于給定的誤碼率,兩者的結(jié)合仍將允許準(zhǔn)確估計(jì)總抖動(dòng)。

RJ從建模的高斯分布中指定為一個(gè)1σrms值,這意味著可以推斷出更長的運(yùn)行長度(低BER),人們只需選擇適當(dāng)?shù)亩鄠€(gè)σ即可沿著分布的尾部移動(dòng)足夠遠(yuǎn)(14σ對應(yīng)1×10-12位錯(cuò)誤)。然后添加DJ以提供TJ @ BER估計(jì)。對于信號(hào)鏈中的多個(gè)元素,可以將RJ值進(jìn)行幾何求和,而將DJ值進(jìn)行代數(shù)求和,而不是添加多個(gè)TJ值(過高估計(jì)抖動(dòng)),從而對整個(gè)信號(hào)鏈進(jìn)行更合理的TJ @ BER估算。

RJ,DJ和TJ @ BER均分別為ADN4651指定,并基于對多個(gè)單元的統(tǒng)計(jì)分析為每個(gè)值提供最大值,以確保在電源,溫度和工藝范圍內(nèi)具有這些抖動(dòng)值。

不同的LVDS接口如何依靠精確的數(shù)據(jù)轉(zhuǎn)換?

典型的接收器可以忍受10%或20%的UI抖動(dòng),因此,例如,將外部LVDS端口與ADN465x隔離,可以通過PLC和I / O模塊之間的電纜安全地?cái)U(kuò)展工業(yè)背板。最大電纜距離將取決于允許的數(shù)據(jù)速率,電纜結(jié)構(gòu)和連接器類型,但是在使用較低的數(shù)據(jù)速率(例如使用高速連接器和適當(dāng)?shù)钠帘坞p絞線電纜時(shí)為200 Mbps)時(shí),可能會(huì)使用幾米長的電纜。

模數(shù)轉(zhuǎn)換器(ADC)接口通常利用LVDS進(jìn)行源同步數(shù)據(jù)傳輸。這意味著LVDS時(shí)鐘與其他LVDS通道上的一個(gè)或多個(gè)數(shù)據(jù)位流并行發(fā)送。ADN4650的通道間偏斜低,分別≤300ps和≤500ps,有助于實(shí)現(xiàn)這一點(diǎn)。這些偏斜值指定了跨多個(gè)通道的從高到低(或從低到高)傳播延遲之間的最大差異,從統(tǒng)計(jì)上保證了所有ADN4650器件在電源,溫度和過程中的傳播延遲。≤100ps的低脈沖偏斜允許在時(shí)鐘的上升沿和下降沿對數(shù)據(jù)進(jìn)行時(shí)鐘同步以實(shí)現(xiàn)雙倍數(shù)據(jù)速率(DDR)時(shí)被時(shí)鐘同步,這是某些轉(zhuǎn)換器用來增加輸出帶寬的。

為了成功地完全隔離使用外部時(shí)鐘源的模擬前端,例如,一組時(shí)鐘同步的多個(gè)數(shù)據(jù)采集通道,可能需要隔離ADC采樣時(shí)鐘。這對任何隔離器都是一個(gè)挑戰(zhàn),因?yàn)闀r(shí)鐘上的任何抖動(dòng)都會(huì)直接增加孔徑抖動(dòng),從而降低測量質(zhì)量。與時(shí)鐘源一樣,用于時(shí)鐘分配的LVDS信號(hào)鏈組件(如扇出緩沖器)通常會(huì)將這種抖動(dòng)指定為加性相位抖動(dòng)。這意味著將輸入時(shí)鐘的相位噪聲與輸出時(shí)鐘的相位噪聲進(jìn)行比較,并且在相關(guān)的頻率范圍(通常為12 kHz到20 MHz)之間積分積分之差。ADN465x系列實(shí)質(zhì)上是具有集成隔離功能的LVDS緩沖器,因此,相同的觀點(diǎn)對于分析對ADC采樣的影響很有用。使用ADN465x時(shí),通過確保典型的附加相位抖動(dòng)僅為376 fs,即使添加電隔離,也可以保持原始測量質(zhì)量,尤其是添加隔離可以消除處理器側(cè)數(shù)字電路的噪聲時(shí)。

在參考電路CN-0388中使用18位,5 MSPS SAR ADC AD7960驗(yàn)證了600 Mbps的無錯(cuò)誤傳輸,同步到300 MHz時(shí)鐘以及隔離采樣時(shí)鐘時(shí)的完整ADC性能和分辨率。如圖4所示。現(xiàn)有的ADC評估平臺(tái)使用插入器透明隔離模擬前端,從而將ADC電路板與高速SDP-H1評估平臺(tái)隔離。該軟件未更改,使用精密模擬源評估數(shù)據(jù)手冊規(guī)格可確保與非隔離平臺(tái)具有相同的性能。

圖4. AD7960和SDP-H1的ADN4651隔離電路。

哪些其他應(yīng)用程序可以使用LVDS隔離?

隔離的模擬前端或隔離的工業(yè)背板是兩個(gè)有用的應(yīng)用示例,以說明隔離LVDS所提供的機(jī)會(huì),但是該技術(shù)還有許多其他應(yīng)用。視頻信號(hào),以平板顯示器通常使用LVDS信號(hào),和HDMI?信令使用類似差分信號(hào),共模邏輯(CML)。這些通常不需要隔離,但是對于某些應(yīng)用(例如醫(yī)學(xué)成像或工業(yè)PC中的外部顯示端口),電流隔離可以分別保護(hù)人員或設(shè)備。

-

lvds

+關(guān)注

關(guān)注

2文章

1045瀏覽量

65946 -

信號(hào)隔離

+關(guān)注

關(guān)注

1文章

60瀏覽量

16619

原文標(biāo)題:人才經(jīng)濟(jì)論壇·2019今日開幕!

文章出處:【微信號(hào):hbrchinese,微信公眾號(hào):哈佛商業(yè)評論】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

差分信號(hào)與共模信號(hào)的比較

差分信號(hào)的優(yōu)點(diǎn)和缺點(diǎn)

采用PGA281可編程運(yùn)放對小信號(hào)進(jìn)行放大,由于PGA281輸出的是差分信號(hào),如何對差分信號(hào)進(jìn)行有源濾波呢?

請問ADS1255可以測量隔離的差分信號(hào)嗎?

差分信號(hào)的阻抗匹配

認(rèn)識(shí)差分信號(hào)的常見誤區(qū)

探討差分信號(hào)的優(yōu)缺點(diǎn)

低壓差分信號(hào)(LVDS)在LED燈墻中的應(yīng)用

差分信號(hào)是什么意思?差分信號(hào)怎么產(chǎn)生?

高速差分信號(hào)有哪些

高速差分信號(hào)設(shè)計(jì)需要關(guān)注的事項(xiàng)

為何需要隔離低壓差分信號(hào)

為何需要隔離低壓差分信號(hào)

評論