FPGA(Filed programmable gate device):現(xiàn)場可編程邏輯器件

FPGA基于查找表加觸發(fā)器的結(jié)構(gòu),采用SRAM工藝,也有采用flash或者反熔絲工藝;主要應(yīng)用高速、高密度大的數(shù)字電路設(shè)計。

FPGA由可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源(時鐘/長線/短線)、底層嵌入功能單元、內(nèi)嵌專用的硬核等組成;

目前市場上應(yīng)用比較廣泛的FPGA芯片主要來自Altera與Xilinx。另外還有其它廠家的一些低端芯片(Actel、Lattice)。

這里主要介紹AlteraCyclone II系列FPGA的內(nèi)部硬件結(jié)構(gòu):

1.FPGA器件結(jié)構(gòu)

2.可編程輸入/輸出單元IOE

3.可編程邏輯單元LE

4.嵌入式塊RAM

5.布線資源

6.底層嵌入功能單元

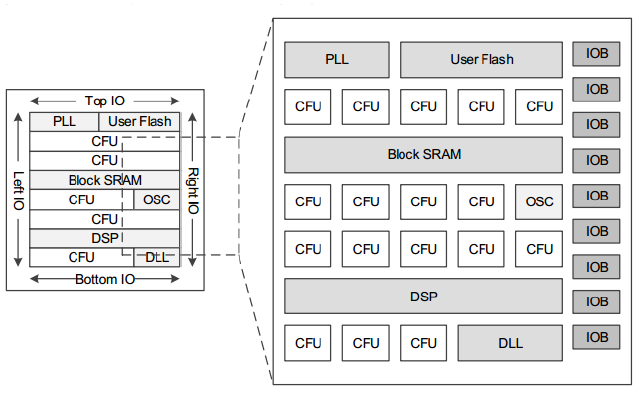

FPGA器件結(jié)構(gòu)

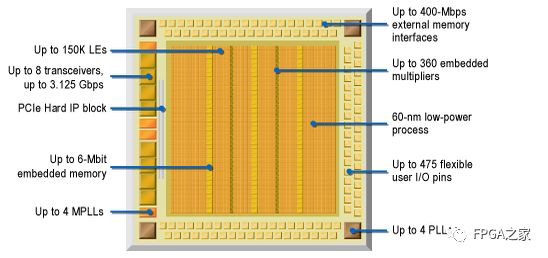

Altera cyclone IV器件結(jié)構(gòu)

FPGA的內(nèi)部結(jié)構(gòu)包括:

1.可編程邏輯門陣列,由最小單元LE組成

2.可編程輸入輸出單元IOE

3.嵌入式RAM塊,為M4K塊,每個的存儲量為4K,掉電丟失

4.布線網(wǎng)絡(luò)

5.PLL鎖相環(huán),EP4CE6E22C8N最大的倍頻至250MHz,這也是該芯片的最大工作

可編程輸入/輸出單元IOE

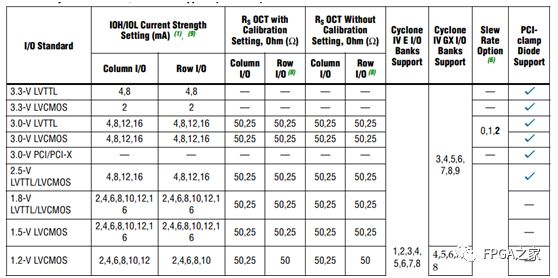

可編程I/O,可配置成OC門、三態(tài)門、雙向IO、單端/差分等;支持各種不同的I/O標(biāo)準(zhǔn):LVTTL、LVCOMS、SSTL、LVDS、HSTL、PCI等;

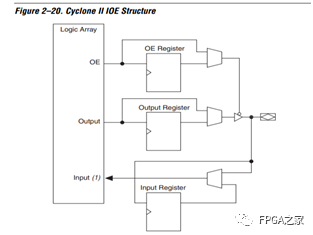

Altera 器件IOE結(jié)構(gòu)

Altera器件的輸入輸出結(jié)構(gòu):可配置成三態(tài)、輸入/輸出、雙向IO

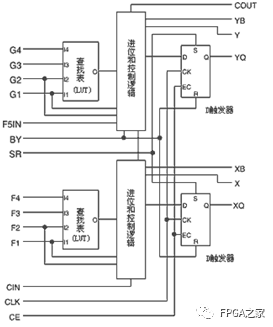

Altera器件中cyclone系列中的IOE結(jié)構(gòu)是基本的輸入、輸出、使能的觸發(fā)器結(jié)構(gòu)。

可編程邏輯單元LE

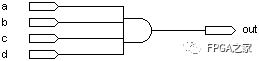

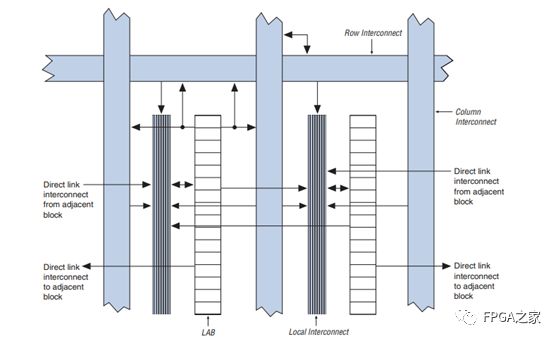

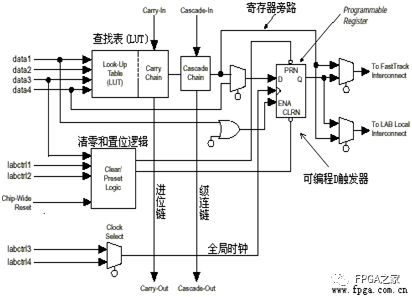

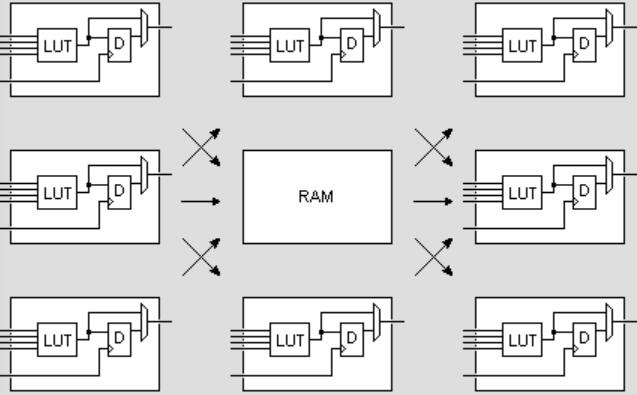

基本可編程邏輯單元LE由查找表(Look up table)觸發(fā)器(FF)組成,而LE是組成LAB的最小單元;

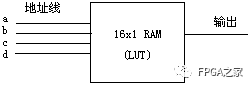

LUT一般是4輸入查找表,高端器件(xilinx v5)采用LUT-6結(jié)構(gòu);LUT可看成4位地址線的16x1的RAM 結(jié)構(gòu)。

FF是可編程的觸發(fā)器,可配置成同步/異步復(fù)位、同步/異步置位、使能、裝載等功能觸發(fā)器。

可編程邏輯塊:

Altera:LAB

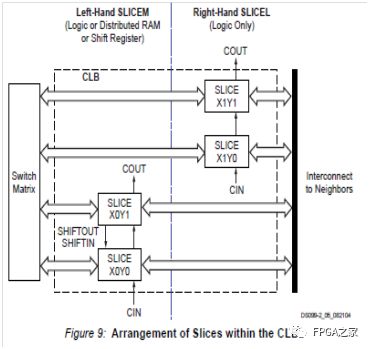

Xilinx:CLB

Xilinx CLB由四個SLICE構(gòu)成;而Altera的LAB由16個/8個LE構(gòu)成;

基本邏輯單元LE/SLICE:

Altera:LE

Xilinx:SLICE

xilinx 為SLICE:包括兩個LUT-4/兩個FF;

altera為LE:包括一個LUT-4/一個FF;

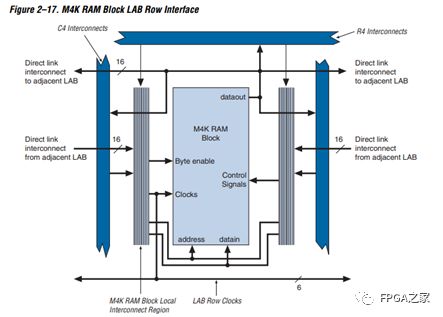

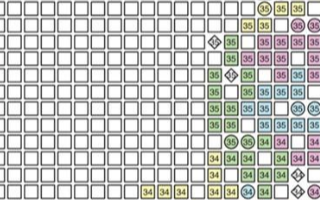

嵌入式塊RAM

嵌入式塊RAM可配置單/雙端口RAM、偽雙端口RAM、ROM、FIFO、SHIFT、CAM等;不同廠家的塊RAM大小不一樣:

Altera:M512、M4K M4K、M-RAM(512K);

Xilinx:18kbit;

Lattic:9kbit;

Altera:M4K:

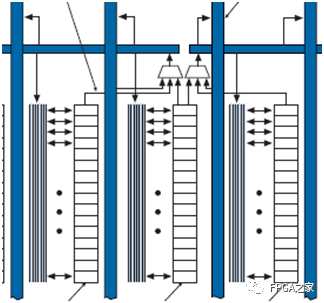

布線資源

全局布線資源:用于全局時鐘/全局復(fù)位/全局置位布線;

長線資源:用于BANK或者嵌入式功能單元的高速信號或者第二全局時鐘的布線;

短線資源:用于其中邏輯單元間的邏輯互聯(lián)與布線;

全局布線資源:

全局時鐘樹:

底層嵌入式功能塊

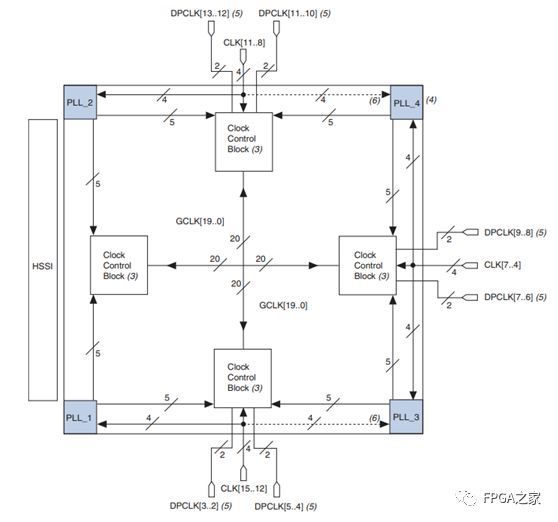

主要是指PLL/DPLL、DCM、DSP48、乘法器、嵌入式硬核/軟核;

Xilinx:DCM、DSP48/48E、DPLL、Multiplier等

Altera:PLL/EPLL/FPLL、DSPcore等;

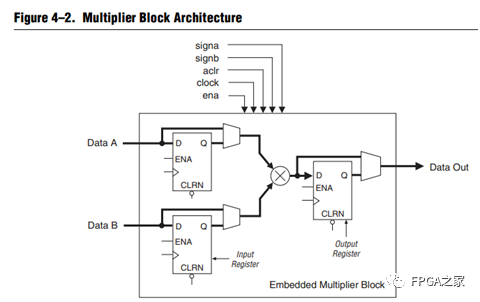

Multiplier結(jié)構(gòu)

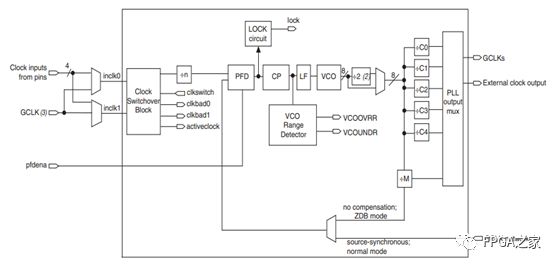

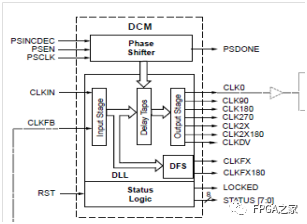

PLL/DCM:嵌入式鎖相環(huán)

Altera:PLL

Xilinx:DCM

Altera的Cyclone II器件最多有四個PLL,分布在芯片四個角;需要主要的是Altera的PLL是模擬鎖相環(huán),在電源/地方面要做考慮。

Xilinx的spatan-3器件最多有四個DCM,也是分布在芯片四個角。

兩者的區(qū)別:Altera的PLL可支持較低的輸入頻率,可Xilinx的DCM支持的最低鎖相頻率為24/32MHz;但Xilinx的高端器件Virtex-5的DPLL可達(dá)到很低的輸入頻率。

內(nèi)嵌專用硬核

指高速串行收發(fā)器;GMAC、SERDES、PCIe等;

Xilinx:GMAC、SERDES、PCI、GTX、GRX

Atera:GMAC、SERDES、PCIe、SPI.4/SFI.5

-

芯片

+關(guān)注

關(guān)注

456文章

50950瀏覽量

424755

原文標(biāo)題:你絕對可以看懂的FPGA芯片內(nèi)部硬件介紹

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA入門知識介紹

基于Altera FPGA的軟硬件協(xié)同仿真方法介紹

介紹FPGA開發(fā)板內(nèi)部ram操作

了解FPGA的芯片內(nèi)部資源:IO是什么

詳細(xì)介紹關(guān)于FPGA開發(fā)板內(nèi)部ram是如何操作的

FPGA內(nèi)部結(jié)構(gòu)的詳細(xì)介紹

FPGA的硬件基礎(chǔ)教程免費下載

Xilinx FPGA芯片內(nèi)部時鐘和復(fù)位信號使用方法

簡單易懂的FPGA芯片內(nèi)部硬件介紹

簡單易懂的FPGA芯片內(nèi)部硬件介紹

評論