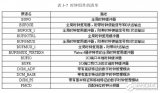

如果FPGA沒有外部時鐘源輸入,可以通過調用STARTUP原語,來使用FPGA芯片內部的時鐘和復位信號,Spartan-6系列內部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

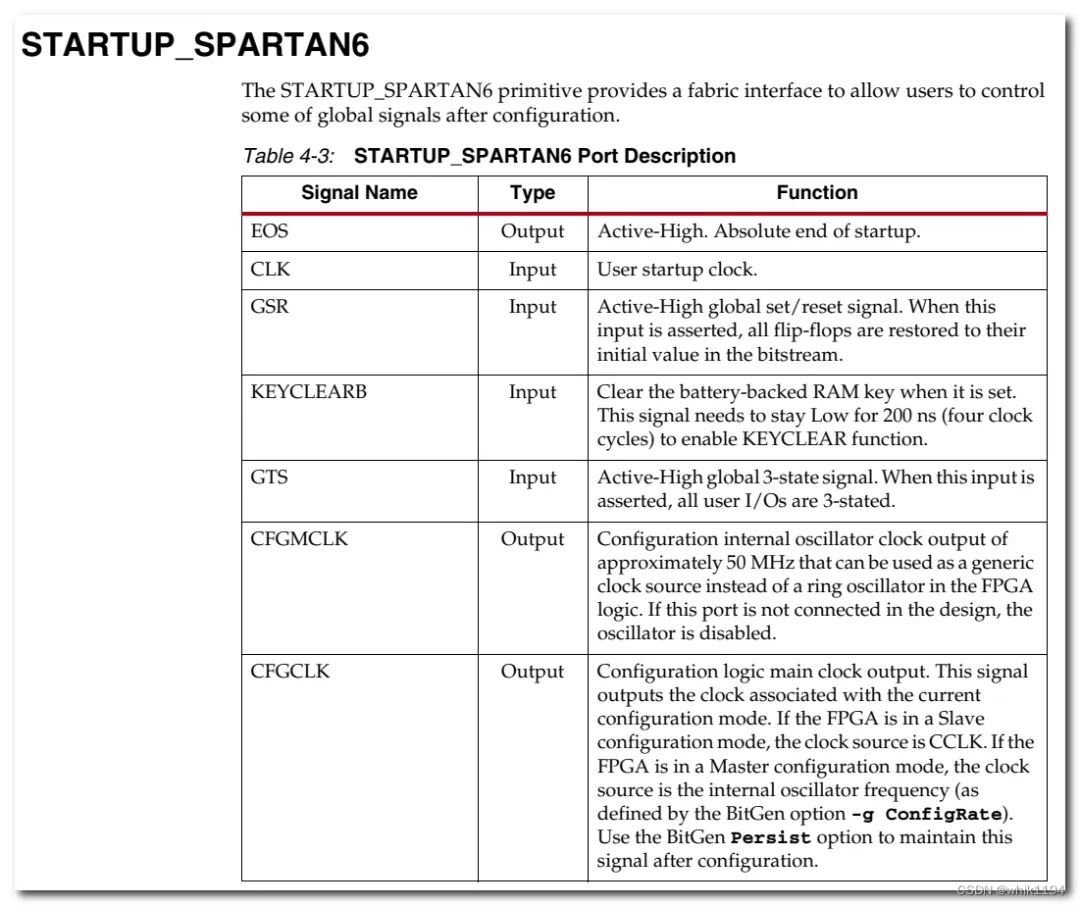

Spartan-6系列

wireclk_50m; wirerst_n; STARTUP_SPARTAN6STARTUP_SPARTAN6_inst( .CFGMCLK(clk_50m),//1-bitoutput:Configurationinternaloscillatorclockoutput. .EOS(rst_n),//1-bitoutput:ActivehighoutputsignalindicatestheEndOfConfiguration. );

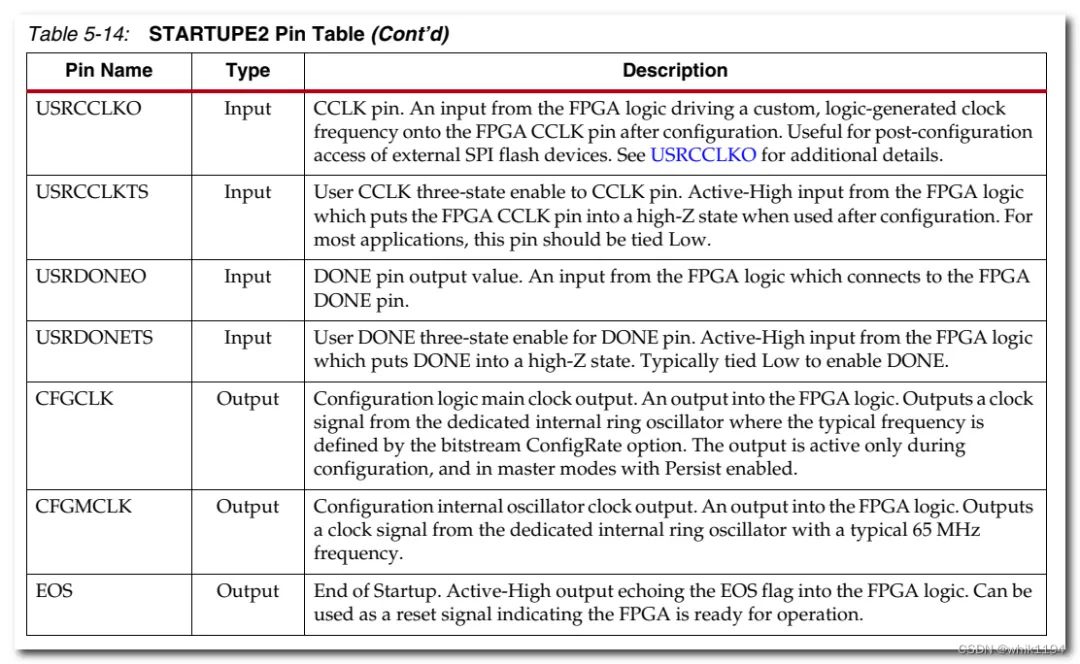

Artix-7(7系列)

wireclk_65m; wirerst_n; STARTUPE2STARTUPE2_ut0( .CFGMCLK(clk_65m),//1-bitoutput:Configurationinternaloscillatorclockoutput65MHz. .EOS(rst_n)//1-bitoutput:ActivehighoutputsignalindicatingtheEndOfStartup. );

分別可以參考文檔:

UG380:Spartan-6 FPGA Configuration

UG470:7 Series FPGAs Configuration

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA芯片

+關注

關注

3文章

246瀏覽量

39801 -

時鐘源

+關注

關注

0文章

93瀏覽量

15975 -

復位信號

+關注

關注

0文章

54瀏覽量

6322

原文標題:Xilinx FPGA芯片內部時鐘和復位信號使用

文章出處:【微信號:mcu149,微信公眾號:電子電路開發學習】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx FPGA的GTx的參考時鐘

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

發表于 09-15 09:14

?3692次閱讀

Xilinx_FPGA_內部結構深入分析

個MUX。利用這種2+1的組合可以產生DDR操作,Xilinx稱之為ODDR2。每個存儲單元都有6個接口信號:時鐘+時鐘時能,數據輸入+輸出,置位復

發表于 08-02 22:48

在FPGA開發中盡量避免全局復位的使用?(2)

在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對

發表于 02-11 11:46

?1016次閱讀

Xilinx全局時鐘的使用和DCM模塊的使用

在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其

發表于 11-22 07:09

?1w次閱讀

FPGA的理想的復位方法和技巧

引腳類似,對 FPGA 來說往往是異步的。設計人員可以使用這個信號在 FPGA 內部對自己的設計進行異步或者同步復位。

發表于 11-22 17:03

?5686次閱讀

Xilinx FPGA的同步復位和異步復位

對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區

發表于 07-13 09:31

?6653次閱讀

Xilinx-DCM的使用方法技巧

Xilinx-DCM的使用方法技巧(長城電源技術(深圳有限公司)-該文檔為Xilinx-DCM的使用方法技巧講解文檔,是一份還算不錯的參考文檔,感興趣的可以參考參考,,,,,,,,,,

發表于 09-28 12:46

?12次下載

Xilinx FPGA芯片內部時鐘和復位信號使用方法

Xilinx FPGA芯片內部時鐘和復位信號使用方法

評論