在描述米勒平臺(miller plateau)之前,首先來看看“罪魁禍首”米勒效應(miller effect) 。

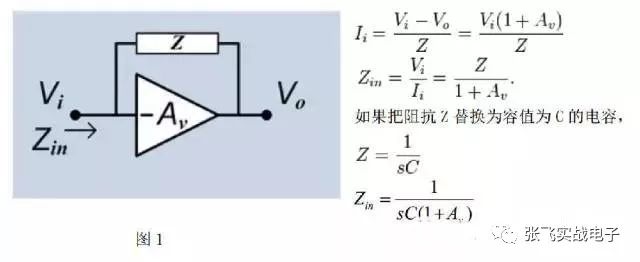

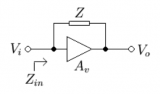

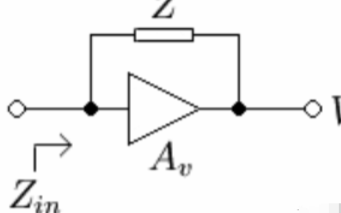

假設一個增益為-Av的理想反向電壓放大器如圖 1 所示,在放大器的輸出和輸入端之間連接一個阻值為 Z 的阻抗。定義輸入電流為 Ii(假設放大器的輸入電流為 0) ,輸入阻抗為 Zin,那么有如下的等式關系,

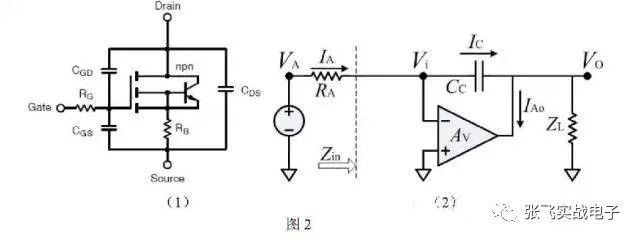

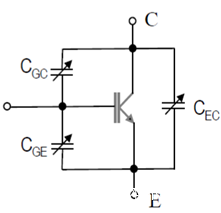

由此可見,反向電壓放大器增加了電路的輸入電容,并且放大系數為(1+Av) 。這個效應最早是由 John Milton Miller 發現的并發表在他 1920 的著作中,所以稱之為米勒效應。再聯系到我們的 MOSFET,加入寄生電容的原理圖可以由下左圖來表示。假設想象圖 2(1)的的 MOSFET 是一個共源電路(common source) :Drain 為輸出端,Source 接地,Gate為輸入端。根據 MOSFET 的小信號模型,MOSFET 形成了一個反向電壓放大器,其等效電路可以由圖 2(2)來表示。

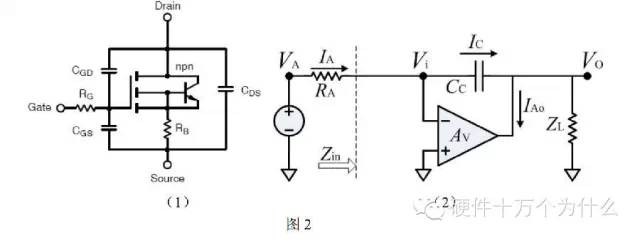

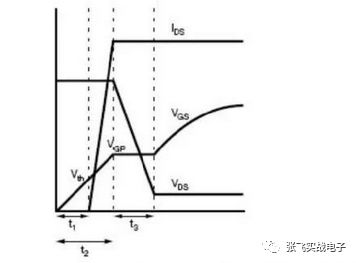

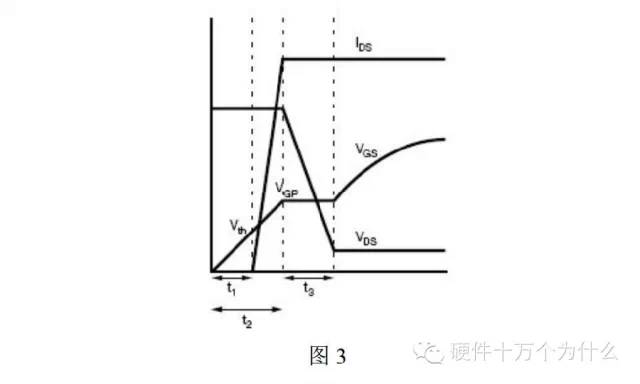

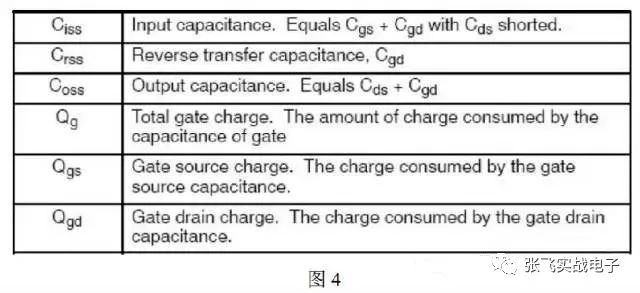

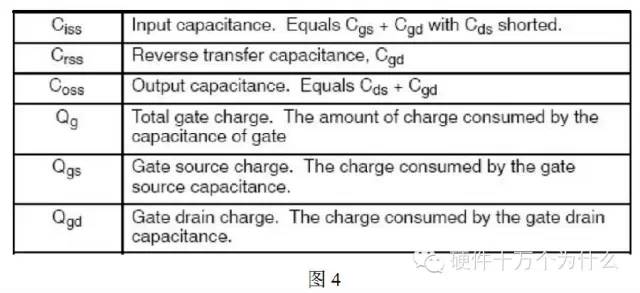

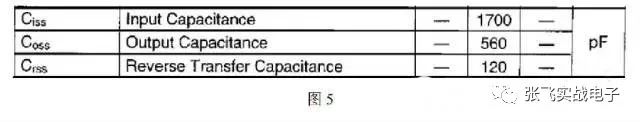

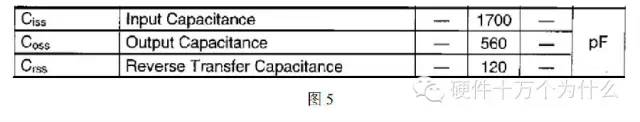

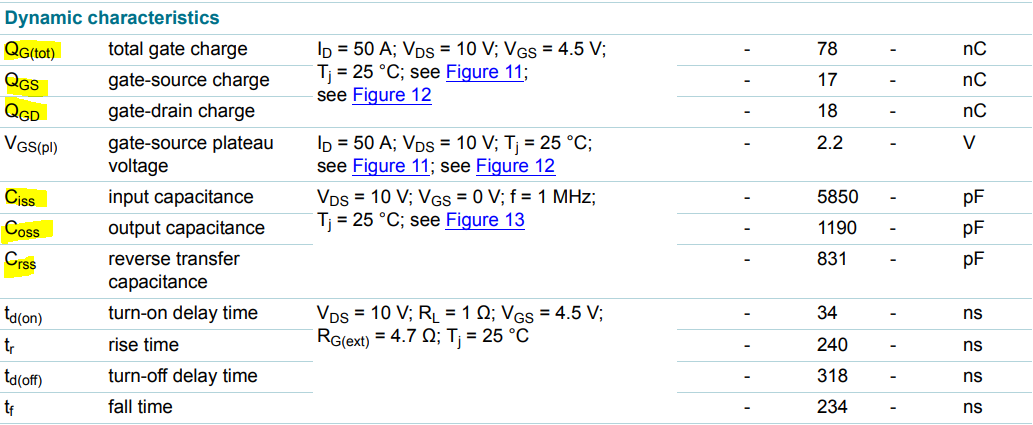

在 0-t1的時間內上升到 MOSFET 的閾值電壓。 漏極電流 IDS從 t1結束時到 t3開始時從 0 上升到穩定負載電流,VGS繼續上升到米勒平臺電壓 VGP。在 t3時間內,VGS一直處于平臺電壓,VDS開始下降至正向導通電壓 VF。在 t3 時間后,VGS繼續上升。這里我們來分析一下為什么波形會是這個樣子。首先,我們需要先要了解一下 MOSFET 寄生電容的大體情況。在 MOSFET 的 DATASHEET中,采用的定義方法如圖 4 所示。需要注意的是,Crss就是我們所說的 CGD。

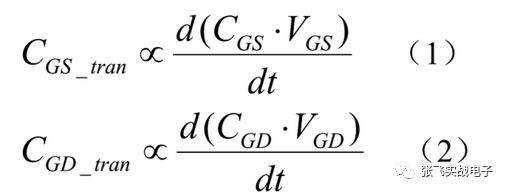

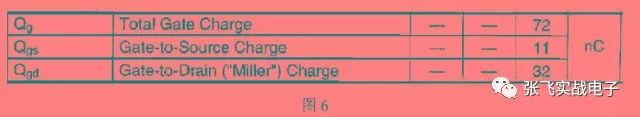

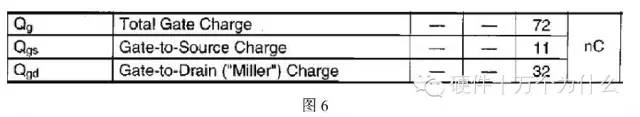

因此,相應的瞬態電容值與乘積(CGS*VGS)和(CGD*VGD)的斜率有關,既接合 MOSFET 的圖 3 來看,在 t3時間之前,由于 CGS遠大于 CGD,所以在此時間段內 VGS的上升斜率主要有 CGS決定。當 t3開始時,參照式(2, )VGD的變化使得給 CGD在這個時間段內的電容值增加,同樣使得充電電流迅速增加。所以在 t3時間內,VGS的斜率主要由 CGD的來決定。值得注意的是,VGS在 t3階段內的斜率往往都很小甚至為 0,這是因為 VGD在這段時間的電壓變化非常大, 使得門極中的大部分電流都用來給 CGD充電, 從而只有很少或者沒有電流流向CGS。再次使用IRF540為例, 在DATASHEET上的有這么一組數據, Qgs=11nC,Qgd=32nC. 從前面可以看出,MOSFET 關斷狀態下的 CGD 遠遠小于 CGS,但是卻需要更多的充電電荷。仔細看 Qgd 的注釋中,標明了是受到了“Miller”米勒效果的放大。

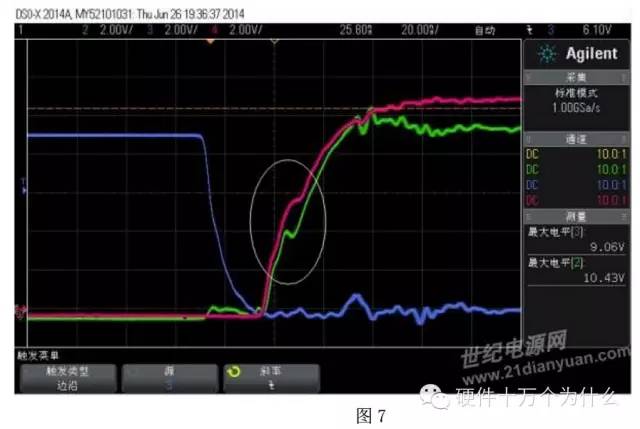

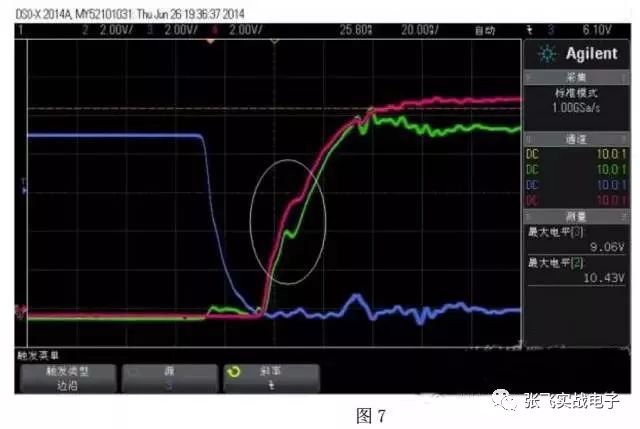

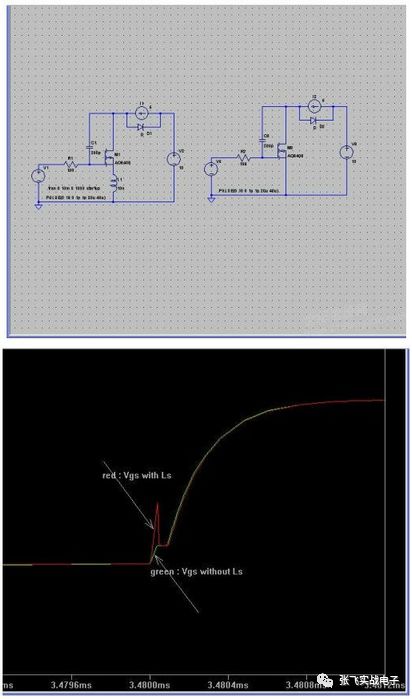

尖峰的主要形成原因與米勒效應并無太大關系, 主要是由于源極附近的雜散電感所致。 在圖3 的 t1-t3時刻之間,驟然增加的源極極電流在雜散電感上感應生成了電壓尖峰。

以下是網友一花一天堂的仿真對比試驗, 通過在 MOSFET 的源級處加入 nH 級的電感來模擬雜散電感。對比上下兩幅圖可知,源級附近的雜散電感為米勒平臺間電壓尖峰的主要原因。

圖8

這里需要指出的是,圖 3 只是一個近似的畫法,大家普遍認同 IDS的拐點與 VGS進入米勒平臺發生在同一時刻。這樣雜散電感產生的尖峰就出現在了米勒平臺之前。但是 VGS進入米勒平臺的時間是由 CGD與 VGD的乘積(CGD*VGD)的斜率決定的。當漏極電流很小且輸出阻抗很大的時候,VGS進入米勒平臺的時間要早于 IDS的拐點。這時,源極的雜散電感形成的電壓尖峰就出現在了米勒平臺之間。由于上面那段話過于生澀,經 greendot 老師的指點,這里可以用一個比較簡單的方法或者說是經驗來判斷雜散電感的尖峰所處的位置。若 MOSFET 連接的負載為感性(連接于 MOSFET的漏極) ,則產生的波形如圖 3 所示,產生的尖峰處于平臺之前。其作用原理:假設用一個電流源來模擬感性負載,并在其兩端反向并聯一個二極管用于模擬 MOSFET 關斷期間的電流回路,如圖 9 所示。當 Vgs上升至 Vth時,IDS從 0 開始上升,并由式(3)在 VGS上產生感應電壓。在 IDS上升至拐點既 IDS等于電流源電流之前,會有一部分的電流通過二極管返回至電流源。此時,由于二極管嵌位的作用,VDS兩端的電壓為供電電壓 Vcc(忽略二極管正向導通電壓) 。聯系本文關于米勒效應的描述,VDS電壓不變的時候,MOSFET 的放大增益為 0,所以此時的 VGS曲線還沒有受到米勒效應的影響。當 IDS上升至拐點后,二極管關斷,VDS的電壓再開始下降,如圖 3 所示。此時 MOSFET 形成了一個放大電路,CGD受到米勒效應的影響,使得 VGS進入米勒平臺。但 IDS已不再變化,此刻的式(3)為 0,所以形成的電壓尖峰處于米勒平臺之前。再次感謝一花一天堂的仿真圖。通過對比可以發現,感性負載是的雜散電感在 VGS上生成的電壓尖峰處于米勒平臺之前。

圖9

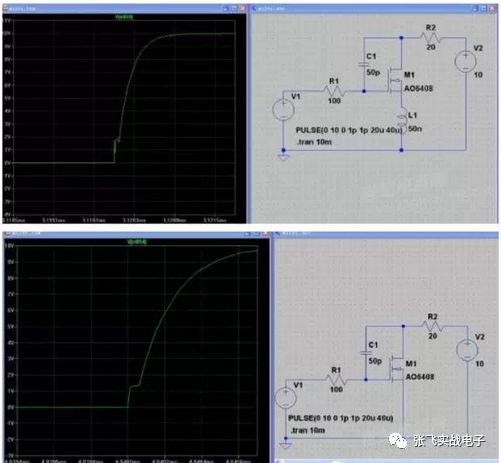

若負載為阻性時,其波形過程為:IDS從 0 開始上升時,VDS=Vcc-(IDS*Load) ,所以 VDS同時開始下降,MOSFET 即刻形成一個放大電路,VGS 進入米勒平臺。由于 IDS的上升過程和 VGS進入米勒平臺為同一時間, 在雜散電感上形成的感應電壓便疊加在了米勒平臺區間。 仿真結果如圖 10(下圖中的 Vds 應為 Vgs)

參考資料:1.Wikipedia, Miller Effect, Common Source.2.Vishay APP NOTE AN605, AN6083.IRF540 Datashee

-

放大器

+關注

關注

144文章

13778瀏覽量

214853 -

MOSFET

+關注

關注

147文章

7572瀏覽量

215485 -

張飛電子

+關注

關注

55文章

175瀏覽量

12757

原文標題:米勒平臺的形成原理

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MOS管的米勒效應:如何減小米勒平臺

米勒效應對MOSFET的危害

米勒效應的本質是什么?

米勒效應問題

MOS管的米勒效應:如何平衡抑制米勒效應和抑制EMI風險的關系

MOSFET米勒效應詳解

IGBT中米勒效應的影響和處理方法

詳解米勒平臺的米勒效應和形成原理

詳解米勒平臺的米勒效應和形成原理

評論