嵌入式系統設計人員面臨著對更高性能和更快上市時間的不斷增長的需求。嵌入式處理器需要經常實時地執行不斷擴展的任務。同時,應用需要高吞吐量和高能效以及小外形和低成本。多核微控制器單元(MCU)提供了一種可行的新解決方案,利用模塊化設計以經濟的價格提供多倍的性能提升。

幾十年來,隨著IC上晶體管數量的增加,芯片性能不斷提高。采用高速緩存和流水線等技術的更復雜的架構允許芯片設計人員使用不斷增加的硅密度來不斷提高處理速度。這已不再是這種情況。芯片設計人員已經耗盡了替代架構的可能性。生產力的增長已經從跟上摩爾定律的速度下降到不到一半。當今提高生產力的唯一方法是通過使用多個CPU來利用模塊化。這導致了多核MCU的發展。

硬件:同構與異構

我們將多核MCU定義為具有兩個或多個CPU的微處理器,這些CPU一致地共享一個公共存儲器。在多核架構中,每個處理器都有自己的指令流作用于自己的數據流(MIMD)。

多核MCU可以歸類為同構或異構。顧名思義,同類模塊具有兩個相同的CPU,可以并行或冗余地運行操作。德州儀器(TI)的Hercules系列產品專為安全應用而設計,擁有兩個同步運行的ARM Cortex-R4F CPU。它們執行相同的操作,然后比較每個時鐘周期的結果,有效地建立一個“安全島”,為設計人員提供可靠的基礎,以在醫療,工業和汽車應用中實施更復雜的操作。為了消除潛在的常見故障模式,設計團隊將芯片組定向為彼此90°,并引入了處理器時序的延遲。該芯片可在高達200 MHz的頻率下運行,并可運行32 MB的閃存。

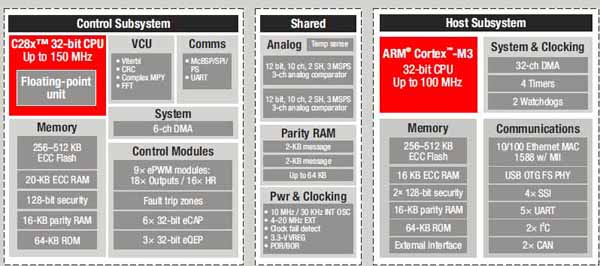

對于具有特殊要求的應用 - 例如,計算密集型操作或大量信號處理 - 異構MCU可以提供更好的解決方案。異構MCU包含不同類型的處理器。它可能具有通用CPU以及數字信號處理器(DSP)和/或專用于浮點運算的處理器。例如,TI的Concerto異構多核MCU結合了C28x 32位CPU和ARM Cortex M3 32位CPU來優化子系統(圖1)。 C28管理控制子系統,提供高達150 MHz的浮點運算。同時,ARM Cortex處理通信,邏輯和排序/監控,速度高達100 MHz。 MCU在閃存和RAM上都集成了錯誤檢測功能,以及帶有多個系統看門狗的內置時鐘監控功能。

圖1:異構多核MCU,如Concerto包含不同的內核,可為每項任務提供最佳解決方案。

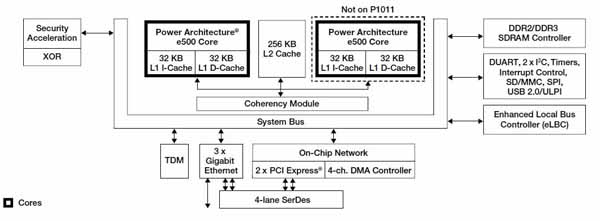

真正的多核MCU需要的不僅僅是具有共享內存的多個內核。為了實現有效的并行處理,架構必須確保每個CPU都在最新的可能數據上運行。在雙核MCU中,每個CPU都有一個專用的I(L1)高速緩存,但所有CPU共享一個2級(L2)高速緩存(圖2)。挑戰在于確保如果CPU1更新其L1緩存中的變量,CPU2將使用正確的信息,而不是其L1緩存先前從L2緩存中獲取的舊數據。設計通常使用各種名稱已知的硬件監視器來完成此操作,包括一致性模塊或簡單地說是窺探器。例如,當CPU 1將變量保存到其L1高速緩存時,一致性模塊注冊該更改并使CPU2的L1高速緩存中的數據無效。當CPU2嘗試訪問該位置時,它無法并且必須轉到L2緩存以獲取新數據。

圖2:來自飛思卡爾的QorIQ系列功能一個一致性模塊,用于監控每個CPU的I級緩存的更改,以確保每個核心都運行最新的數據。

飛思卡爾半導體的QorIQ P2平臺系列通信處理器基于雙e500 Power Architecture內核,每個CPU具有雙32 KB L1高速緩存,另外還有256 KB二級高速緩存。用戶可以選擇在兩個內核之間對L2緩存進行分區,也可以將其配置為存儲內存或SRAM。 P2020評估板,名為P2020COME-DS-PB-ND,使工程師能夠熟悉飛思卡爾雙核MCU的復雜性。 Digi-Key網站還提供雙核QorIQ產品的產品培訓模塊。

功能并行與數據并行

硬件只是一個開始。多核MCU的最大好處是程序員可以利用軟件最大限度地提高工作效率的方式。有多種方法可以編程多核MCU。在對稱多處理(SMP)中,也許是最常見的方法,所有CPU都可以訪問公共內存空間并由單個操作系統運行。 CPU通過共享內存中的變量進行通信。任何CPU都可以運行任何進程,但通常在任何給定時間都不會在CPU之間共享進程。

非對稱多處理(AMP)提供更多自由度。在AMP中,可以將特定CPU分配給某些進程以實現最佳性能。非對稱體系結構甚至可以在不同的處理器上運行不同的操作系統,在核心處理和時間敏感操作上運行實時操作系統(RTOS),而通用核心在Linux上運行。

多核MCU的主要優點之一是并行處理能力。并行處理可分為功能并行處理和數據并行處理。功能并行性涉及將任務分解為單個運算符。不同處理器執行不同功能。這是一種強大的技術,但不是多核方法中真正的肌肉所在。

數據并行性提供了最大的性能提升。它涉及將數據劃分為由不同核心處理的各個部分。這是一種功能強大的技術,但由于CPU通過共享內存進行通信,因此同步對于確保CPU以正確的順序和正確的數據進行操作至關重要。

多線程或fork/join并行性提供了一種確保同步的方法。系統將處理劃分為線程,在CPU之間拆分數據,每個CPU在其數據塊上運行相同的代碼。當線程完成其操作時,它們重新組合以產生結果。在完成所有線程之前,操作不會結束,因此這種方法可確保同步。

使用先進先出(FIFO)緩沖區提供了另一種同步方法。當CPU通過FIFO進行通信時,如果它是空的,它們只能寫入它。數據強制執行優先級 - 如果緩沖區已滿,則進程后期的CPU無法寫入。它必須輪流等待。

互斥(互斥)鎖提供了更復雜的同步方法。通過硬件實現,互斥鎖可確保在任何給定時間只有一個CPU擁有共享變量的所有權。當給定線程開始其操作時,它讀取變量并設置鎖定,這阻止其他線程訪問信息。當操作結束時,線程釋放鎖定,以便其他人可以訪問它。

特別是在并行處理方面,多核MCU為嵌入式設計提供了強大的解決方案。但是,它們必須經過精心設計和編程。線程越多,該過程就越具有挑戰性。錯誤可能導致系統死鎖,循環結束,甚至產生可能的結果,這些結果意外地依賴于首先完成哪個線程。

硬件設計有其自身的挑戰。雖然解決方案功能強大,但重要的是要意識到它們不一定是給定應用程序的最佳解決方案。用戶需要考慮處理器功能和帶寬限制 - 與內核一樣快,他們都將使用相同的通信總線,ADC和其他資源。

總體而言,多核MCU為各種嵌入式設計挑戰提供了有用的選擇。存在用于簡化嵌入式設計和編程的工具。通過訪問它們并密切關注測試和驗證,設計團隊可以獲得高性能和經濟的價格點,并加快產品上市速度。

-

mcu

+關注

關注

146文章

17316瀏覽量

352319 -

嵌入式

+關注

關注

5091文章

19176瀏覽量

307032 -

操作系統

+關注

關注

37文章

6889瀏覽量

123627

發布評論請先 登錄

相關推薦

多核嵌入式系統存在的局限性?怎么解決這些問題?

多核MCU可用于簡化嵌入式設計 精選資料推薦

嵌入式多核程序設計資料分享

中國首顆ARM+RISC-V異構多核MCU伴隨IAR在上海國際嵌入式展亮相

嵌入式異構多核的片上通信架構設計

NI LabVIEW 8.6 全面簡化嵌入式系統原型構造與發

嵌入式多媒體應用的多核編程框架

嵌入式多媒體多核應用軟件設計解析

嵌入式多媒體多核應用軟件設計框架

多核MCU可用于簡化嵌入式設計

嵌入式linux和物聯網,嵌入式Linux或RTOS:用于物聯網

嵌入式linux和物聯網,嵌入式Linux或RTOS:用于物聯網

多核MCU可用于簡化嵌入式設計

多核MCU可用于簡化嵌入式設計

評論