2018年12月,在美國舊金山或華盛頓哥倫比亞特區的召開的IEEE國際電子元件會議(International Electron Devices Meeting,縮寫:IEDM)剛剛結束。

在每一界的IEDM上,全球工業界與學界的管理者、工程師和科學家將會聚集在一起討論納米級CMOS晶體管技術、先進內存、顯示、感測器、微機電系統元件、新穎量子與納米級規模元件、粒子物理學現象、光電工程、功率與能量收集元件、高速元件、制程技術、元件模型化與模擬。 會議也涵蓋硅、化合物、有機半導體與新興材料系統元件的討論和簡報。

在本次的IEDM上,我們看到以下新技術趨勢:

三星力推下一代3nm GAA-FET

在2018年五月份的Samsung Foundry Forum論壇上,韓國半導體巨頭宣布了他們的工藝路線圖。按照三星規劃,其將首次采用EUV光刻(極紫外光刻)的7nm LPP(Low Power Plus)工藝技術將于今年下半年投產。關鍵IP正在研發中,明年上半年完成;7nm之后將會是其5nm LPE(Low Power Early),能實現更大面積的電路縮放和更低的功耗;在這之后,便會迎來4nm LPE/LPP制程工藝,這也是三星最后一次應用高度成熟和行業驗證的FinFET立體晶體管技術。

三星路線圖

在3nm的時候,三星計劃引入了Gate-All-Around(簡稱GAA),也就是環繞柵極。相比于現在的FinFET Tri-Gate三柵極設計,這個重新設計了底層結構的晶體管能克服當前技術的物理、性能極限,增強柵極控制,獲得性能大大提升。在日前的IEDM上,三星晶圓代工業務負責人表示,三星已經完成了3nm工藝技術的性能驗證,并且在進一步完善該工藝,目標是在2020年大規模量產。

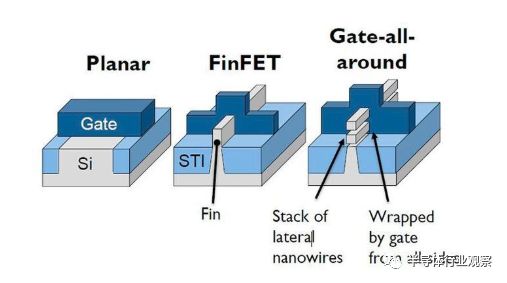

所謂Gate-all-around (GAA) ,有時候被稱作橫向納米線場效應管。這是一個周邊環繞著 gate 的 FinFet 。按照專家的觀點, GAA 晶體管能夠提供比 FinFet 更好的靜電特性,可滿足某些柵極寬度的需求,這主要體現在同等尺寸結構下,GAA溝道控制能力增強,因此給尺寸進一步微縮提供了可能;傳統Finfet的溝道僅三面被柵極包圍,而GAA以納米線溝道設計為例,溝道的整個外輪廓都被柵極完全包裹住,這就意味著柵極對溝道的控制性能就更好。

從平面晶體管到GAA的演進

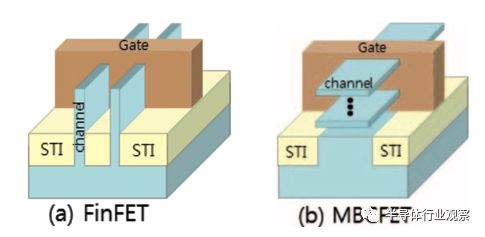

從Cadence博主Paul McLellan的文章我們可以看到,三星研究人員將將他們采用全環柵(GAA)晶體管設計的3nm CMOS技術叫做多橋通道(MBC)架構。據介紹,這個由納米片(nanosheets)的水平層制成的溝道完全被柵極結構包圍。

三星聲稱,這種技術具有高度可制造性。因為它利用了該公司現有的約90%的FinFET制造技術,而只需要少量修改過的光掩模。他們用它構建了一個功能齊全的高密度SRAM宏。他們表示,該工藝具有出色的柵極可控性(65 mV / dec亞閾值擺幅(subthreshold swing)),這比公司的FinFET技術高31%,且因為納米片通道寬度可通過直接圖案化來改變,這就給設計提供了靈活性。

在大家為晶體管的未來感到擔憂的時候,三星給大家做了一個好指引。

IMEC發布16nm DRAM

與CPU等芯片相比,DRAM內存在20nm節點之后也放緩了速度,線寬減少越來越困難,40nm工藝的DRAM內存芯片線寬減少約為5-10nm,20nm工藝的線寬減少就只有2-3nm了,更先進的工藝減少線寬就更困難了。能量功耗,帶寬,延遲和制程升級成為了DRAM業者關注的重要問題,這也讓廠商舉步維艱。

以三星和SK海力士為例,據***媒體Digitimes在今年五月的報道,韓國兩大存儲巨頭的18nm制程雙雙出現了良率問題,并遭到數據中心客戶退貨,且在改善前將暫緩出貨,受到影響的業者包括亞馬遜及阿里巴巴、騰訊、華為等大廠,***地區業者也陸續于近1~2周內獲得訊息。報道進一步指出,三星18nm制程并非第一次傳出質量疑慮,先前已修改過2次設計,原本業界以為第3次改良將可安全過關,不過高階服務器產品應用于數據中心的要求較為嚴格,環境測試也較為嚴峻,在DRAM制程持續微縮下,導致符合規格的產品良率較難穩定控制。

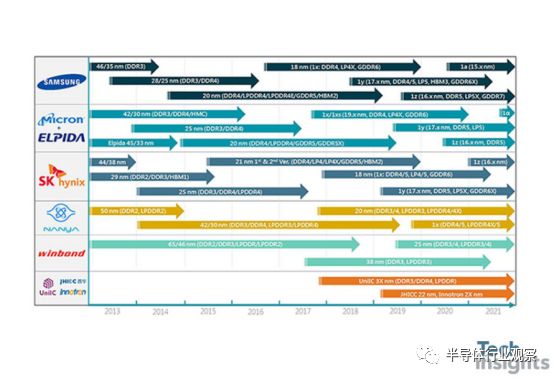

在18nm已經如此艱難,但專家認為20nm以下,DRAM工藝預計將經過兩到三次的技術迭代,可以稱之為1x nm,1y nm,1z nm。其中,1x nm位于16nm和19nm之間,1y nm則定義為14nm到16nm,1z nm則是12nm到14nm。隨著而來的晶體管泄漏電流等問題就成為了懸在開發者頭上的達摩克利斯之劍。

DRAM技術演進圖,幾乎所有廠商的1X、1Y和1Z路線圖都延期了

但IMEC的研究人員宣稱他們找到了新的解決方法。

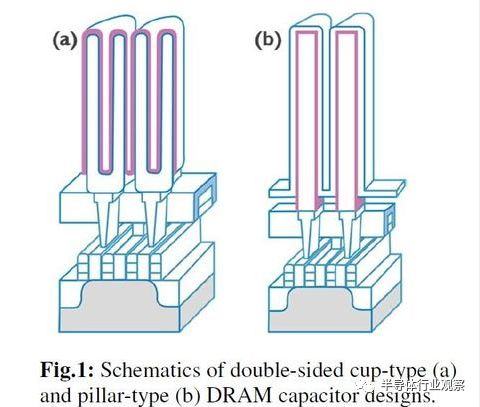

首先我們先看一下其原理。所有的DRAM存儲器都包括電容器—晶體管對的陣列,他們通過充放電將其數據作為電荷存儲在電容器中;電荷的存在表示“1”,不存在時是“0”。這些數字的操作是計算機編程的基礎。但由于空間限制,使得難以在Pitch內封裝足夠的電容,因此業界難以將DRAM擴展到16nm及更小的工藝制程。

IMEC研究人員則表示,他們使用了使用新的介電材料(SrTiO3或STO),并使用原子層沉積(ALD)工藝去Pattern,打造了11nm的柱狀電容。通過調整電容器和生長它的SrRuO3(SRO)外延模板的材料特性,研究人員實現了非常高的介電常數(k~118)和低漏電(±1V時10-7 A / cm2)。這意味著可以使用柱形電容器代替現有的杯形電容器,而不會在降低數據存儲能力方面付出太多代價。這些結果使STO電容器適用于16nm和更小DRAM的持續縮放。

IBM在多個新領域的探討

普通人對于IBM的了解,就是他們曾經的PC和Power處理器,但其實過去多年來,IBM在很多先進半導體科技上的研發領先于很多廠商,在本屆的IEDM2018上,他們也帶來多個對未來技術發展的想法分享:

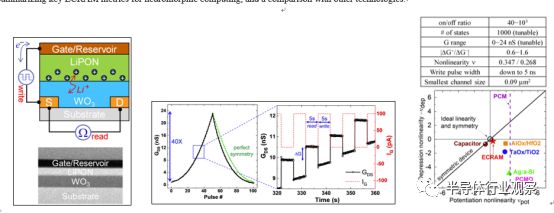

首先是Electrochemical Synaptic Cell。

按照IBM的說法,我們現在為神經形態計算研發的Synaptic Cell (如RRAM和PCM等非易失性存儲技術)具有非理想的切換特性(例如,不對稱的重量更新(asymmetric weight update),有限的耐用性(limited endurance)和高水平隨機性(elevated levels of stochasticity)或隨機行為(random behavior)))。

為解決這些問題,IBM研究人員將介紹一種新型可擴展電化學隨機存取存儲器(electrochemical random access memory,簡稱ECRAM)器件,該器件基于氧化鎢(WO3)中的鋰(Li)離子嵌入,可用作可擴展的synaptic cell。這些非易失性ECRAM顯示出高水平的開關對稱性和線性度,良好的數據保持能力,以及多達1,000個離散電導水平,這可用于大型存儲器陣列中的多級操作。

研究人員還展示了這個器件成功的高速編程能力。他們使用5ns脈沖寬度和300x300nm2 ECRAM器件。對于縮放的100x100nm2器件,預計具有1 fJ的超低開關能量。基于實驗數據的MNIST圖像識別模擬顯示96%的準確度。

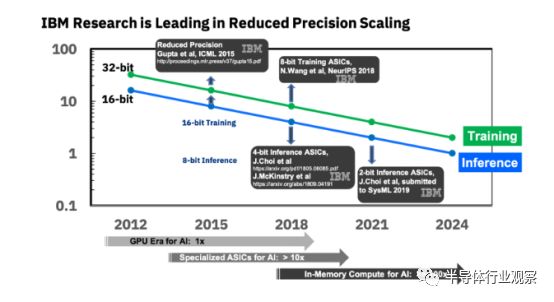

其次,解決內存計算的主要挑戰;

我們的特約撰稿人李飛在其文章《內存內計算,下一代計算的新范式?》中說到了“內存墻”問題,而IBM在IEDM 2018上帶來了解決基于PCM內存內計算的一個大挑戰——“精度有限”。他們提出了一種設備級解決方案,也就是他們所說的Proj-PCM。

據介紹,這個方案可以實現AI相關計算所需的標量乘法數學(scalar multiplication mathematics)的高精度(8位)和低功率(60 nW)。相變材料是高度非線性的,新穎的Proj-PCM器件采用所謂的projection segment(金屬電阻器),以便在讀取存儲器時穩定材料的電導(electrical conductance),從而降低噪聲和溫度漂移。他們構建了一個用于圖像識別的單層神經網絡,包括30個Proj-PCM設備并對其進行離線訓練,之后即使在高溫下也能表現出無差錯的模式識別性能。

這個方案具有存儲和處理數據的雙重功能,其單獨的架構調整可以將能耗降低90%以上,并且相變存儲器(PCM)可以獲得額外的性能提升。該屬性使其能夠執行計算,研究人員預測的PCM(Proj-PCM)使PCM在很大程度上不受電導變化的影響,從而實現比以前更高的精度。按照論文介紹,這個方案不但能夠以 8-bit 精度訓練深度學習模型,同時保持圖像、速度、文本數據集類別的模型精度。

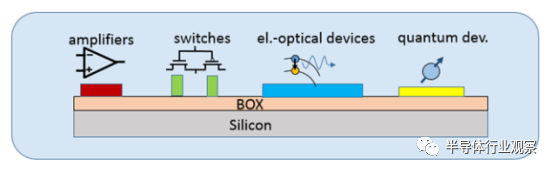

除此之外,IBM還在探索用III-V族材料代替Si溝道材料的方法。

他們表示,III-V材料提供了硅沒有的幾個優點:如較低的有效質量,較高的遷移率和直接的帶隙,這使它們更適合光子和隧道器件。硅已經并將繼續成為電子行業的首選半導體,因為Si豐富,低成本,堅固并且在高質量SiO 2氧化物方面提供理想的鈍化。為了結合兩者的優點,在Si上集成III-V材料具有很高的技術和經濟意義,并且已經被追求了多年。

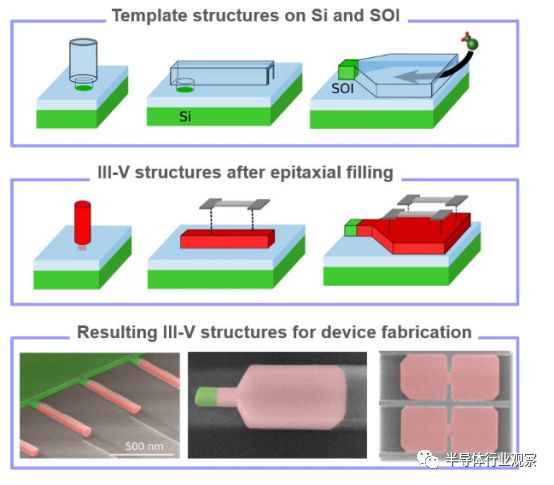

如下圖所示,與基于Si的電路緊密“聯系”的III-V器件可以提高系統性能,甚至可以實現新的應用領域,預期其系統制造成本將顯著低于分立芯片封裝方法。

Si上III-V材料和器件的各種應用空間的示意圖

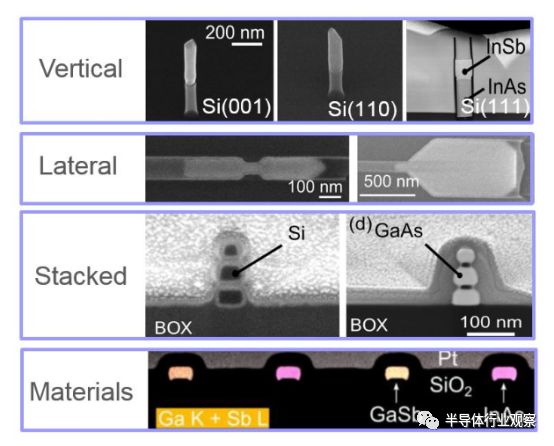

他們開發了一種新的外延生長方法,在在Si上沉積III-V材料,從而獲得良好的材料質量。最重要的一點是,該工藝與CMOS工藝兼容,這就是他們所謂的“模板輔助選擇性外延”(Template-Assisted-Selective-Epitaxy,縮寫TASE)工藝。

據介紹,IBM的這個工藝設計是為了將高遷移率材料集成成納米級別的sheets而設計的,他們也Si上集成了高性能InGaAs GAA nanosheet N-FETs。據報道,Nanosheets的厚度可以做到10nm,晶體管的柵極長度小于40nm,且柵極金屬環繞通道,以實現最佳的柵極控制。

Si上集成三五族材料的范例

這些器件具有出色的電流驅動能力(Ion =355μA/μm),以及72 mV / decade的亞閾值擺幅(subthreshold swing)。研究人員表示,通過縮放柵極長度/nanoshee尺寸可以進一步提高器件性能,且這些器件與當前的硅制造工具兼容。

Template-Assisted-Selective-Epitax

-

半導體

+關注

關注

334文章

27690瀏覽量

221645 -

IC

+關注

關注

36文章

5978瀏覽量

176056 -

電子元件

+關注

關注

94文章

1387瀏覽量

56669

原文標題:國外正在關注這些集成電路新技術

文章出處:【微信號:iawbs2016,微信公眾號:寬禁帶半導體技術創新聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

電子元件產業正在發展什么新技術詳細趨勢介紹

電子元件產業正在發展什么新技術詳細趨勢介紹

評論