物理優(yōu)化是Vivado實(shí)現(xiàn)流程中更快時(shí)序收斂的重要組成部分。 了解如何在Vivado中應(yīng)用此功能以交換運(yùn)行時(shí)以獲得更好的設(shè)計(jì)性能。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131442 -

交換

+關(guān)注

關(guān)注

0文章

32瀏覽量

16705 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66801

發(fā)布評論請先 登錄

相關(guān)推薦

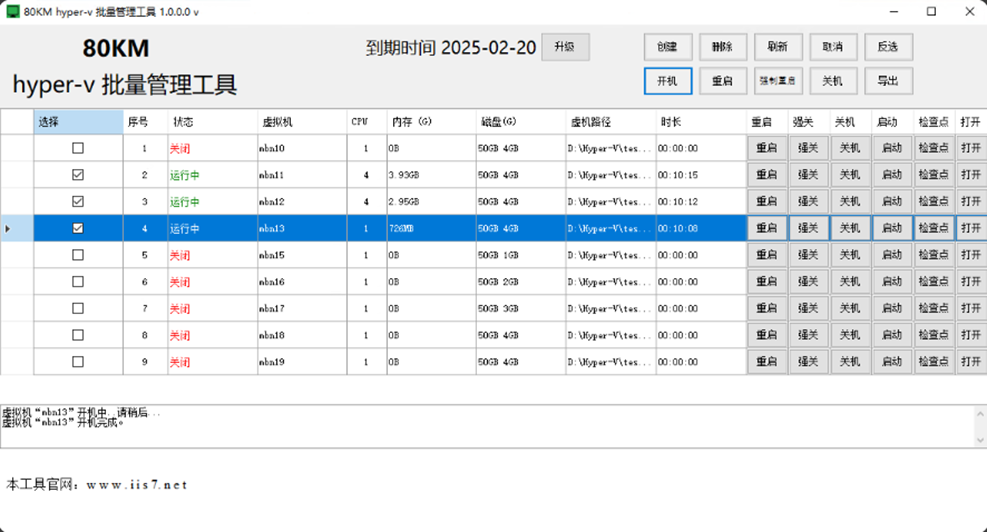

hyper v 顯卡,hyper-v顯卡:如何在虛擬機(jī)中配置和優(yōu)化顯卡性能

:如何在虛擬機(jī)中配置和優(yōu)化顯卡性能。 ? ?在虛擬化環(huán)境中,顯卡性能對于需要高圖形處理能力的應(yīng)用

光波導(dǎo)系統(tǒng)中光柵幾何結(jié)構(gòu)的優(yōu)化

| | 次我們強(qiáng)調(diào)了快速物理光學(xué)軟件VirtualLab Fusion分析光波導(dǎo)系統(tǒng)性能。這次我們在設(shè)計(jì)工作流程中處理一個(gè)密切相關(guān)的步驟: 在系統(tǒng)的耦合和擴(kuò)展區(qū)域中使用的光柵幾何結(jié)構(gòu)的優(yōu)化

發(fā)表于 12-20 10:27

仿真系統(tǒng)的性能優(yōu)化技巧

在現(xiàn)代工業(yè)和科學(xué)研究中,仿真系統(tǒng)扮演著越來越重要的角色。它們不僅能夠幫助我們預(yù)測復(fù)雜系統(tǒng)的行為,還能在沒有實(shí)際物理原型的情況下進(jìn)行實(shí)驗(yàn)和測試。然而,隨著仿真模型的復(fù)雜度增加,性能優(yōu)化成

SSM框架的性能優(yōu)化技巧 SSM框架中RESTful API的實(shí)現(xiàn)

SSM框架的性能優(yōu)化技巧 SSM(Spring + Spring MVC + MyBatis)框架的性能優(yōu)化是提升Java Web應(yīng)用性能的

光波導(dǎo)系統(tǒng)中光柵幾何結(jié)構(gòu)的優(yōu)化

快速物理光學(xué)軟件VirtualLab Fusion擁有分析光波導(dǎo)系統(tǒng)性能。這次我們在設(shè)計(jì)工作流程中處理一個(gè)密切相關(guān)的步驟: 在系統(tǒng)的耦合和擴(kuò)展區(qū)域中使用的光柵幾何結(jié)構(gòu)的優(yōu)化。

Virt

發(fā)表于 12-16 10:39

Vivado之實(shí)現(xiàn)布局布線流程介紹

一、前言 本文將介紹Vivado進(jìn)行綜合,以及布局布線的內(nèi)部流程,熟悉該流程后結(jié)合Settings中對應(yīng)的配置選項(xiàng),對于時(shí)序收斂調(diào)試將更具有針對性。 二、Implementation(實(shí)現(xiàn)) 實(shí)現(xiàn)

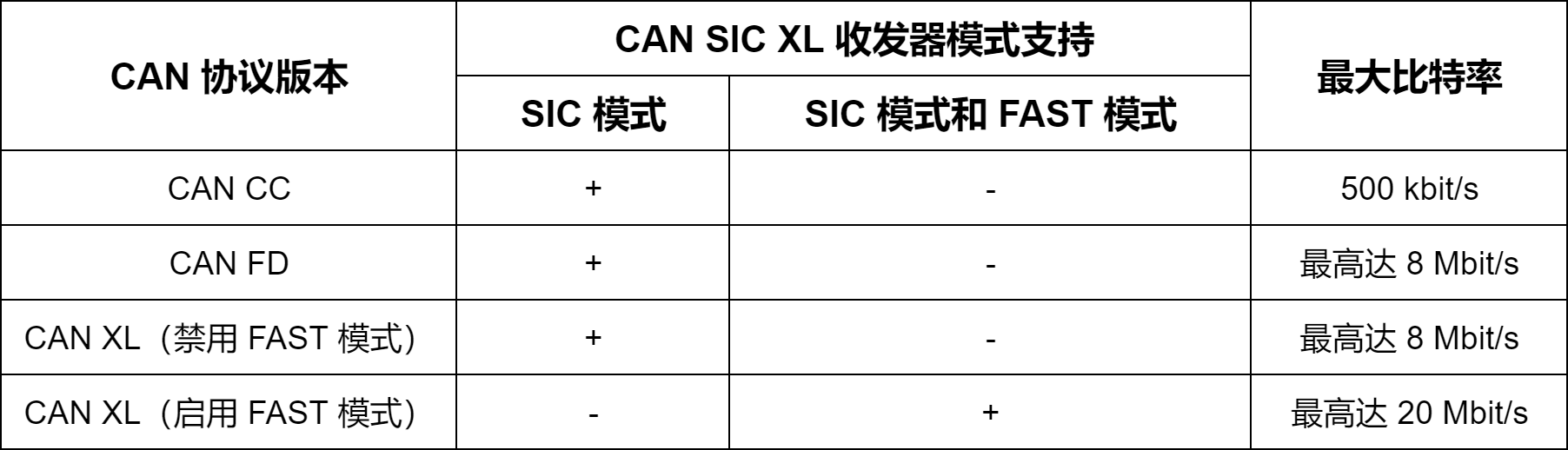

CAN XL物理層揭秘(下):物理層組合與兼容性

CAN XL網(wǎng)絡(luò)憑借物理層革新,在汽車電子和工業(yè)通信中占據(jù)重要地位。在上篇中,我們深入探討了CAN XL網(wǎng)絡(luò)中的物理層革新與優(yōu)勢(點(diǎn)擊回顧)。本文將繼續(xù)這一話題,重點(diǎn)介紹CAN XL網(wǎng)

如何在電路中優(yōu)化GND連接 GND在高頻應(yīng)用中的挑戰(zhàn)

在電路中優(yōu)化GND連接以及應(yīng)對GND在高頻應(yīng)用中的挑戰(zhàn),是確保電路性能穩(wěn)定、減少干擾和噪聲的關(guān)鍵環(huán)節(jié)。以下是對這兩個(gè)方面的介紹: 一、優(yōu)化G

如何通過OSI七層模型優(yōu)化網(wǎng)絡(luò)性能

七層模型的各個(gè)層次,可以顯著提升網(wǎng)絡(luò)性能。以下是通過OSI七層模型優(yōu)化網(wǎng)絡(luò)性能的具體方法: 一、物理層優(yōu)化

AI大模型的性能優(yōu)化方法

AI大模型的性能優(yōu)化是一個(gè)復(fù)雜而關(guān)鍵的任務(wù),涉及多個(gè)方面和策略。以下是一些主要的性能優(yōu)化方法: 一、模型壓縮與優(yōu)化 模型蒸餾(Model D

優(yōu)化 FPGA HLS 設(shè)計(jì)

優(yōu)化 FPGA HLS 設(shè)計(jì)

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設(shè)計(jì)性能。

介紹

高級設(shè)計(jì)能夠以簡潔的方式捕獲設(shè)計(jì),從而

發(fā)表于 08-16 19:56

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

本文介紹了在 AMD Vivado? Design Tool 中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的過程中要把具體步驟映射到相應(yīng)的 DFX 非工程模式的步驟,這樣才能更好地理解整個(gè)流程的運(yùn)行

鴻蒙語言ArkTS(更好的生產(chǎn)力與性能)

可以傳遞類型D的變量,這種靈活性可能不符合開發(fā)者的意圖,容易帶來程序行為的正確性問題。另外,由于類型D和類型C布局不同,那么foo中對c.s這個(gè)屬性訪問就不能被優(yōu)化成根據(jù)固定偏移量訪問的方式,從而給運(yùn)行時(shí)性能造成瓶頸。

發(fā)表于 02-17 15:56

如何在Vivado中應(yīng)用物理優(yōu)化獲得更好的設(shè)計(jì)性能

如何在Vivado中應(yīng)用物理優(yōu)化獲得更好的設(shè)計(jì)性能

評論