聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

視頻

+關注

關注

6文章

1956瀏覽量

73062 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131439 -

調試

+關注

關注

7文章

589瀏覽量

34030

發布評論請先 登錄

相關推薦

ZYNQ基礎---AXI DMA使用

Xilinx官方也提供有一些DMA的IP,通過調用API函數能夠更加靈活地使用DMA。 1. AXI DMA的基本接口 axi dma IP的基本結構如下,主要分為三個部分,分別是控制axi

如何進行電子連接器的測試與驗證

電子連接器的測試與驗證是確保其性能和質量的關鍵步驟。以下是對電子連接器進行測試與驗證的方法: 一、測試與驗證的目的 電子連接器的測試與驗證旨

調試Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作怎么解決?

我正在調試Xilinx Zynq + ADS58C48,ADC使用的是LVDS模式,ADC不能正常工作。有以下幾點問題:

1)通過Xilinx FPGA差分原語輸給ADC一個10MHz的差分時

發表于 12-10 07:34

AMBA AXI4接口協議概述

AMBA AXI4(高級可擴展接口 4)是 ARM 推出的第四代 AMBA 接口規范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導體產業首個符合 AXI4 標準的即插即用型 IP 進一步擴展了 AMD 平臺

解決驗證“最后一公里”的挑戰:芯神覺Claryti如何助力提升調試效率

過程中必不可少的一環,它幫助工程師找到問題的根源并進行優化。隨著設計復雜性的提升,調試作為驗證的“最后一公里”正面臨越來越多的挑戰。如何有效提升調試效率,已成為行

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

引言由于芯片設計復雜度的提升、集成規模的擴大,以及產品上市時間要求的縮短,使得設計驗證變得更加困難。特別是在多FPGA環境中,設計調試和驗證的復雜性進一步增加,傳統的調試手段難以滿足對

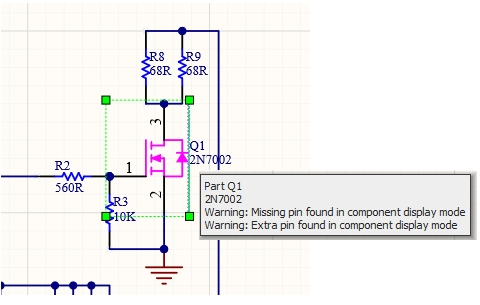

對元件顯示模式下發現的驗證錯誤進行故障排除

對原理圖進行電氣規則檢查時的驗證錯誤進行故障排除,例如,“Missing pin found in component display mode”或“Extra pin found in component display mo

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

NVMe AXI4 Host Controller IP可以連接高速存儲PCIe SSD,無需CPU,自動加速處理所有的NVMe協議命令,具備獨立的數據寫入和讀取AXI4接口,不但適用高性能、順序

有關PL端利用AXI總線控制PS端DDR進行讀寫(從機wready信號一直不拉高)

,DDR就不會拉高wready信號,驗證如圖所示,必須你首先給wvalid信號,wready信號才會拉高

情形二:如果設置為AXI3,如圖所示

經過驗證發現,最后DDR會一開始就拉高wready信號

發表于 05-31 12:04

SoC設計中總線協議AXI4與AXI3的主要區別詳解

AXI4和AXI3是高級擴展接口(Advanced eXtensible Interface)的兩個不同版本,它們都是用于SoC(System on Chip)設計中的總線協議,用于處理器和其它外設之間的高速數據傳輸。

FPGA通過AXI總線讀寫DDR3實現方式

AXI總線由一些核心組成,包括AXI主處理器接口(AXI4)、AXI處理器到協處理器接口(AXI4-Lite)、

發表于 04-18 11:41

?1321次閱讀

PCIe-AXI-Cont用戶手冊

PCIe-AXI-Controller兼容PCI Express base Specification Revision 3.1,實現PCIe PHY layer,Data link layer以及

發表于 02-22 09:15

?3次下載

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

PCIe-AXI-Controller兼容PCI Express Base Specification Revision 3.1,實現PCIe PHY Layer,Data Link Layer以及

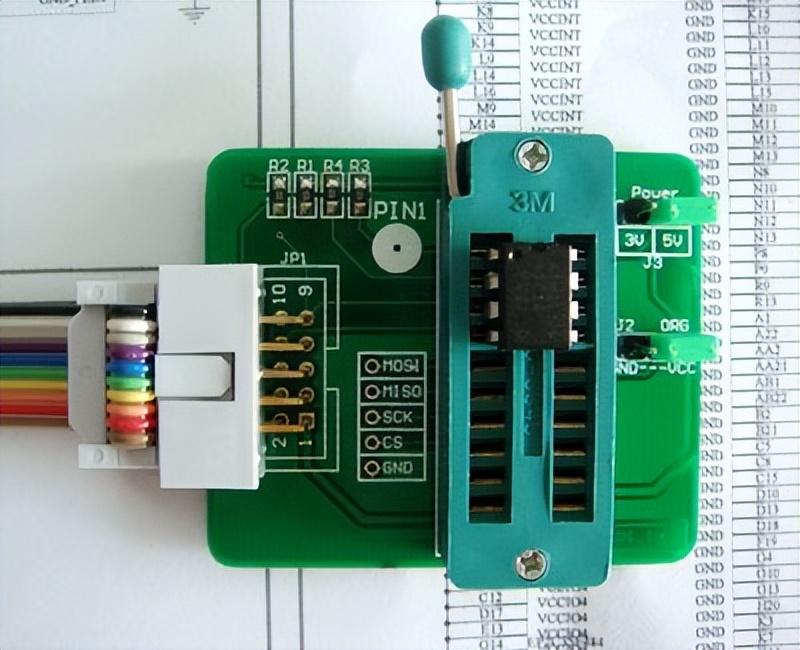

如何使用Xilinx AXI進行驗證和調試

如何使用Xilinx AXI進行驗證和調試

評論