線寬越寬抗干擾能力越強,信號質量越好(趨膚效應的影響)。但同時又要保證50Ω特征阻抗的要求。正常的FR4板材,表層線寬6MIL阻抗為50Ω。這個顯然不能滿足高速模擬輸入的信號質量的要求,所以我們一般采用挖空GND02,讓其參考ART03層。這樣差分信號可以算到12/10,單線可以算到18MIL。(注意線寬超過18MIL再加寬就沒有意義了)

圖中高亮為綠色的CLINE為參考ART03層的單線和差分高速模擬輸入。在這樣做的同時還要做一些細節處理:

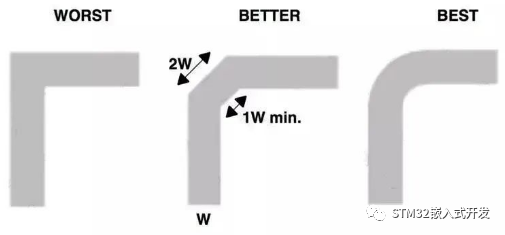

(1)TOP層模擬部分需要包地處理,如上圖。需要注意的是包地銅皮到模擬輸入CLINE的距離,需要做到3W,也就是銅皮邊沿到CLINE的AIRGAP為線寬的兩倍。根據一些電磁理論計算和仿真,PCB板上信號線的磁場和電場主要是分布在3W范圍之內的。(受周圍信號干擾噪聲小于等于1%)。

(2)模擬區域的正片層的GND鋪銅也需要與周圍的數字區域隔離,即所有層隔離。

(3)GND02的挖空處理,平常情況下我們一般是把這個區域全部挖空,這樣操作比較簡單,也沒有什么問題。但是考慮到細節方面或者說為了做的更好,我們可以只把模擬輸入走線部分的正下方挖空,當然是和TOP層一樣,3W區域。這樣既可以保證信號質量也能保證板子的平整度。處理結果如下圖:

這樣可以使高速模擬輸入信號的返回路徑在GND02層得到迅速回流。也就是模擬地回流路徑變短。

(4)在高速模擬信號的的周圍不規則的打大量的GND過孔,使模擬信號迅速回流。也可以吸收噪聲。

高速PCB信號走線的規則盤點

規則一:高速PCB信號走線屏蔽規則

在高速的PCB設計中,時鐘等關鍵的高速信號線,走線需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都會造成EMI的泄漏。建議屏蔽線,每1000mil,打孔接地。

規則二:高速信號的走線閉環規則

由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現一種失誤,即時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了閉環的結果,這樣的閉環結果將產生環形天線,增加EMI的輻射強度。

規則三:高速信號的走線開環規則

規則二提到高速信號的閉環會造成EMI輻射,然而開環同樣會造成EMI輻射。

時鐘信號等高速信號網絡,在多層的PCB走線的時候一旦產生了開環的結果,將產生線形天線,增加EMI的輻射強度。

規則四:高速信號的特性阻抗連續規則

高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射。也就是說,同層的布線的寬度必須連續,不同層的走線阻抗必須連續。

規則五:高速PCB設計的布線方向規則

相鄰兩層間的走線必須遵循垂直走線的原則,否則會造成線間的串擾,增加EMI輻射。

簡而言之,相鄰的布線層遵循橫平豎垂的布線方向,垂直的布線可以抑制線間的串擾。

規則六:高速PCB設計中的拓撲結構規則

在高速PCB設計中,線路板特性阻抗的控制和多負載情況下的拓撲結構的設計,直接決定著產品的成功還是失敗。

為菊花鏈式拓撲結構,一般用于幾Mhz的情況下為益。高速PCB設計中建議使用后端的星形對稱結構。

規則七:走線長度的諧振規則

檢查信號線的長度和信號的頻率是否構成諧振,即當布線長度為信號波長1/4的時候的整數倍時,此布線將產生諧振,而諧振就會輻射電磁波,產生干擾。

規則八:回流路徑規則

所有的高速信號必須有良好的回流路徑。盡可能地保證時鐘等高速信號的回流路徑最小。否則會極大的增加輻射,并且輻射的大小和信號路徑和回流路徑所包圍的面積成正比。

規則九:器件的退耦電容擺放規則

退耦電容的擺放的位置非常的重要。擺放不合理根本起不到退耦的效果。其原則是:靠近電源的管腳,并且電容的電源走線和地線所包圍的面積最小。

-

pcb

+關注

關注

4325文章

23159瀏覽量

399341 -

信號

+關注

關注

11文章

2804瀏覽量

77013

原文標題:PCB設計高速模擬輸入信號走線方法及規則

文章出處:【微信號:murata-eetrend,微信公眾號:murata-eetrend】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCB設計的直角走線,差分走線,蛇形線走線技巧

高速PCB設計中的走線技巧

高速信號PCB走線屏蔽設計方案

詳解PCB設計高速模擬輸入信號走線

詳解PCB設計高速模擬輸入信號走線

評論