基本的同步時序路徑約束

先讀文章:《時序邏輯電路的建立,保持時間裕量分析》

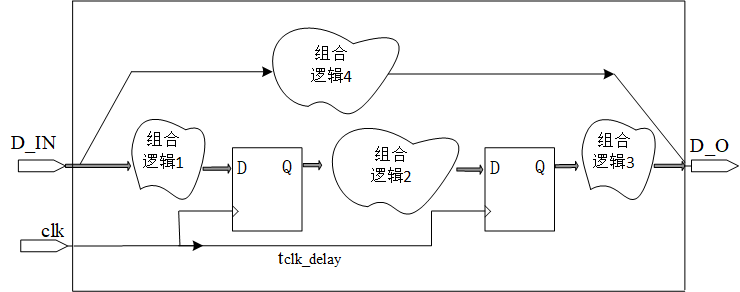

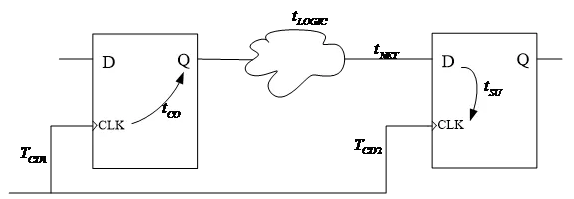

我們設計的同步時序電路示意圖如下。

從上面的示意圖可知,一個同步時序電路的時序路徑無非就是四種:

(1)從輸入端口到內部寄存器(從D_IN經過組合邏輯1,到第一個寄存器數據端口D)。

(2)從內部寄存器到內部寄存器(從第一個寄存器的Q端,經過組合邏輯2,到第二個寄存器的D端)。

(3)從內部寄存器到輸出端口( 從第二個寄存器的Q端,經過組合邏輯3,到輸出端口 D_O端)。

(4)從輸入端口到輸出端口(從D_IN經過組合邏輯4到達輸出端口D_O)。

先看路徑(2),從內部寄存器到內部寄存器。如文章《時序邏輯電路的建立,保持時間裕量分析》中的詳細描述,要滿足如下建立保持時間要求。

建立時間裕量:

tsetup_slack=tcycle-(tcq+tlogic) -tsetup+tclk_delay-tjitter>0

保持時間裕量:

thold_slack=tcq+tlogic-thold-tclk_delay-tjitter>0

對于EDA來說,tsetup(寄存器建立時間要求),tcq(寄存器輸出延時),thold(寄存器保持時間要求)它都是知道的。在忽略tjitter(時鐘抖動)的情況下,我們需要告訴EDA我們的時鐘周期,tcycle。如此EDA工具就會根據我們的給出的tcycle,去優化寄存器到寄存器之間的組合邏輯2的延時(tlogic)和tclk_delay,去滿足建立保持時間裕量要求。EDA也會根據我們給出的tcycle,去計算建立保持時間裕量。

因此此時我們只需要對時鐘進行約束,約束示例語句如下(在端口clk上創建的時鐘,周期為10ns)。

create_clock -period 10 [get_ports clk]

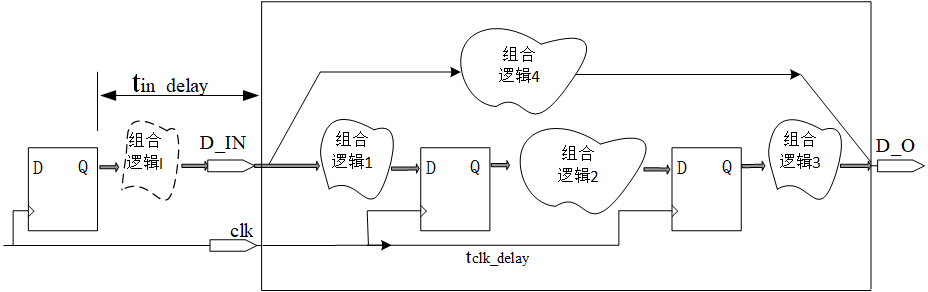

對于路徑(1),從輸入端口到內部寄存器(從D_IN經過組合邏輯1,到達第一個寄存器的數據端口D),我們需要把上一級的電路示意圖也畫出來。大家就明白了。如下圖所示,上一級的電路模型也可以等效為一個寄存器再通過一個組合邏輯電路。因此時序約束其實也就是變成了,從外部寄存器到內部寄存器之間的時序約束。

從圖中可以看到tin_delay(既數據到輸入端口的延時)其實等于上一級電路寄存器的輸出延時(tcq)加上一級組合邏輯的延時。

此時我們需要滿足的建立保持時間要求如下(tlogic1為組合邏輯1的延時)。

建立時間裕量

tsetup_slack=tcycle-tin_delay-tlogic1-tsetup+tclk_delay-tjitter>0

保持時間裕量

thold_slack=tin_delay+tlogic1-thold-tclk_delay-tjitter>0

同樣在忽略tjitter的情況下,我們只需要告訴EDA工具tcycle,tin_delay,如此EDA就會根據我們的條件去約束組合邏輯1的延時以及tclk_delay,從而使得電路滿足建立保持時間要求。

設置tcycle的方式,上面已經說過。設置輸入延時(tin_delay)的約束命令示例如下(-clock用于指定時鐘域,2表示設置輸入延時為2ns):

set_input_delay -clock clk 2 [get_ports D_IN]

對于輸入端口的完整約束示例如下:

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk 2 [get_ports D_IN]

當然對于輸入延時的定義也可以用 -max -min去分別定義一個最大值和最小值。在分析建立時間裕量時,EDA工具會用最大值去分析;在分析保持時間裕量時,EDA工具會用最小值去分析。定義示例如下:

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk -max 4 [get_ports D_IN]

set_input_delay -clock clk -min 1 [get_ports D_IN]

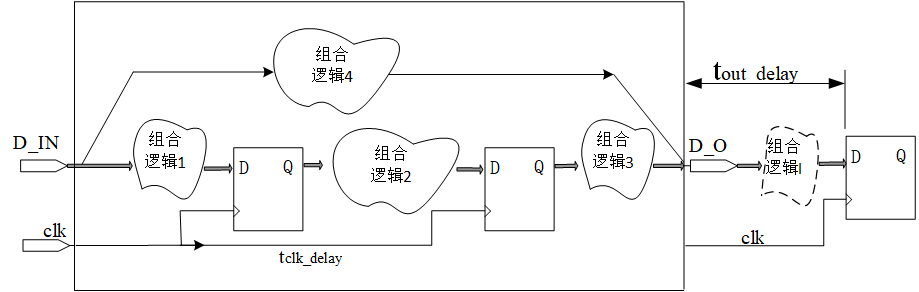

對于路徑(3),從內部寄存器到輸出端口(從第二個寄存器的Q端經過組合邏輯3到輸出端口D_O),同樣我們把它的下一級電路示意圖也畫出來。其下一級電路也是通過組合邏輯送到寄存器這種結構。問題也就可以等效為寄存器到寄存器之間的時序約束。

同樣在忽略時鐘抖動的情況下,我們需要告訴EDA工具數據從輸出端口到下一級電路寄存器的延時tout_delay和tcycle。此時EDA工具就會根據如下要求去優化組合邏輯3的延時tlogic3以及tclk_delay,以及計算靜態時序裕量。

建立時間裕量

tsetup_slack=tcycle-tout_delay-tlogic3-tsetup+tclk_delay-tjitter>0

保持時間裕量

thold_slack=tout_delay+tlogic3-thold-tclk_delay-tjitter>0

約束輸出延時(tout_delay)的示例如下(-clock 指定時鐘域)。

create_clock -name clk -period 10 [get_ports clk]

set_output_delay -clock clk 6 [get_ports D_O]

同樣,輸出延時也可以用 -max -min指定一個最大值和一個最小值。

create_clock -name clk -period 10 [get_ports clk]

set_output_delay -clock clk -max 6 [get_ports D_O]

set_output_delay -clock clk -min 2 [get_ports D_O]

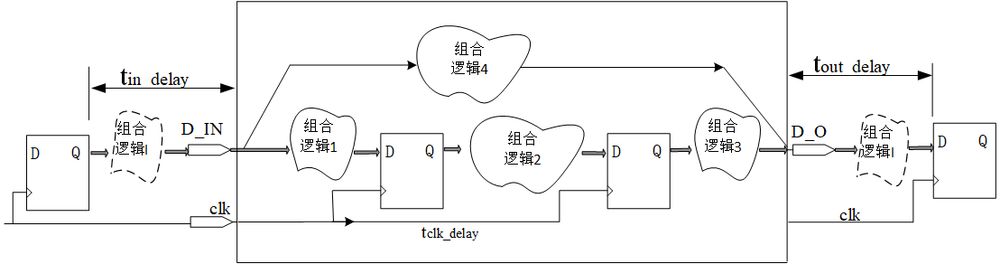

對于路徑(4)(從輸入端口經過組合邏輯4再到輸出端口),這時候我們必須聯合上下兩級電路來考慮。我們要先明確從上一級電路獲取數據的輸入延時tin_delay,以及其送到下一級電路的tout_delay。如此EDA工具才知道如何去做組合邏輯4的時序優化與做靜態時序計算。

此時需要滿足的時序要求如下:

建立時間裕量

tsetup_slack=tcycle-tin_delay-tout_delay-tlogic4-tsetup+tclk_delay-tjitter

保持時間裕量

thold_slack=tin_delay+tout_delay+tlogic4-thold-tclk_delay-tjitter

在忽略時鐘抖動的情況下,我們需要約束輸入延時,輸出延時。示例約束語句如下。

create_clock -name clk -period 10 [get_ports clk]

set_input_delay -clock clk 4 [get_ports D_IN]

set_output_delay -clock clk 1 [get_ports D_O]

-

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16586 -

同步時序

+關注

關注

0文章

12瀏覽量

7895

原文標題:基本的同步時序路徑約束

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

同步電路設計中靜態時序分析的時序約束和時序路徑

同步時序電路原理圖圖解 同步時序路徑約束要求

同步時序電路原理圖圖解 同步時序路徑約束要求

評論