這里我們以8-bit 的LFSR(線性反饋移位寄存器)做一個流水燈為例,介紹Vivado的基本使用。

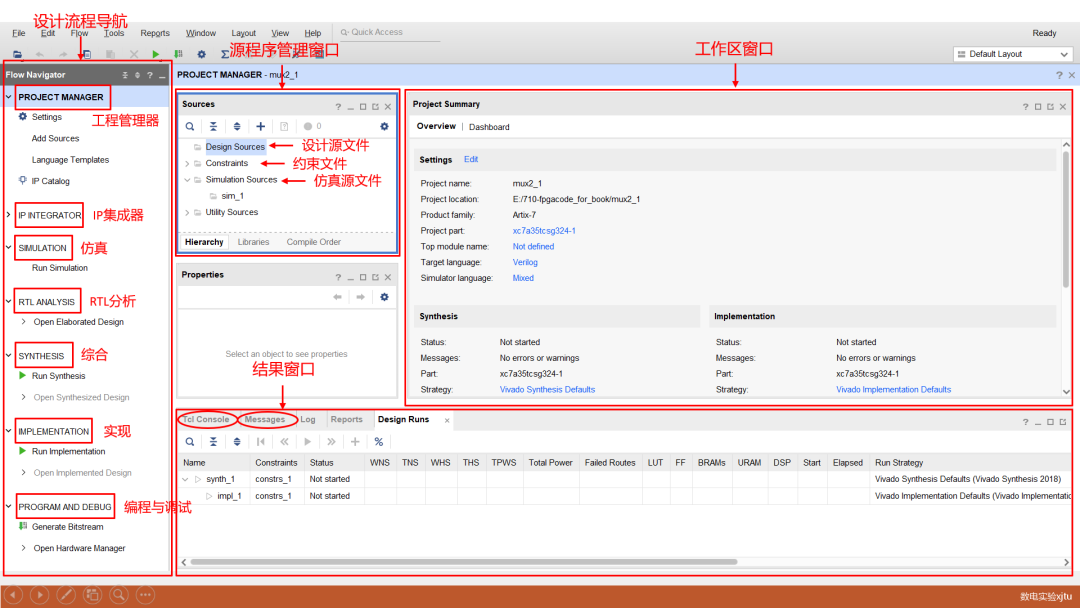

Vivado的基本使用過程大致如下:

一. 選則器件建立工程(或者是打開之前的工程)

三. 查看Schematic。

四. 添加TB文件,做功能仿真。

五. 添加約束文件,Synthesis(綜合)。

六. Implementation(實現(xiàn))并生成Bit文件。

七. 生成bit文件,下載到板子上。

一 . 新建工程

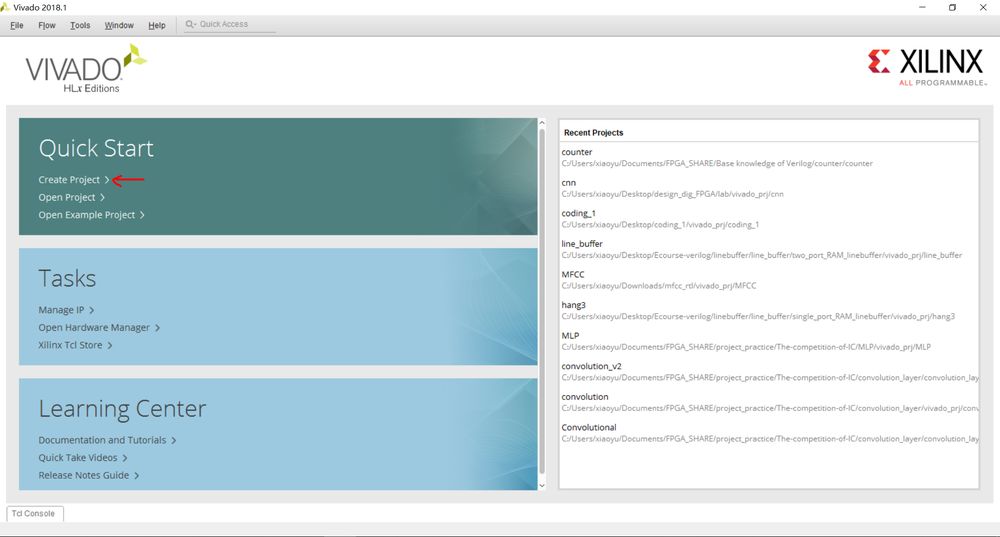

1. 打開Vivado工具,點擊如下 Create Project 。

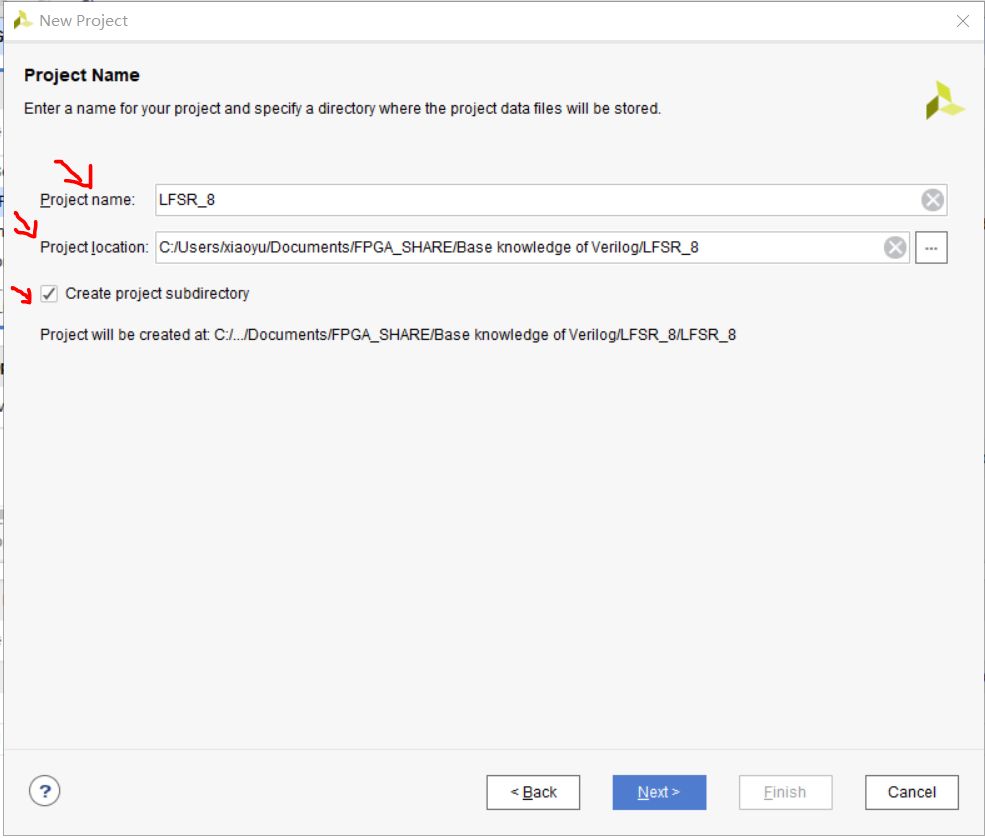

2. 點擊Next,出現(xiàn)如下圖所示界面,填入工程名字(Project name),以及選擇工程存放的目錄(Project location)。

選擇項Create project subdirectory就是在在你選擇的目錄下再生成一級與工程名字一樣的子目錄,工程將放在這個子目錄文件夾。

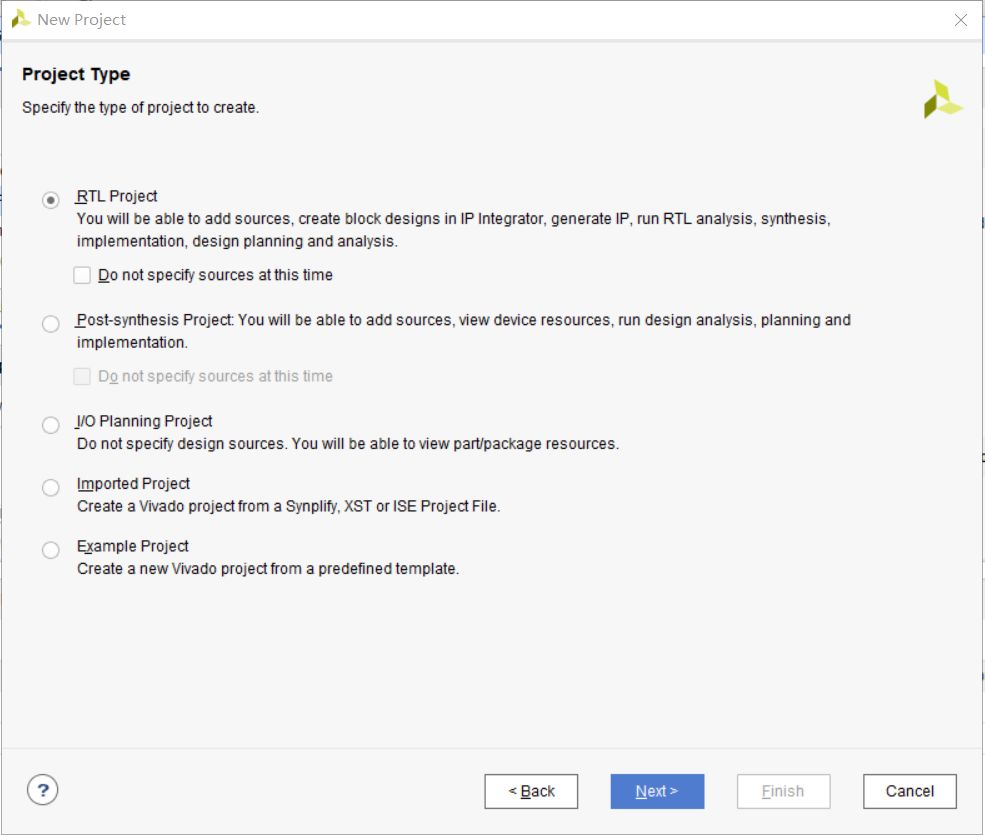

3. 選擇RTL Project,再點擊Next

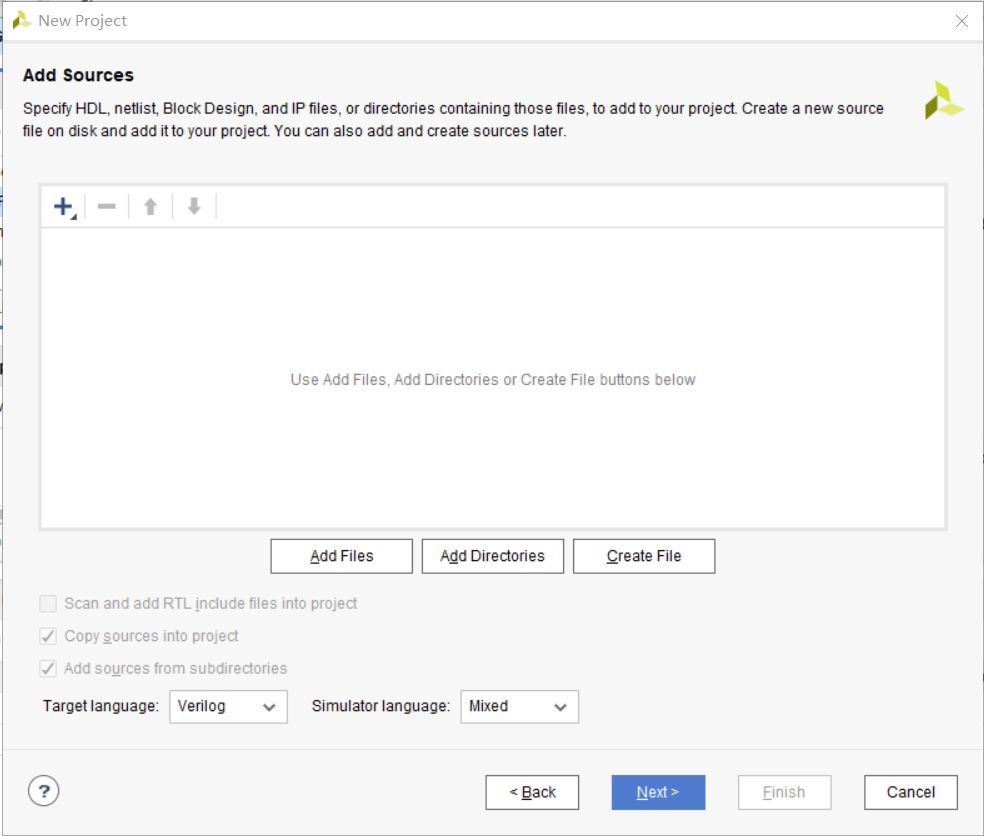

4. 在這里你可以添加已有的Verilog設(shè)計文件(Add Files),甚至是某個文件夾下的多個設(shè)計文件(Add Directories),或者新建Verilog文件(Create Files)。這里我們暫時不管,直接點擊Next。

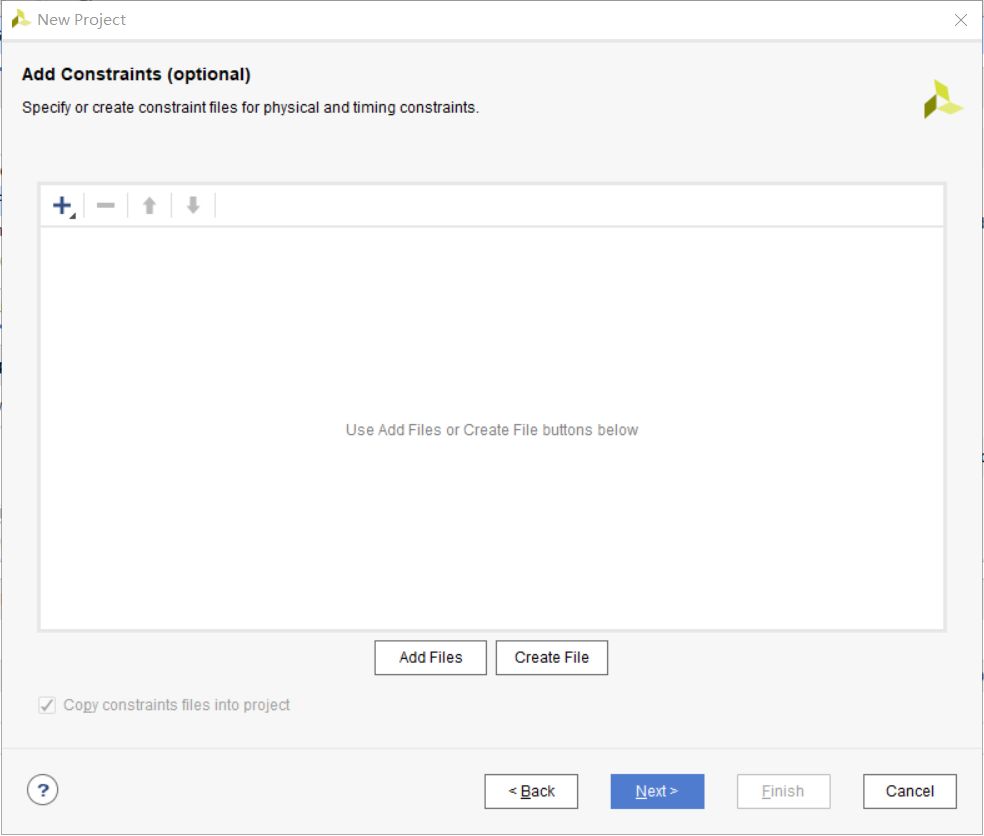

5. 同樣的,這里你可以添加或者新建約束文件(XDC文件)。這里我們暫時也先不管,直接點擊Next。

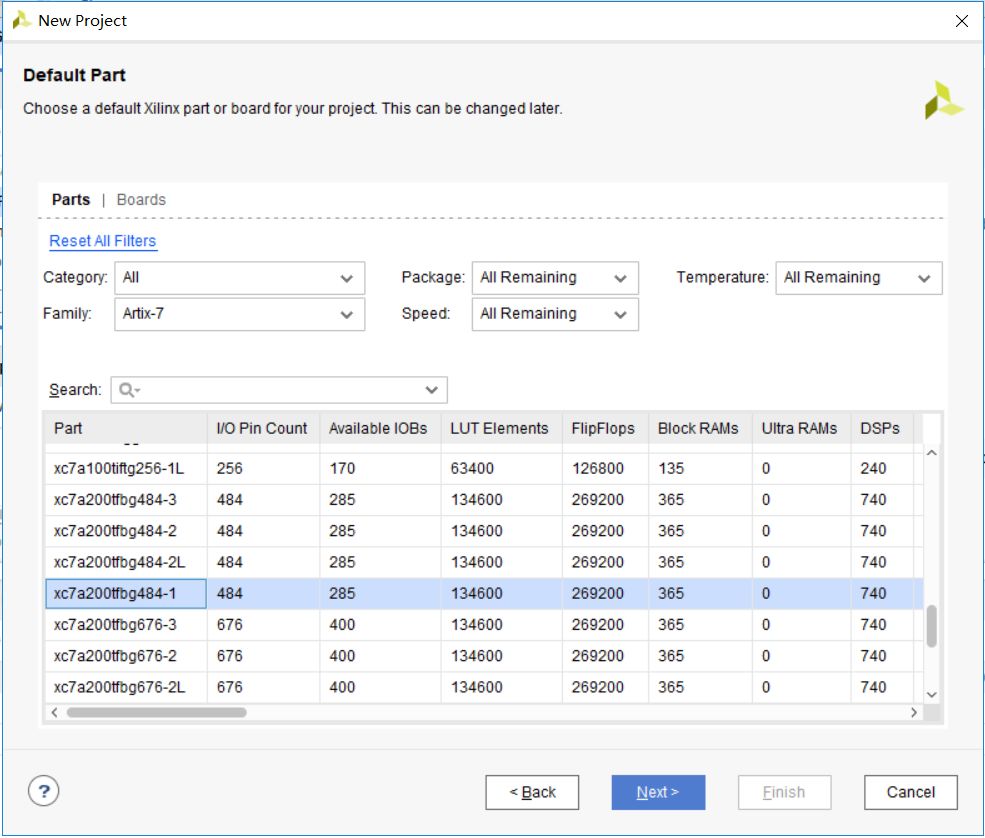

6. 選擇器件(FPGA板子)。這一步很重要,你必須選擇你要使用的板子型號。它有一些篩選項。

Category: 下對應(yīng)的是工業(yè)應(yīng)用,普通應(yīng)用,軍工/高可靠性應(yīng)用

Family:下對應(yīng)的就是所有的Xlinx公司有的FPGA芯片型號。

同時,還可以根據(jù)封裝類型(Package),溫度(Temperature), 速度(Speed)等信息去選擇。這里我選好了我要用的板子。點擊Next。

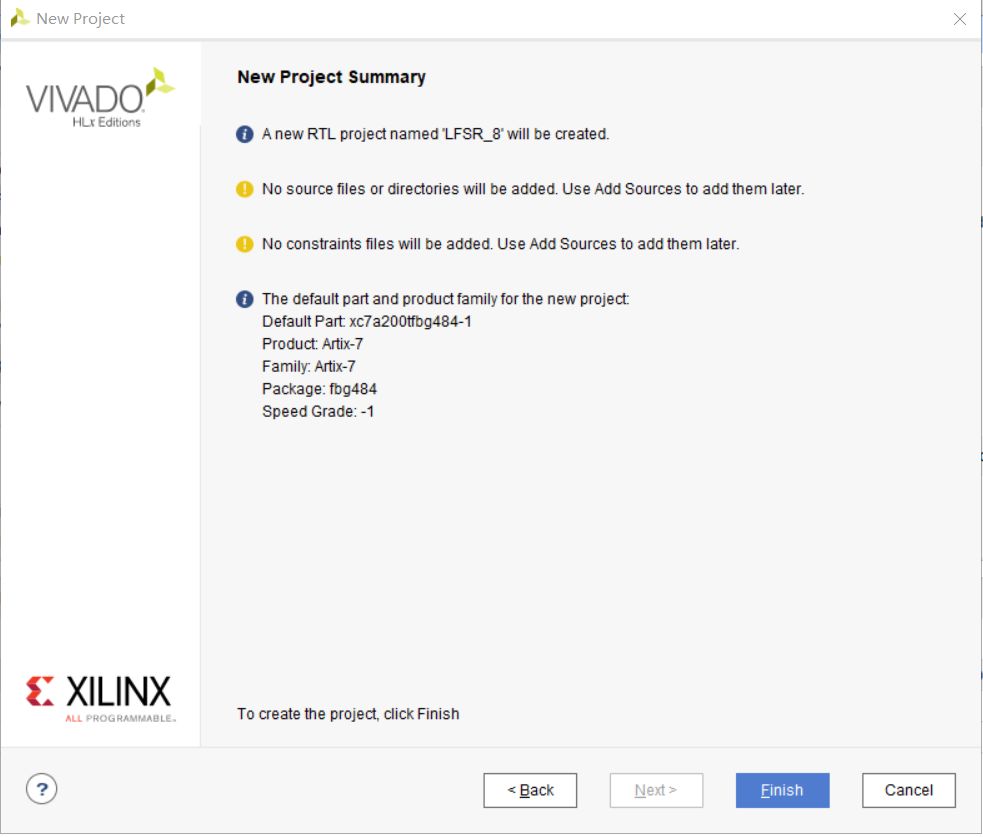

7. 所有的工程信息展示入下。確認沒問題,點擊Finish。如果覺得有問題可以點擊Back回退到上一步。

二. 添加電路描述Verilog文件

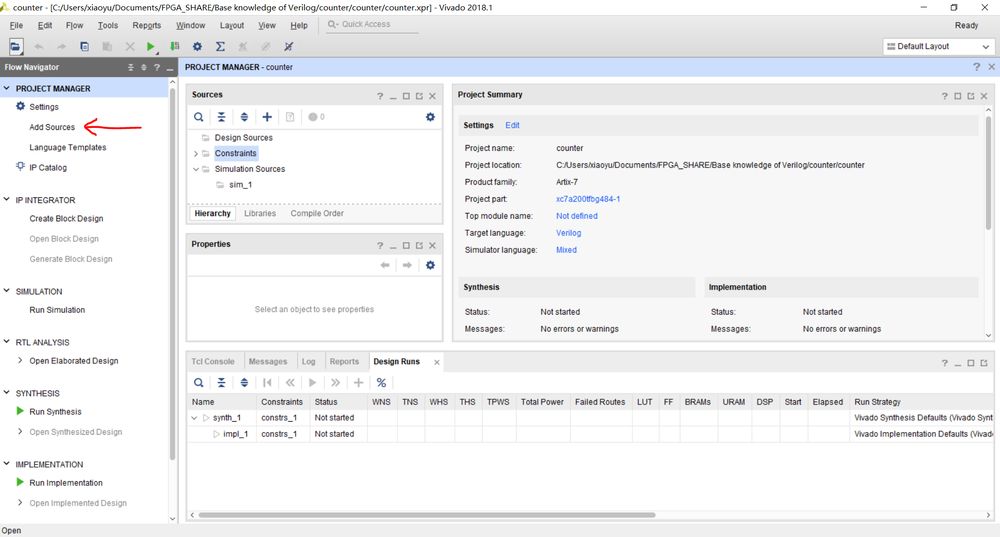

1. 在如下界面,點擊 Add->Source 。

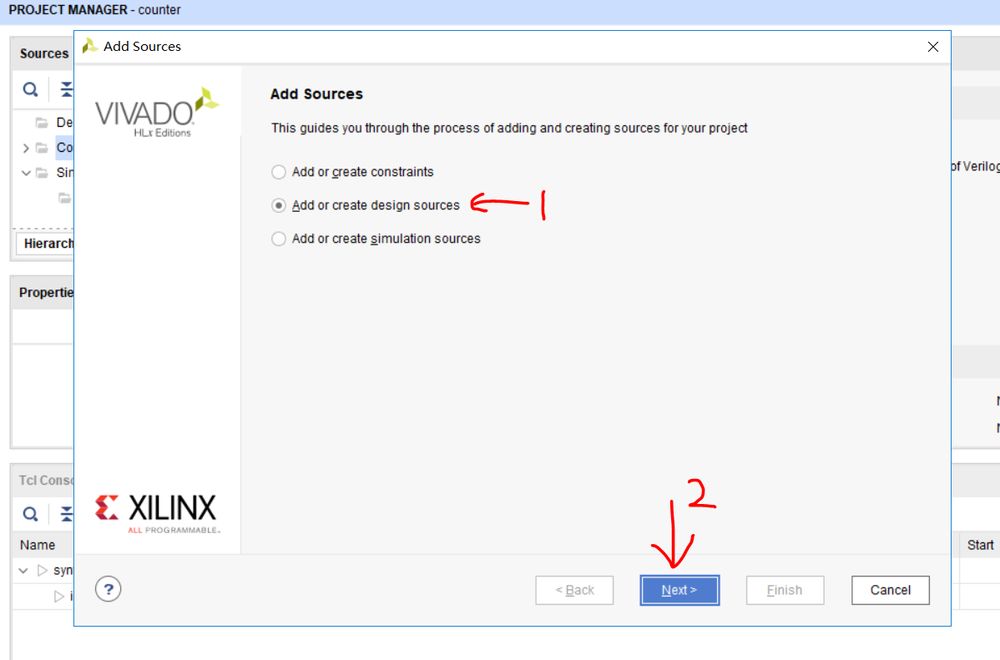

2.在彈出的頁面選擇Add or create design source 并點擊Next。

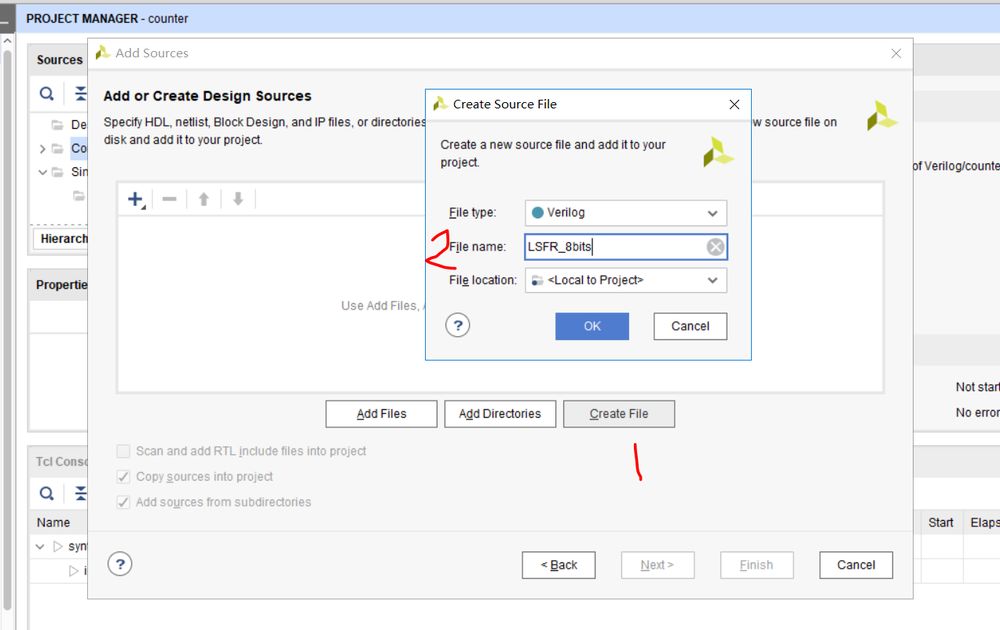

3.再在接下來彈出的頁面點擊Create File。此時如下圖,在2位置敲入文件文件名字,這里可以取為,LSFR_8bits , 再點擊OK。

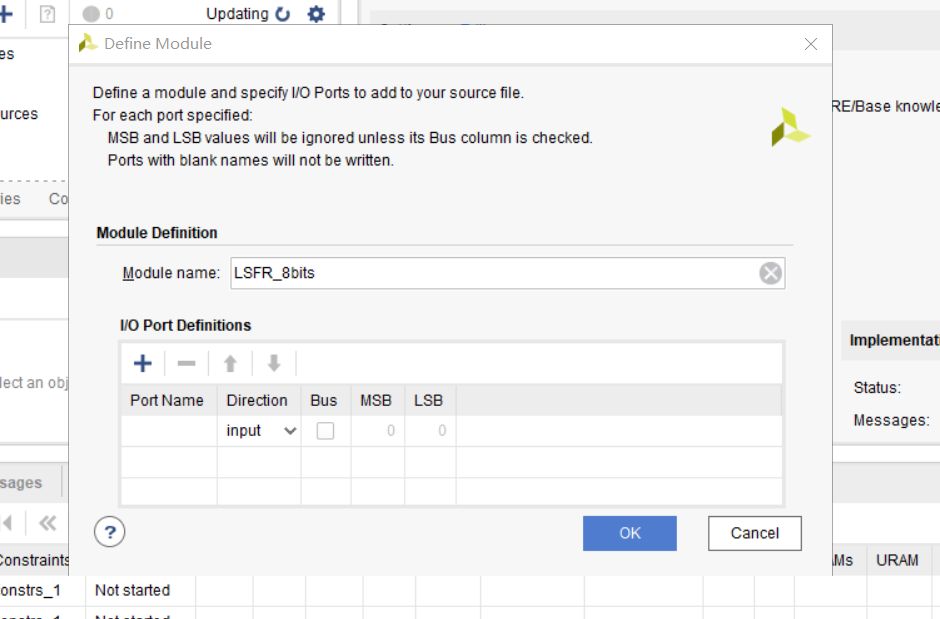

4. 點擊Finish后出現(xiàn)如下圖界面。這里你可以定義這個模塊的輸入輸出端口。這里我們先不定義,直接點擊OK。

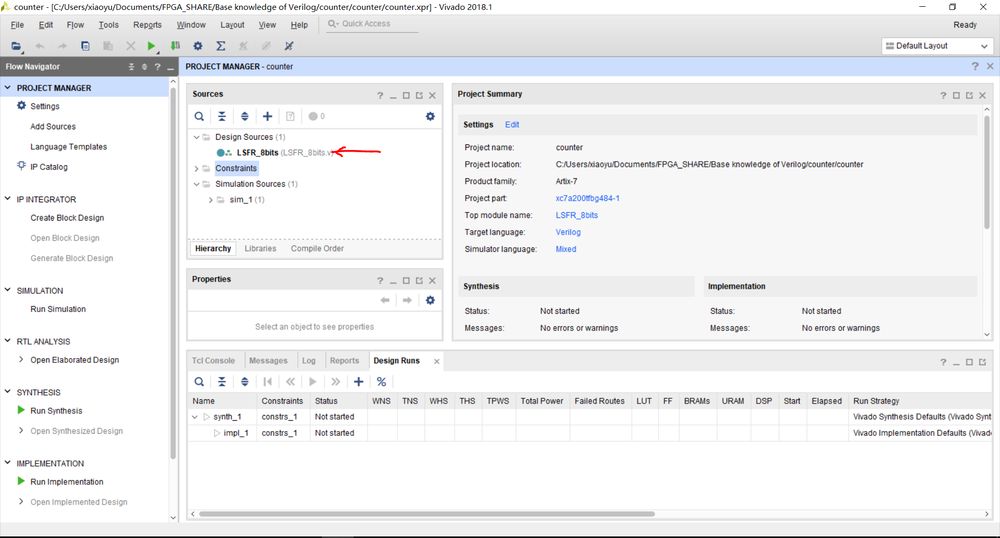

5. 這就生成了一個Verilog設(shè)計文件,在如下界面可以找到。雙擊上圖文件,對Verilog文件進行編輯。

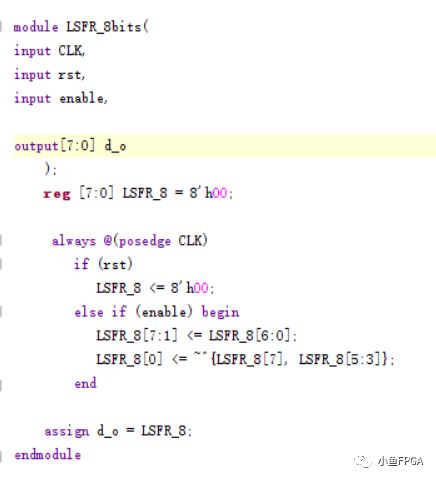

6. 編輯完畢后,如下。點擊保存。

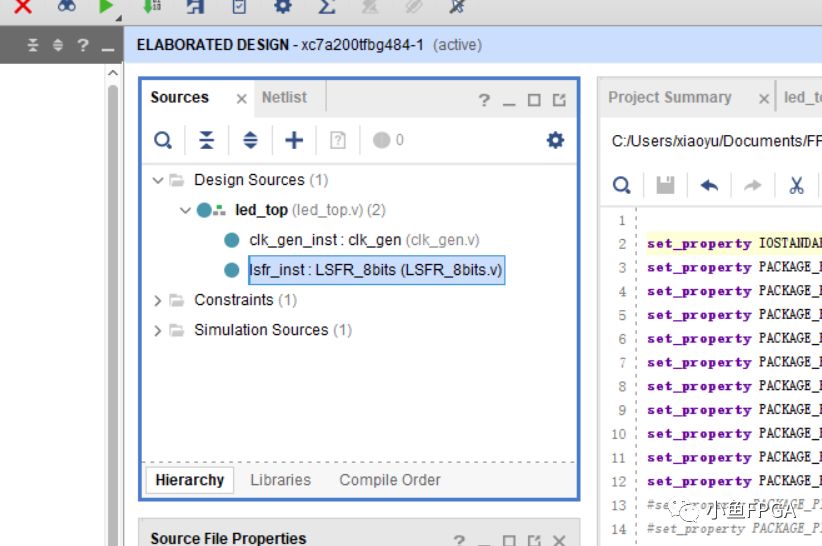

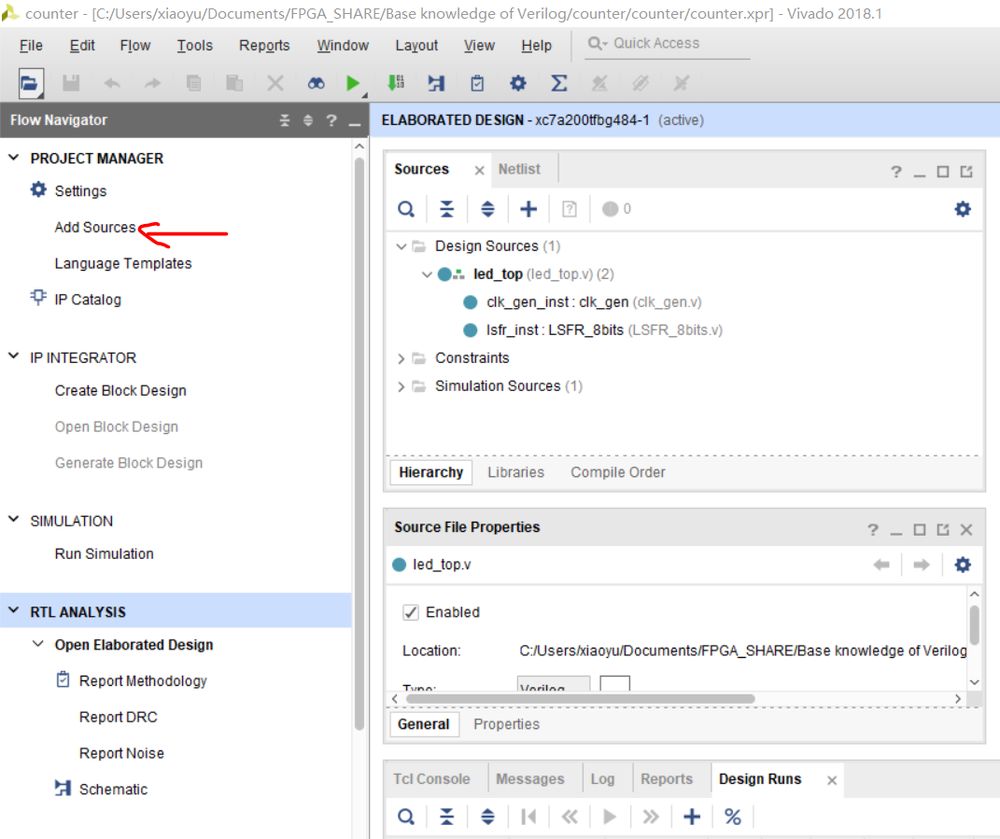

7. 由于我們開發(fā)板上的時鐘頻率為20M,用它來做流水燈,肉眼看不出效果,故需要再添加一個分頻模塊,以及一個頂層模塊。添加方式同上。最后的設(shè)計層次關(guān)系入下。

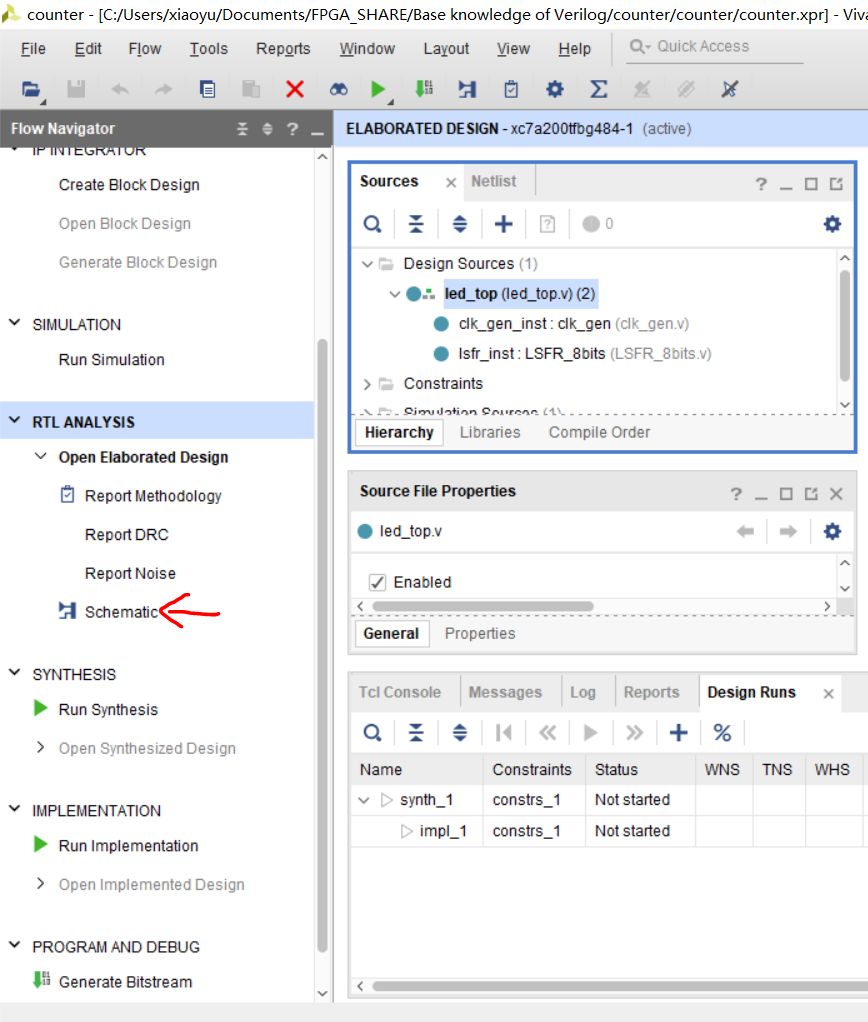

三. 查看Schematic

1. 在如下界面,找到RTL ANALYSIS欄。在RTL ANALYSIS欄下,有一個Open Elaborated Design。在Open Elaborated Design下點擊Schematic。

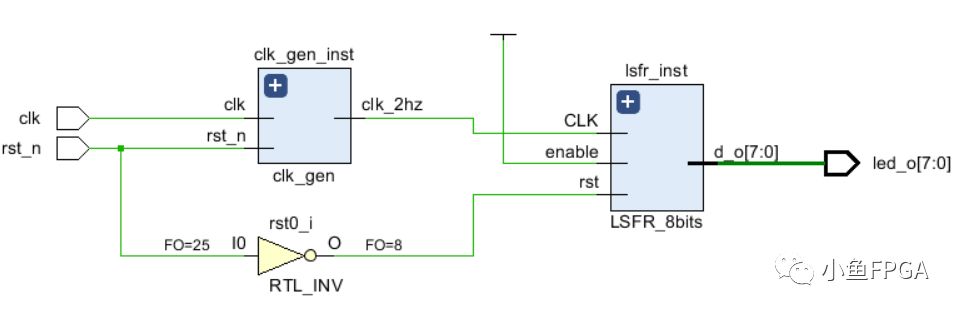

2. 點擊Schematic之后,一般要等一會,便會彈出相應(yīng)的Verilog文件描述的電路原理圖。如下圖。

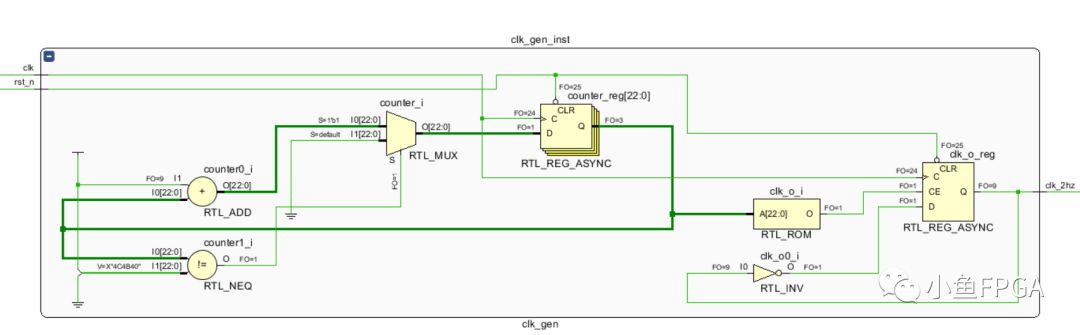

3. 點擊clk_gen_inst原理圖上的+號,就可以展開其內(nèi)部電路。大家可以分析一下這個電路與你們的Verilog描述之間的關(guān)系。

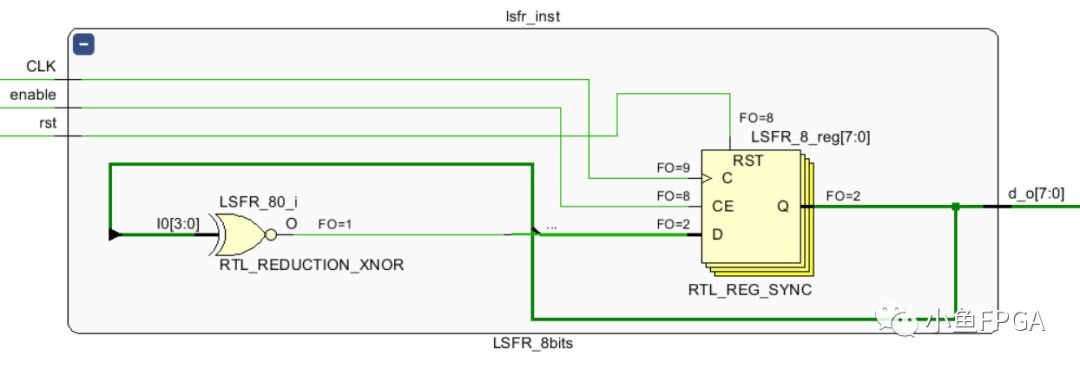

4. 對于LSFR展開后電路如下。

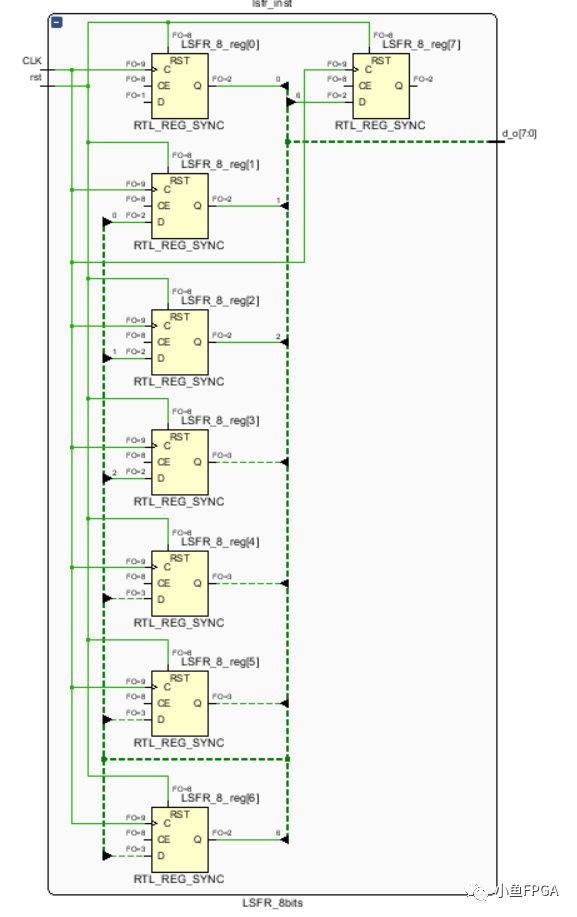

5. 對于LSFR_8_reg[7:0] 這個8bit寄存器,如果想要看它內(nèi)部的連接,可以單擊選中它,再按下F4。其內(nèi)部原理圖就展現(xiàn)出來了。8個寄存器首尾相連,數(shù)據(jù)從第一個寄存器進來,隨著節(jié)拍一拍一拍往后傳遞,這就是移位寄存器。

四. 添加TB文件,做功能仿真

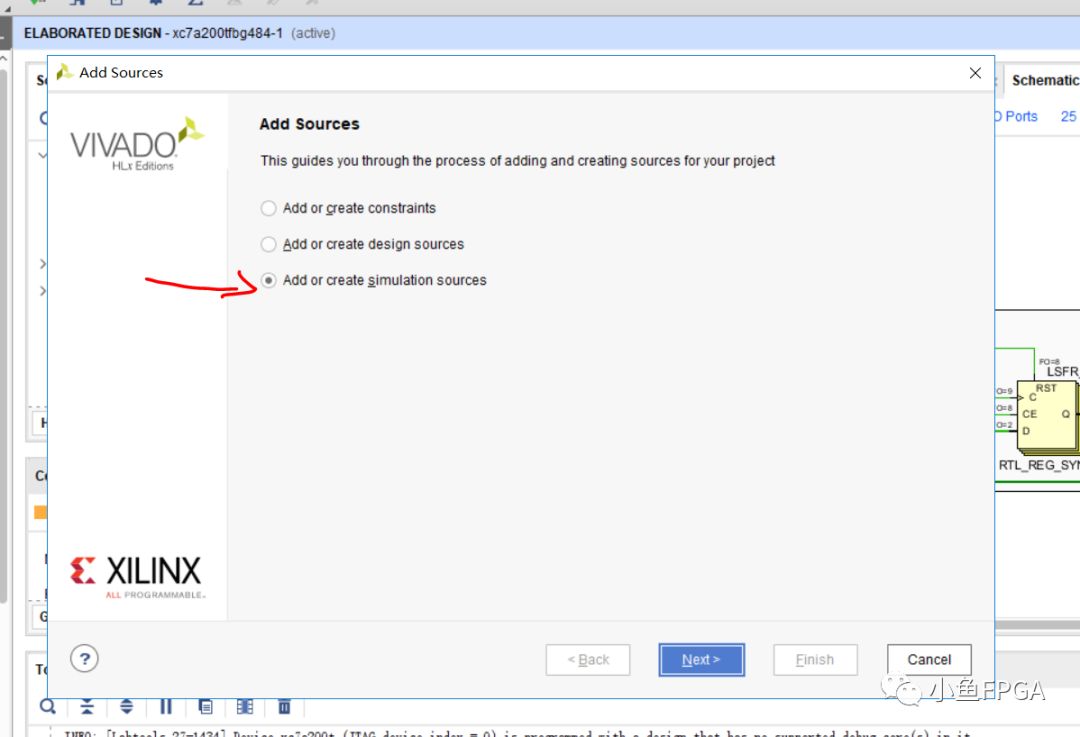

1. 在左邊欄點擊 Add Sources。

2. 選擇 Add or Create simulation source , 點擊Next。

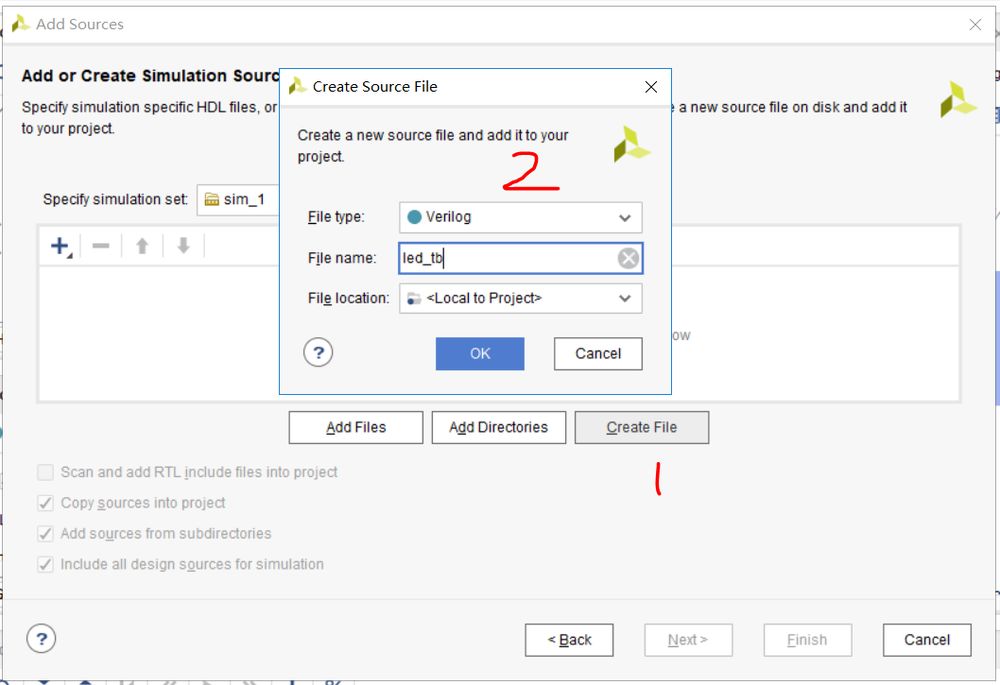

3. 點擊Create Files, 彈出2所示小框。選擇文件類型,這里我們選擇Verilog來寫TB。文件名字可以取為led_tb 。點擊OK。

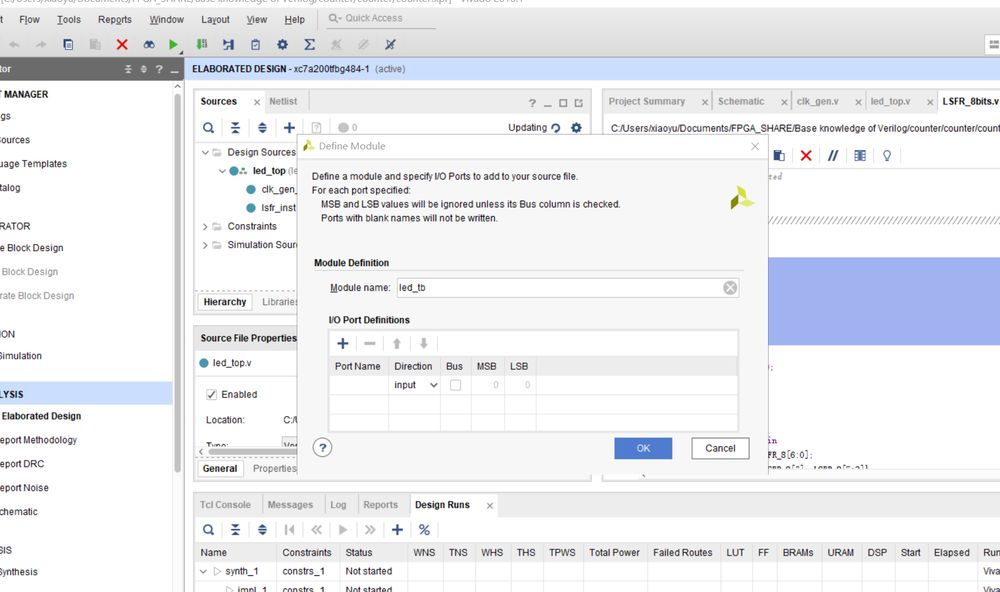

4. 再點擊Finish,此時也會彈出定義端口的設(shè)置框,如下。這里不管,直接點擊OK。

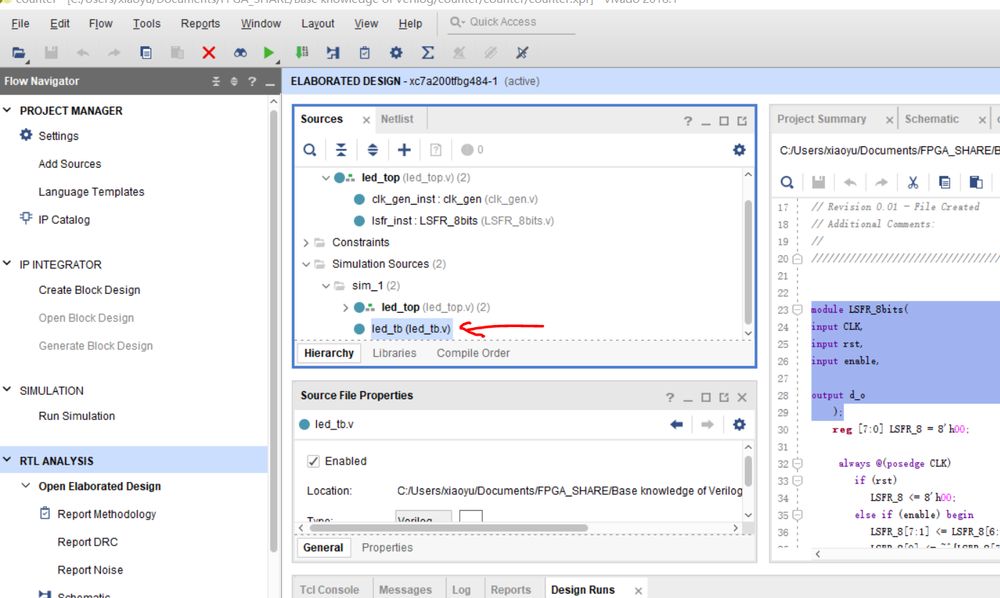

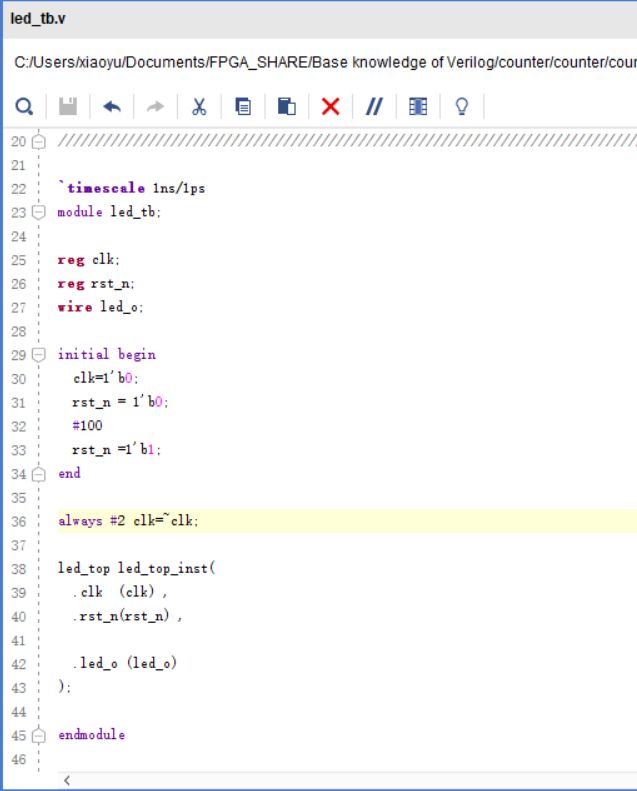

5. 在simulation Sources找到led_tb.v文件,雙擊對其進行編輯。

6. 編輯完之后如下。可以看到,TB只是用來給我們的設(shè)計提供輸入信號(輸入激勵),然后再去通過波形等其它判斷方式,去查看輸出是否符合我們的設(shè)計功能要求。

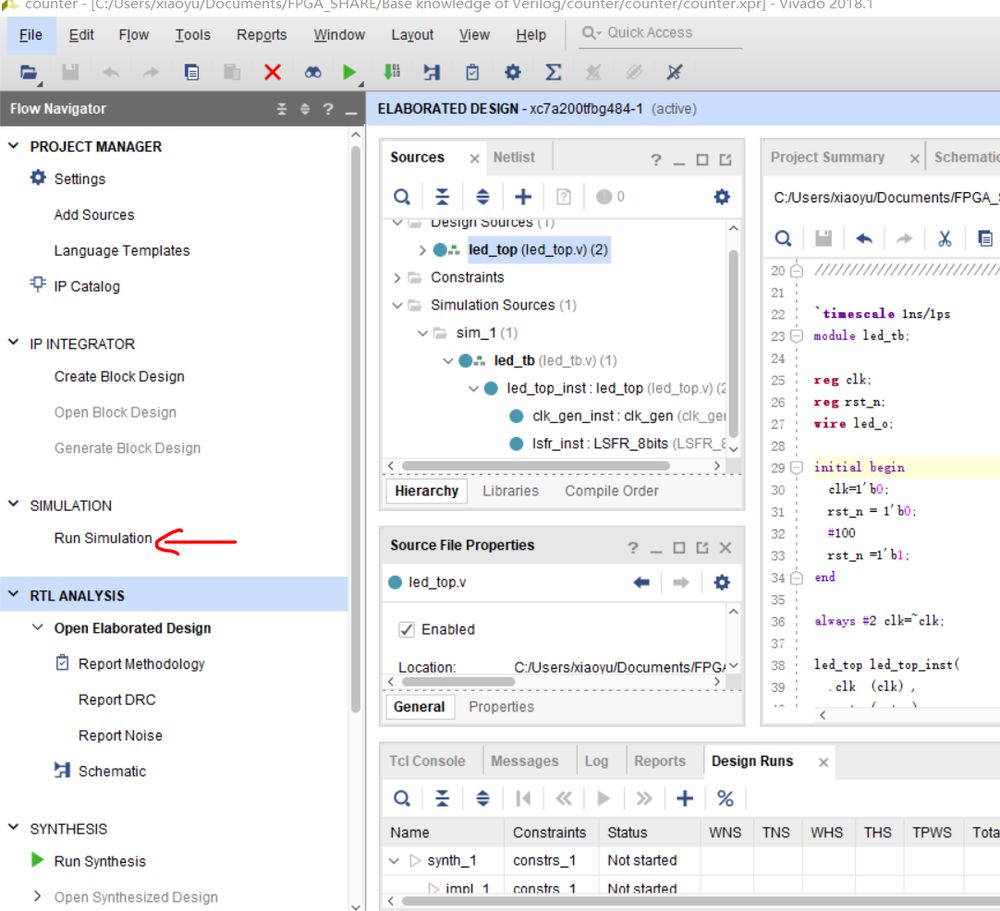

7. 在下圖位置點擊 Run Simulation 。再選擇Run Behavioral Simulation(功能仿真)。

8. 如下圖所示,1按鈕表示從新開始仿真;2表示一直跑仿真;3表示跑仿真的時間為4,5里面的設(shè)置的值。在6里面可以選擇相應(yīng)的模塊,同時7里面就可以看到這個模塊里面的所有內(nèi)部信號,可以右擊某個信號再選擇Add to wave window,將其添加到右邊的波形顯示框顯示。

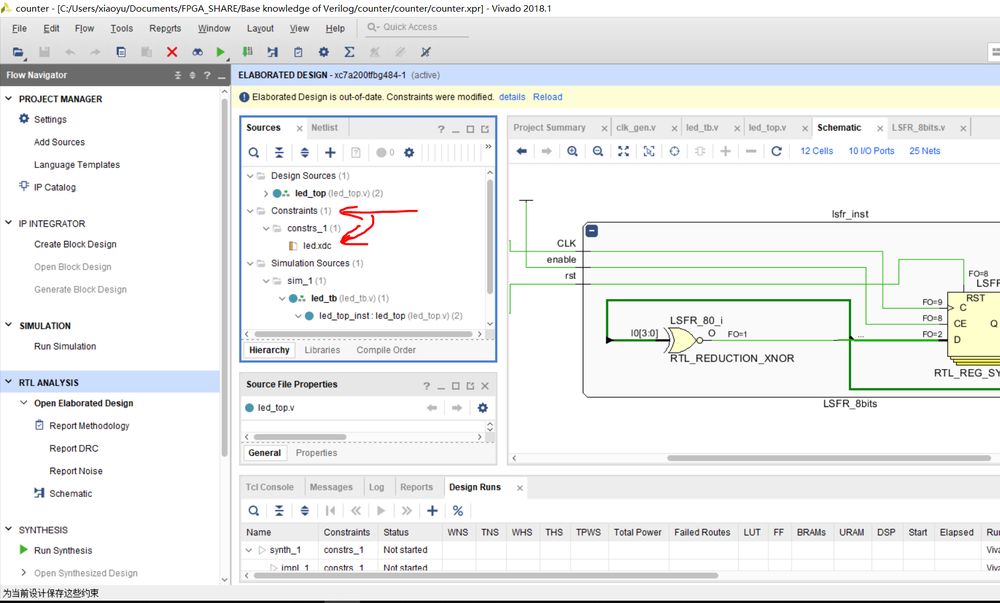

五. 添加約束文件并做Synthesis(綜合)

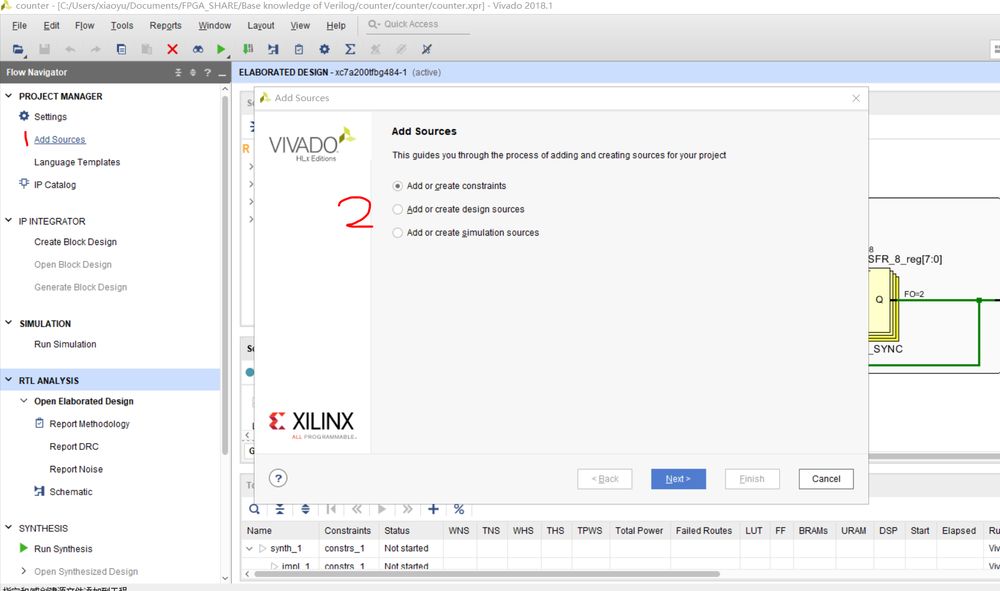

1. 如上添加其它文件一樣點擊 Add Sources。在彈出的頁面選擇 Add or create constraints,再點擊Next。

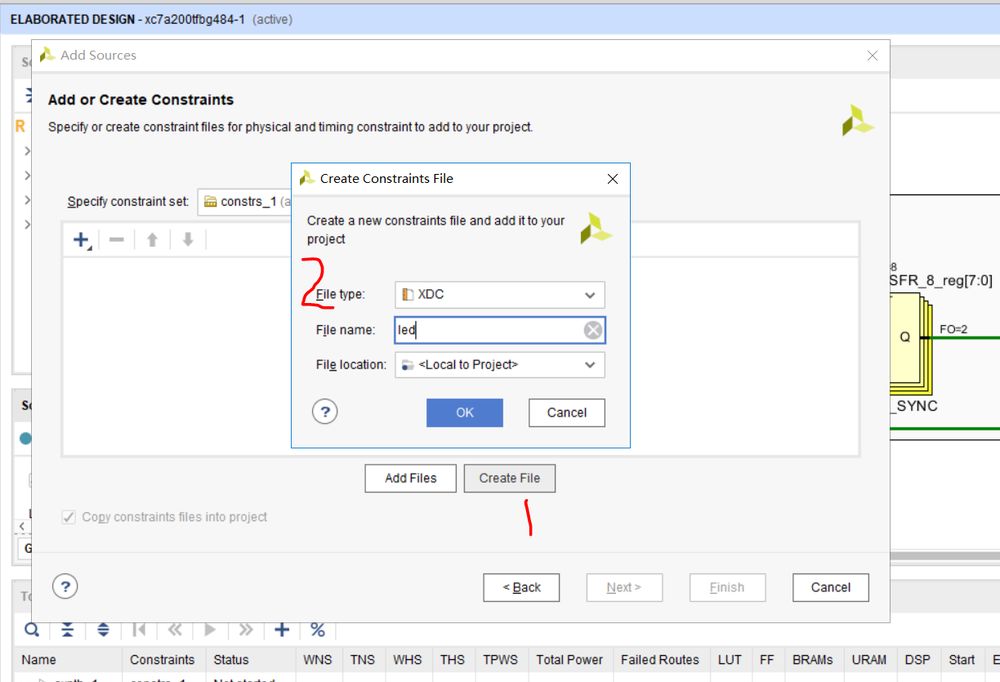

2. 點擊Create Files,在彈出的小框2里填入文件名字。再點擊OK,繼續(xù)點擊Finish。

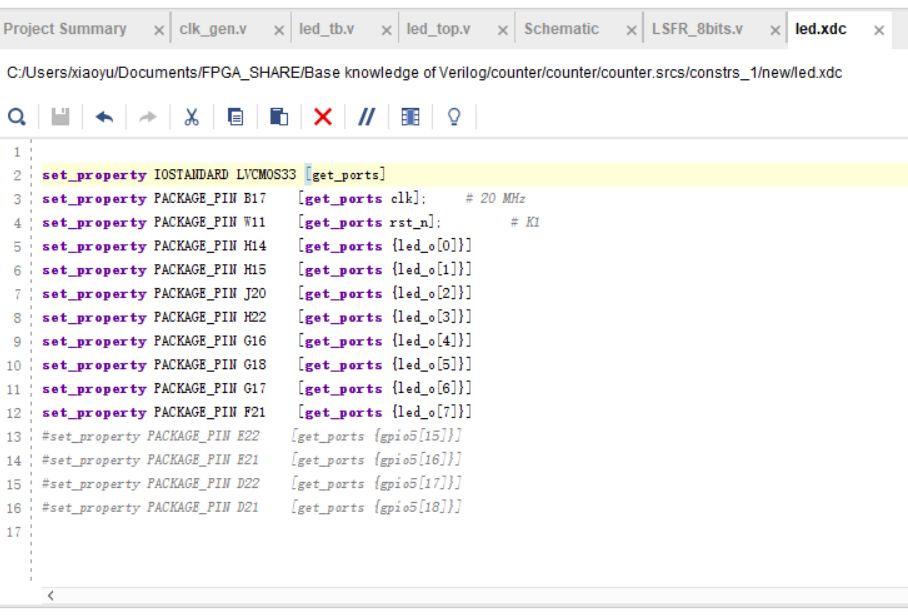

3. 在Source下找到新建的XDC文件。雙擊對其進行編輯。

4. 在XDC文件里面主要是對設(shè)計加入端口與時鐘約束,輸入輸出延時等其它約束。這里我們只加入端口約束。這里端口約束,既將設(shè)計的頂層模塊的輸入輸出端口與實際的FPGA芯片I/O端口互連。編輯完,保存。

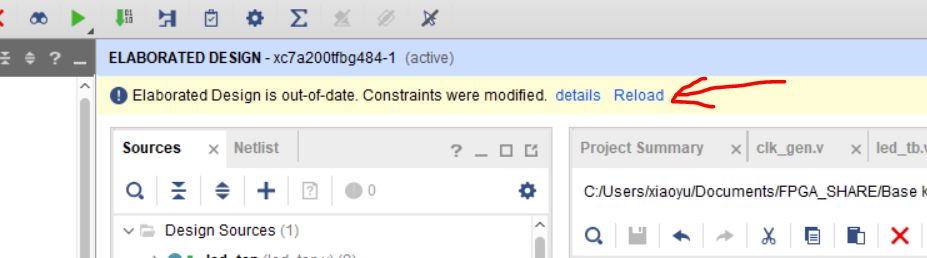

5. 在上面彈出的Constraints更新了的提示,點擊Reload。

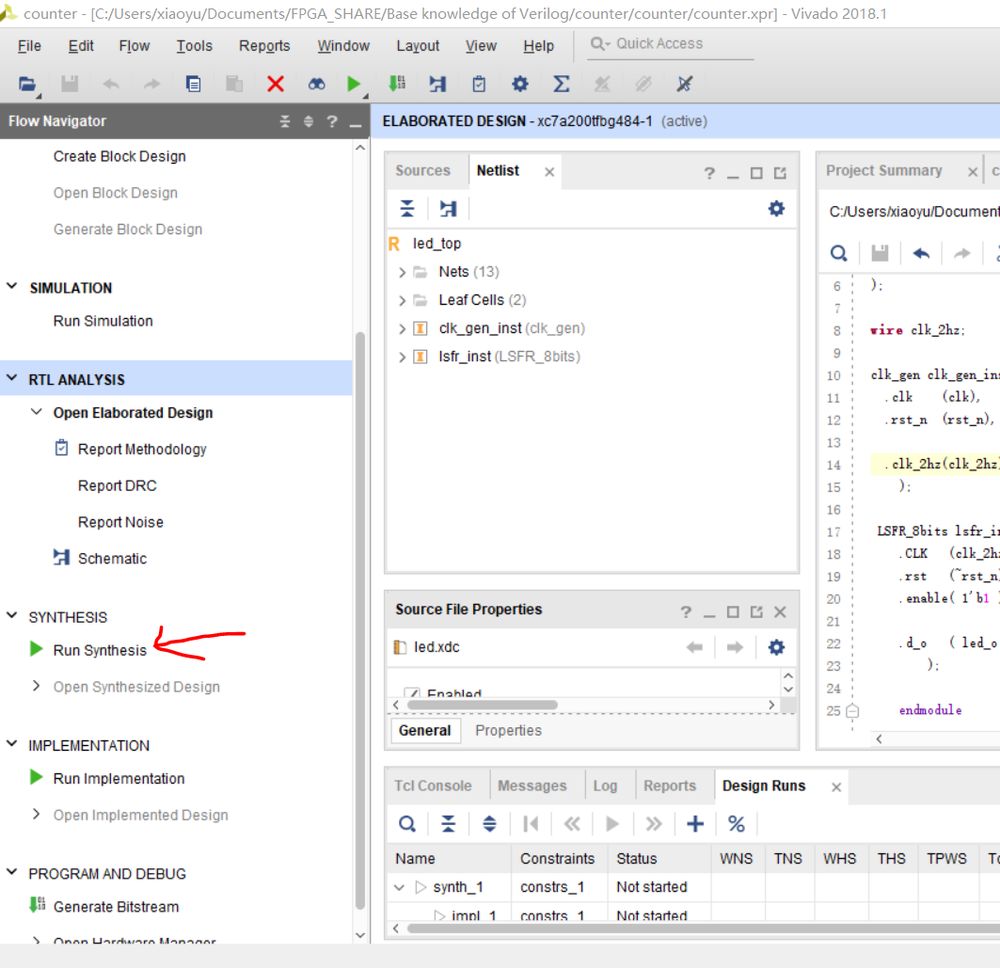

6. 更新完畢,在下圖位置找到Run Synthesis,點擊Run Synthesis。再在彈出的框里選擇OK。

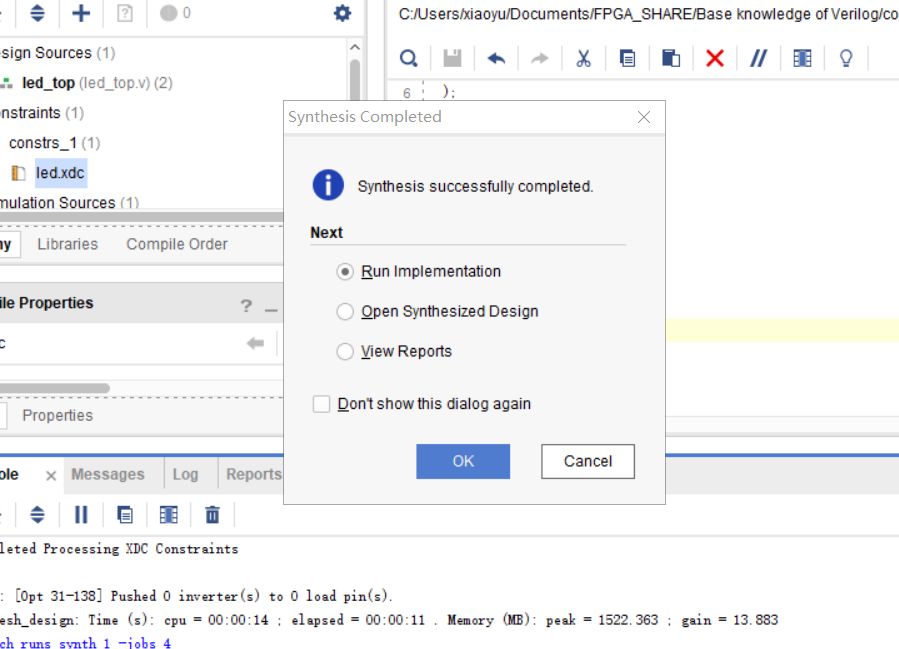

7. 此時在右上方可以看到有Running synth_deign的提示。如果綜合完成則會提示,Synthsis Complete。并彈出如下框。當然這里可以選擇 Run Implementation。也可以選擇其它兩個。真正的設(shè)計當中,在這里我們一般不著急繼續(xù)Run Implementation。而是先看看綜合后的時序報告。當然這里就不多做介紹了。

六. Run Implementation并生成Bit文件

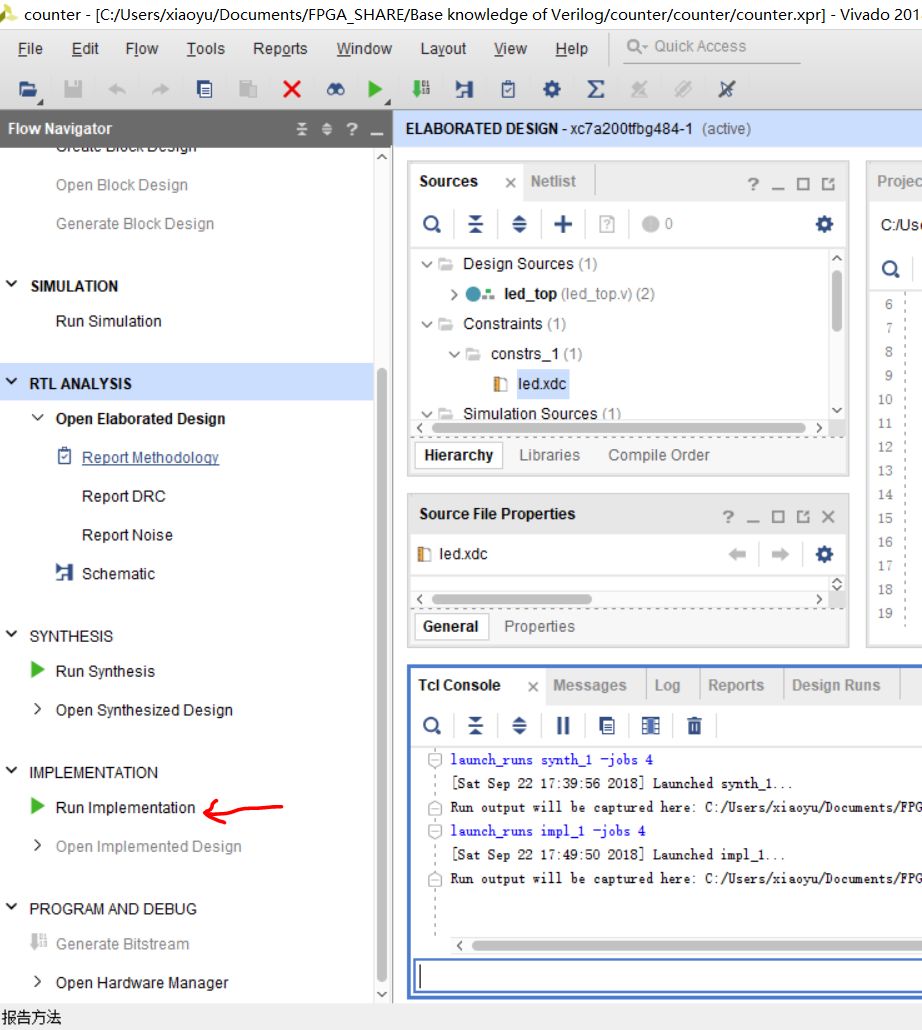

1. 綜合完成后,就是Run Implementation。我們可以在綜合完之后彈出的框里直接選擇Run Implementation。也可以事后在如下圖位置找到 Run Implementation。

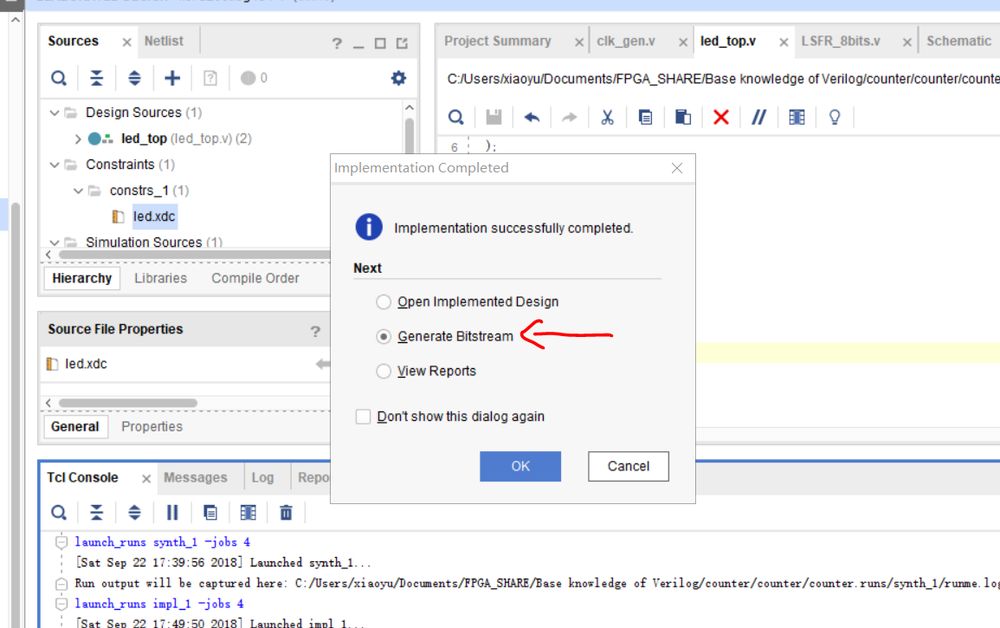

2. 在點擊了 Run Implementation之后,如果Implementation完成了,會彈出如下提示框。這里我們選擇Generate Bitstream,點擊OK。

3. bit文件生成成功,會彈出如下提示。這里我們先點擊Cancel。

七. 將生成的bit文件下載到板子上

1. 先將FPGA開發(fā)板上電,并將Xlinx FPGA下載器與電腦和板子連好。

2. 在如下位置找到 open Hardware Manager -> Open Target。點擊Open Target -> auto connect 。

3. 點擊 Open Target -> auto connect 等待一會,如果如下圖提示No target is open。右擊箭頭所指的localhost,再點擊 close server。

4. 將操作2再做一遍,如果成功連接上開發(fā)板,情況如下。可以看到板子的型號。

5. 右擊器件,選擇 Program Device

6. 如下圖,其自動選擇了本工程生成的bit文件。點擊 Program。

7. 等待一會,下載完畢,在板子上就可以看到效果了。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605177 -

Vivado

+關(guān)注

關(guān)注

19文章

815瀏覽量

66792

原文標題:FPGA設(shè)計與Vivado的使用流程

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

基于FPGA vivado 17.2 的數(shù)字鐘設(shè)計

基于microblaze的vivado開發(fā)流程

基于FPGA Vivado的流水燈樣例設(shè)計資料分享

使用Vivado高層次綜合 (HLS)進行FPGA設(shè)計的簡介

Vivado設(shè)計之Tcl定制化的實現(xiàn)流程

Vivado的安裝生成bit文件及燒錄FPGA的簡要流程教程免費下載

Vivado綜合引擎的增量綜合流程

淺析Vivado在非工程模式下的FPGA設(shè)計流程

【FPGA Vivado】基于 FPGA Vivado 的流水燈樣例設(shè)計

Xilinx FPGA Vivado開發(fā)流程介紹

用TCL定制Vivado設(shè)計實現(xiàn)流程

vivado創(chuàng)建工程流程

vivado主界面及設(shè)計流程

FPGA設(shè)計流程與Vivado的基礎(chǔ)使用

FPGA設(shè)計流程與Vivado的基礎(chǔ)使用

評論