在電路中,時(shí)鐘的不良設(shè)計(jì)可能導(dǎo)致整個(gè)設(shè)計(jì)的失敗。盡管最簡(jiǎn)單的時(shí)鐘分布是最好的,但是在很多應(yīng)用中,電路板上某些位置的芯片需要同步時(shí)鐘信號(hào),而在另外一些位置又需要非同步(即不同頻率)時(shí)鐘信號(hào),時(shí)鐘的分布形成了一個(gè)多分支時(shí)鐘樹,給設(shè)計(jì)帶來了巨大的挑戰(zhàn)。

滿足設(shè)計(jì)規(guī)范中抖動(dòng)(jitter)的要求是時(shí)鐘設(shè)計(jì)中最關(guān)鍵的。抖動(dòng)是時(shí)鐘周期實(shí)際值與理想值之間的差異,并且通常隨著時(shí)鐘樹而變得更復(fù)雜,操作頻率越高,jitter越大。更糟糕的是,它的容差通常非常小,在超高速應(yīng)用中甚至只允許有幾個(gè)飛秒(10-15s)的容差。偏斜(Skew)是指同步時(shí)鐘信號(hào)從一個(gè)芯片到另一個(gè)芯片之間的時(shí)間差異,在采用網(wǎng)絡(luò)級(jí)同步通信的應(yīng)用中,它是一個(gè)很大的問題。相對(duì)而言,Jitter是一個(gè)普遍存在的問題,因?yàn)樗苯佑绊懽杂烧袷庪娐泛屯诫娐罚疚膶⒅攸c(diǎn)討論如何降低他對(duì)電路時(shí)鐘的影響。

設(shè)計(jì)約束要求工程師不僅選擇高精度時(shí)鐘芯片、設(shè)計(jì)優(yōu)秀的電路布局,還要確保時(shí)鐘信號(hào)在傳輸?shù)侥繕?biāo)IC的過程中不受電磁干擾(EMI)或其他信號(hào)線的串?dāng)_。但是在很多時(shí)候,即使選擇了高精度的芯片和優(yōu)秀的時(shí)鐘樹設(shè)計(jì),也不能保證抖動(dòng)是最小的。制造工藝、供應(yīng)電壓、溫度和頻率的變化都會(huì)影響到時(shí)鐘特性。測(cè)試和故障排除是必要的,而在測(cè)試和排除故障的過程中,通常又會(huì)導(dǎo)致器件的更改,甚至是添加諸如抖動(dòng)衰減器等來清理時(shí)鐘信號(hào),以滿足產(chǎn)品規(guī)范。

(注:在描述時(shí)鐘樹精度時(shí),工程師有時(shí)會(huì)提到相位噪聲。抖動(dòng)是時(shí)鐘在時(shí)域上不確定性的度量;而相位噪聲是抖動(dòng)在頻域的表現(xiàn),盡管本文僅限于時(shí)域技術(shù),但所提到的解決方案,也適用于頻域。)

時(shí)鐘樹芯片

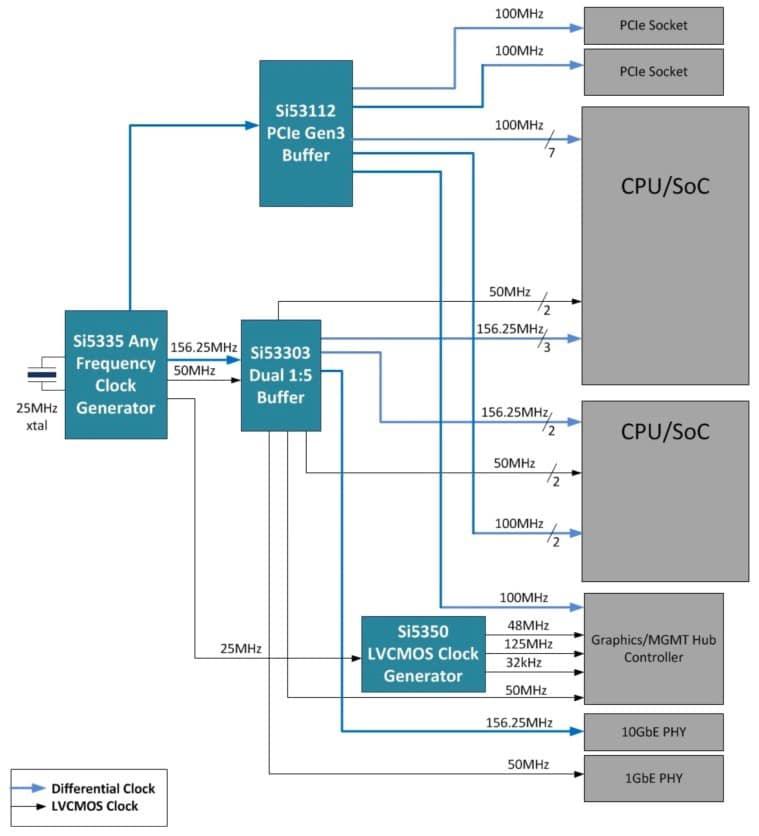

不同產(chǎn)品對(duì)時(shí)鐘的要求像人類的指紋一樣各不相同,所以沒有典型的時(shí)鐘樹結(jié)構(gòu)。圖1給出了一個(gè)時(shí)鐘樹的例子,圖中的芯片來源于Silicon Labs。

雖然時(shí)鐘電路具有多樣性,但通常每個(gè)電路具有以下一個(gè)或多個(gè)器件:

- 石英晶體:生成特定時(shí)鐘信號(hào)頻率的壓電諧振器。

- 晶體振蕩器:以晶體頻率為參考,生成多個(gè)頻率和輸出的電路。壓控振蕩器是晶體振蕩器的一個(gè)變體,可以通過調(diào)諧產(chǎn)生更精確頻率的時(shí)鐘輸出。

- 時(shí)鐘緩沖器:將單時(shí)鐘生成多路副本,分發(fā)給工作在相同頻率下的芯片。時(shí)鐘緩沖器的一個(gè)變體是零延遲緩沖器。

- 時(shí)鐘發(fā)生器:以輸入頻率為參照而生成多個(gè)頻率輸出的芯片。

- 抖動(dòng)衰減器:通過衰減輸入的抖動(dòng)來清理時(shí)鐘信號(hào)的芯片。

石英晶體

石英晶體(X)被用作壓電諧振器,當(dāng)施加電信號(hào)時(shí),它能夠以精確的頻率諧振,然后被用作時(shí)鐘生成器的參考頻率。作為參考頻率,晶體有一些關(guān)鍵優(yōu)勢(shì):

- 根據(jù)晶體的切割和安裝方式,石英晶體可以提供32kHz至50MHz范圍內(nèi)的特定頻率。

- 頻率不受溫度的影響(但也不是完全無關(guān))。

- 晶體產(chǎn)生的相位噪聲很少(抖動(dòng)的頻域表現(xiàn))

- 它們呈現(xiàn)高Q因子(即,頻率輸出在標(biāo)稱或中心頻率附近呈現(xiàn)窄帶寬)。

石英晶體通常與振蕩器電路一起使用,振蕩器電路增強(qiáng)了晶體的溫度獨(dú)立性,放大了晶體的輸出,通過乘或除,可以通過晶體的參考頻率產(chǎn)生一個(gè)或多個(gè)不同頻率的輸出,也可以將晶體的正弦波輸出改變?yōu)?a href="http://m.1cnz.cn/v/tag/8791/" target="_blank">數(shù)字電路所要求的方波。振蕩器電路可以內(nèi)置在目標(biāo)IC中,也可以與晶體振蕩器(XO)相配對(duì),該器件的輸出將成為目標(biāo)IC的時(shí)鐘輸入。 Microchip的PL602-03就是一個(gè)例子,它產(chǎn)生的時(shí)鐘抖動(dòng)極小,可以使用12到25MHz的石英晶體,產(chǎn)生48到100MHz的輸出頻率。

晶體振蕩器

晶體振蕩器(XO)的方波輸出可以是單端信號(hào)也可以是差分信號(hào)。差分信號(hào)一般應(yīng)用于高速并且對(duì)抖動(dòng)敏感的電路。使用晶體振蕩器是一般要考慮成本,除非應(yīng)用需要多個(gè)時(shí)鐘頻率或?qū)r(shí)鐘精度要求特別嚴(yán)格。

XO的一個(gè)替代方案是壓控XO(VCXO)。VCXO的參考時(shí)鐘仍然由石英晶體決定,但通過調(diào)整控制電壓,該頻率可以在某個(gè)范圍內(nèi)略微調(diào)整。VCXO的電壓調(diào)整范圍約為±100-200ppm。VCXO可用于機(jī)頂盒等系統(tǒng),以滿足所需的閉環(huán)頻率響應(yīng),同時(shí)保持干凈的時(shí)鐘輸出。安森美半導(dǎo)體的NB3N508S就是一個(gè)例子,它是一款低相位噪聲的VCXO,可以從27MHz的石英晶體信號(hào)中產(chǎn)生216MHz的時(shí)鐘輸出。在0-3.3V范圍內(nèi)調(diào)節(jié)VIN引腳的電壓,可獲得±100ppm的電壓輸出。

在電路中,將石英晶體,XO或VCXO放置在目標(biāo)IC附近,可以使用更少的時(shí)鐘器件,以最低的成本構(gòu)建時(shí)鐘樹。然而,隨著目標(biāo)IC數(shù)量的增加,這種方法也變得不切實(shí)際。

時(shí)鐘緩沖器

對(duì)于需要多個(gè)相同時(shí)鐘輸入的電路,一個(gè)可選的方案是添加時(shí)鐘緩沖器。時(shí)鐘緩沖器的參考時(shí)鐘可以由石英晶體、晶體振蕩器或時(shí)鐘芯片(如時(shí)鐘發(fā)生器)來提供。參考時(shí)鐘從輸入引腳輸入,時(shí)鐘緩沖器可以復(fù)制出2至10個(gè)時(shí)鐘副本給需要同一頻率的IC。使用一個(gè)時(shí)鐘緩沖器,可以省去原本需要的多個(gè)石英晶體和晶體振蕩器,降低了成本,也節(jié)省了電路板空間,但給布線帶來了麻煩。一個(gè)經(jīng)驗(yàn)法則是,如果需要四個(gè)或更多時(shí)鐘,使用時(shí)鐘緩沖器通常比使用單獨(dú)的晶體和晶體振蕩器更加經(jīng)濟(jì)實(shí)惠。

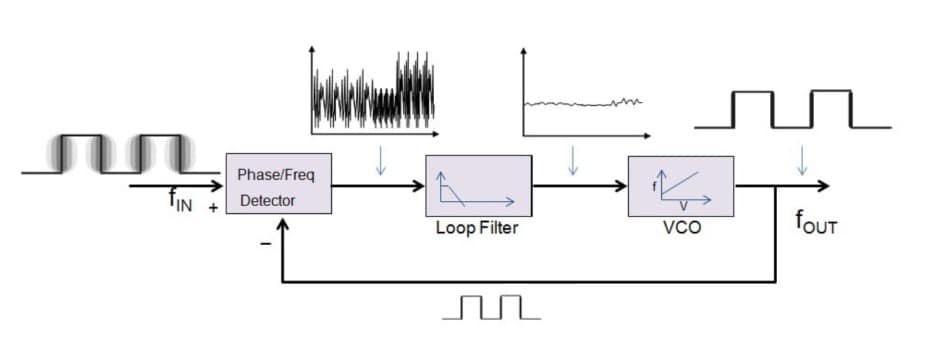

精度更高的時(shí)鐘緩沖器叫做零延遲時(shí)鐘緩沖器,它的成本更高些。如針對(duì)PCIe應(yīng)用的IDT 9DBL0是一種3.3V雙輸出時(shí)鐘緩沖芯片,它將一個(gè)時(shí)鐘信號(hào)扇出為多個(gè)時(shí)鐘信號(hào),而不產(chǎn)生延遲,輸出之間的偏差也很小。這些器件一般采用鎖相環(huán)(PLL)技術(shù),該鎖相環(huán)使用參考輸入和由輸出驅(qū)動(dòng)的反饋輸入。PLL內(nèi)的相位檢測(cè)器能夠調(diào)節(jié)VCXO的輸出頻率,使多路輸出無相位或頻率差異,因此無抖動(dòng)差異。

時(shí)鐘發(fā)生器

與時(shí)鐘緩沖器一樣,時(shí)鐘發(fā)生器的參考時(shí)鐘也由石英晶體、晶體振蕩器或其他時(shí)鐘電路提供。前面提到的時(shí)鐘緩沖器是用來生成多個(gè)相同頻率的信號(hào)副本,而時(shí)鐘發(fā)生器可以通過單個(gè)參考時(shí)鐘輸入生成多個(gè)不同頻率的時(shí)鐘輸出。此外,時(shí)鐘發(fā)生器還包括其他功能,如時(shí)鐘輸出的使能與關(guān)閉、頻率偏移和頻譜擴(kuò)展。通過使用差分信號(hào),時(shí)鐘skew的控制,傳輸線的精心設(shè)計(jì)等可以保證集中式時(shí)鐘源可以提供與多個(gè)分立晶體和晶體振蕩器相似的時(shí)鐘精度。

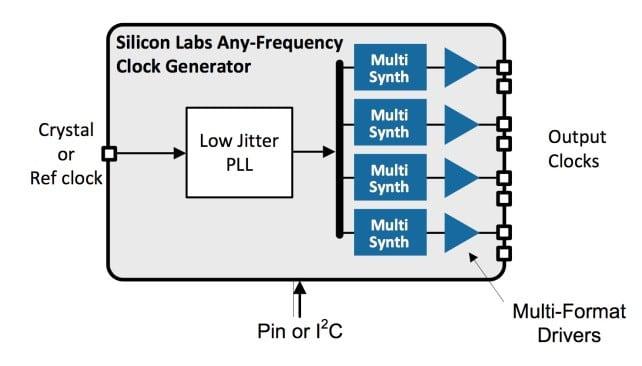

時(shí)鐘發(fā)生器的一個(gè)例子是Silicon Labs的Si5338Q,該芯片是一款高性能,低抖動(dòng)的時(shí)鐘發(fā)生器,它能夠合成四個(gè)獨(dú)立的高達(dá)350MHz的用戶可編程時(shí)鐘頻率并能夠選擇高達(dá)710MHz的輸出頻率。它的輸出支持四個(gè)差分時(shí)鐘,八個(gè)單端時(shí)鐘或兩者的組合(圖2)。

抖動(dòng)衰減器

時(shí)鐘樹可能需要的另一個(gè)芯片是抖動(dòng)衰減器。抖動(dòng)衰減器是專用芯片,用于“clean-up”時(shí)鐘信號(hào)。它一般用在高速電路中,必須要將抖動(dòng)減小到可以忽略的程度以確保電路正常工作的場(chǎng)合。

抖動(dòng)定義

抖動(dòng)是與理想時(shí)鐘相比,實(shí)際周期變化的值,以秒(s)為單位。

抖動(dòng)的類型

抖動(dòng)有兩種形式,隨機(jī)性抖動(dòng)和確定性抖動(dòng):

隨機(jī)抖動(dòng)

隨機(jī)抖動(dòng)在本質(zhì)上是系統(tǒng)的固有噪聲。該噪聲遵循高斯曲線,不是一個(gè)可識(shí)別的噪聲源,這給抖動(dòng)的分析帶來了麻煩。但幸運(yùn)的是,在大多數(shù)系統(tǒng)中,隨機(jī)抖動(dòng)可以忽略不計(jì),不會(huì)影響電路性能。但是,有時(shí)候本底噪聲可能會(huì)非常高,以至于必須要進(jìn)行一些故障排除來提高電路性能。

確定性抖動(dòng)

確定性抖動(dòng)有一個(gè)特定的原因并且通常是重復(fù)的。這使得分析其原因要比隨機(jī)抖動(dòng)更容易些。確定性抖動(dòng)可以進(jìn)一步分類為周期性抖動(dòng)和數(shù)據(jù)相關(guān)性抖動(dòng)。例如,由開關(guān)電源引起的抖動(dòng)是確定性的和周期性的,與電源的工作頻率相一致。相反,數(shù)據(jù)相關(guān)性抖動(dòng)可能是周期性的也可能是非周期性的,因?yàn)樗怯芍T如以太網(wǎng)或PCIe通信中的串行數(shù)據(jù)流的動(dòng)態(tài)變化和不規(guī)則時(shí)鐘邊緣等因素造成的。數(shù)據(jù)相關(guān)性抖動(dòng)因系統(tǒng)、功能和其他因素等而發(fā)生變化,難以被診斷。

在某些系統(tǒng)中,確定性的抖動(dòng)可能看起來是隨機(jī)的,因?yàn)槎鄠€(gè)噪聲源相互重疊,掩蓋了與原本獨(dú)立的噪聲源。

抖動(dòng)度量

抖動(dòng)可有三種形式:絕對(duì)抖動(dòng),周期抖動(dòng)和周期間抖動(dòng)。

絕對(duì)抖動(dòng)

絕對(duì)抖動(dòng),也稱為時(shí)間間隔誤差(JTIE)-表示某時(shí)刻信號(hào)與理想時(shí)鐘的偏移量

周期抖動(dòng)

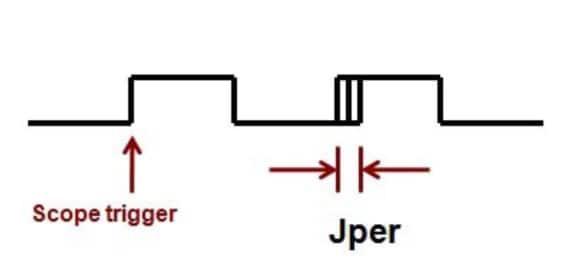

周期抖動(dòng)(Jper)-不要和上面描述的周期性抖動(dòng)混淆。他是是在固定周期數(shù)(通常為1,000或10,000)內(nèi)(圖3)所有獨(dú)立時(shí)鐘周期的最長(zhǎng)和最短時(shí)鐘周期之差。

周期間抖動(dòng)

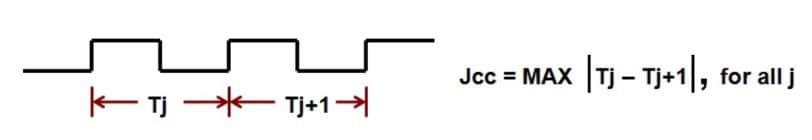

周期間抖動(dòng)(Jcc)是在固定周期數(shù)(通常為1,000或10,000個(gè)周期)內(nèi)測(cè)量的連續(xù)時(shí)鐘周期之間的最大差異(圖4)。

抖動(dòng)的影響

有些抖動(dòng)是不可避免的并且不全是壞事。但是,過度的抖動(dòng)會(huì)影響電路性能。例如,在高頻率下運(yùn)行且需要高精準(zhǔn)的同步時(shí)序系統(tǒng)必須滿足JTIE的規(guī)范。同步eEhernet(SyncE)和光傳輸網(wǎng)絡(luò)(OTN)應(yīng)用也是這樣的例子。高的JTIE將導(dǎo)致系統(tǒng)的同步失敗和故障發(fā)生。

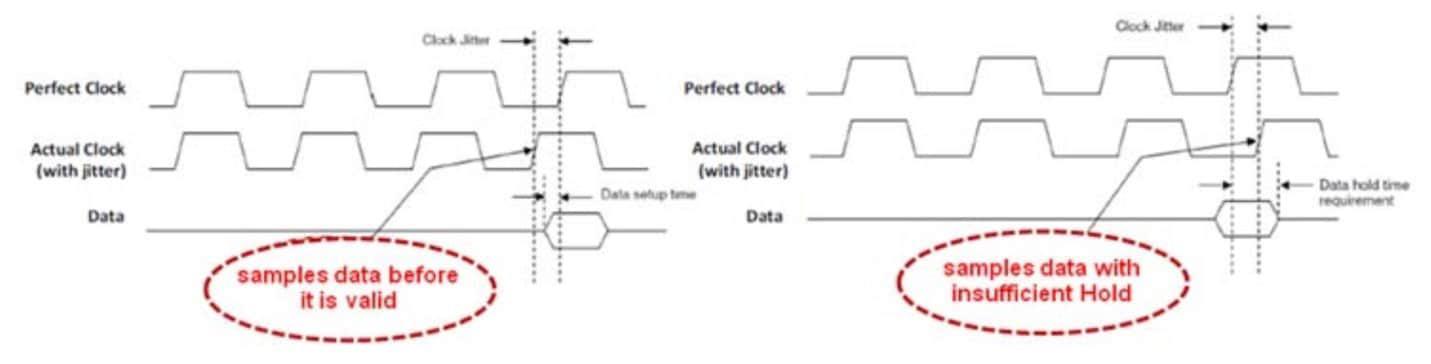

Jper和Jcc對(duì)于大多數(shù)的數(shù)字應(yīng)用都很重要,因?yàn)樵跀?shù)字系統(tǒng)中,它們可能會(huì)影響鎖存器和觸發(fā)器的建立時(shí)間和保持時(shí)間:

- 鎖存器:時(shí)鐘為高電平時(shí),鎖存器傳輸數(shù)據(jù),時(shí)鐘為低電平時(shí),鎖存器保持?jǐn)?shù)據(jù)。

- 觸發(fā)器:觸發(fā)器在時(shí)鐘周期的上升沿到來時(shí)傳輸數(shù)據(jù)。

如果數(shù)據(jù)流和系統(tǒng)時(shí)鐘受到Jper和Jcc的影響,則會(huì)輪流影響鎖存器和觸發(fā)器的建立時(shí)間和保持時(shí)間,從而導(dǎo)致數(shù)據(jù)損壞或丟失,降低了ADC的采樣精度,或者限制了處理器的運(yùn)行頻率。在不能忍受時(shí)鐘頻率發(fā)生突變的應(yīng)用中,對(duì)Jcc的控制也是很重要的(圖5)。

時(shí)序問題的解決方案

應(yīng)用這些實(shí)踐和技巧將會(huì)幫助解決時(shí)序問題:

采用好的設(shè)計(jì)實(shí)例

減小時(shí)序問題的第一步是使電路盡可能地簡(jiǎn)單。不論每個(gè)定時(shí)器的性能如何優(yōu)秀,每個(gè)器件都會(huì)引入固有抖動(dòng),它們的影響是累積的。 器件的數(shù)量少就會(huì)引起更小的抖動(dòng)。

每個(gè)電路都可以容忍一定程度的抖動(dòng)而不會(huì)影響性能。如果不保證性能,工程師應(yīng)盡量避免使用對(duì)抖動(dòng)要求嚴(yán)格的電路。識(shí)別和減小抖動(dòng)是一個(gè)困難又耗時(shí)的過程,只有在重要的情況下才應(yīng)該被采用。

這個(gè)建議擴(kuò)展到了電路的運(yùn)行參數(shù)。開發(fā)者應(yīng)該評(píng)估系統(tǒng)運(yùn)行頻率等要求,因?yàn)轭l率越高,Jper和Jcc就越大。(JTIE與操作頻率無關(guān)。)

開發(fā)者還應(yīng)該考慮時(shí)鐘樹的最佳拓?fù)浣Y(jié)構(gòu)。通過使用更少的石英晶體和時(shí)鐘發(fā)生器并增加更多的時(shí)鐘緩沖器,可以降低成本,但是會(huì)在時(shí)間精度上進(jìn)行折衷。 類似地,通過采用VCXO和零延遲緩沖器,可以提高時(shí)序精度,從而提高復(fù)雜性(由于像晶體這樣的元件趨向于需求,所以可能需要更長(zhǎng)的交付周期)。

其他的設(shè)計(jì)技巧包括:

- 通過保持信號(hào)線短路,選擇最佳拓?fù)浣Y(jié)構(gòu),并選擇材料預(yù)算可支持的最佳芯片,來限制時(shí)鐘樹的延遲。

- 控制轉(zhuǎn)換時(shí)間以保持時(shí)鐘邊緣的良好定義。

- 在電路中匹配元件(例如,除非由于操作原因而需要不同類型的元件,一般情況下都使用相同類型的時(shí)鐘發(fā)生器和時(shí)鐘緩沖器)。

- 當(dāng)從單芯片中分配多個(gè)信號(hào)時(shí)要匹配時(shí)鐘線的長(zhǎng)度。

- 使用間隔和屏蔽來保護(hù)時(shí)鐘線免受串?dāng)_。

- 使用具有積分去耦功能的時(shí)鐘緩沖器。

開發(fā)人員還應(yīng)該利用商家免費(fèi)提供的白皮書和時(shí)鐘電路設(shè)計(jì)的應(yīng)用筆記來獲取建議。

最后,開發(fā)人員應(yīng)根據(jù)時(shí)鐘樹拓?fù)浣Y(jié)構(gòu)的電路圖和所選芯片的數(shù)據(jù)表來計(jì)算容限和抖動(dòng)的累積量。許多芯片供應(yīng)商提供線上工具來簡(jiǎn)化這一過程,并且評(píng)估芯片和拓?fù)浣Y(jié)構(gòu)的影響。這些工具甚至可以被用來為給定的應(yīng)用程序提供芯片和拓?fù)浣Y(jié)構(gòu)。

分析時(shí)鐘樹

遵循良好的設(shè)計(jì)準(zhǔn)則,選擇合適的時(shí)鐘樹拓?fù)浣Y(jié)構(gòu),采用高質(zhì)量的芯片是非常好的做法,但這也并不能保證時(shí)鐘是完全令人滿意的。很多其他的因素也可以引入抖動(dòng),例如不匹配的信號(hào)線長(zhǎng)度,EMI,電壓波動(dòng)甚至機(jī)械應(yīng)力(影響晶體的壓電特性),這些因素都是不可預(yù)測(cè)的。即使是最好的時(shí)鐘電路也可能被這些噪聲源損害。

如果時(shí)鐘電路的性能不如預(yù)期,則需要使用為此設(shè)計(jì)的專用儀器進(jìn)行分析,以便確定時(shí)鐘問題的根源。

每種類型的抖動(dòng)都是以皮秒(高精度的定時(shí)系統(tǒng)用飛秒)為單位來表示的。大的偏差意味著時(shí)鐘質(zhì)量低,抖動(dòng)也常用時(shí)鐘增量的均方根(RMS)值來表示。計(jì)算RMS值通常假定時(shí)序偏差服從高斯分布,計(jì)算結(jié)果是抖動(dòng)測(cè)量值的標(biāo)準(zhǔn)差(圖6)。

通常使用高速數(shù)字示波器對(duì)抖動(dòng)進(jìn)行測(cè)量(時(shí)域值)。示波器可以直接測(cè)量出JTIE,Jper和Jcc,并可以還可以測(cè)量高頻或低頻時(shí)鐘信號(hào)的抖動(dòng)。示波器特別適合測(cè)量數(shù)據(jù)相關(guān)性抖動(dòng)(圖7)。

通過對(duì)原始數(shù)據(jù)進(jìn)行后期處理,可以計(jì)算出RMS抖動(dòng)值。然后可以通過計(jì)算“峰值因數(shù)”將RMS抖動(dòng)值轉(zhuǎn)換為峰-峰值。計(jì)算波峰因數(shù)通常假設(shè)時(shí)鐘的工業(yè)標(biāo)準(zhǔn)誤碼率(BER)為10-12。對(duì)于這個(gè)BER,RMS到峰-峰值因數(shù)是14.069。因此,1ps的RMS抖動(dòng)值相當(dāng)于14.069ps的峰-峰抖動(dòng)值。

如果測(cè)得的抖動(dòng)幅度超出預(yù)定的范圍,則在使用儀器時(shí)需要一些技巧,不僅要確定抖動(dòng)的大小,還要確定抖動(dòng)的來源。周期性確定性的抖動(dòng)是最容易被數(shù)據(jù)相關(guān)性抖動(dòng)跟蹤的,但也更難以排除故障。由于這種類型的抖動(dòng)可能具有隨機(jī)抖動(dòng)的外觀表現(xiàn),因此難點(diǎn)仍然是來自多個(gè)源疊加的周期性抖動(dòng)或數(shù)據(jù)相關(guān)性抖動(dòng)。對(duì)于特別棘手的問題,應(yīng)該從儀器和芯片供應(yīng)商處尋求建議。

改善的時(shí)鐘電路

一旦問題的根源被發(fā)現(xiàn),就有許多方法來解決抖動(dòng)問題;根據(jù)抖動(dòng)的來源,可以通過以下幾種方式來簡(jiǎn)化電路,從而解決問題:

- 用一個(gè)能夠提供多路輸出的緩沖器替換多個(gè)分立的緩沖器。

- 更換更高規(guī)格、更專業(yè)的芯片。

- 重新布線并匹配走線長(zhǎng)度。

具體的解決方案將取決于抖動(dòng)的類型和來源。

在很多系統(tǒng)中,隨機(jī)抖動(dòng)是性能下降主要原因。這時(shí),最好的方法是將時(shí)鐘電路盡可能的簡(jiǎn)化,然后用更高規(guī)格的元件依次替換每個(gè)元件,直到本底噪聲被降低到可接受的水平。

其他方面也可以被改進(jìn),如開關(guān)電源和目標(biāo)芯片:

開關(guān)電源

能夠經(jīng)常顯示出隨機(jī)抖動(dòng)和確定性抖動(dòng)來源的區(qū)域是電源,特別是開關(guān)電源,開關(guān)電源因其高轉(zhuǎn)換效率而受歡迎,但也是眾所周知的EMI和其他噪聲源。這種噪聲應(yīng)該在供應(yīng)的輸出中被濾除。否則,將會(huì)損害時(shí)鐘信號(hào)的完整性。另外,設(shè)計(jì)人員還應(yīng)該確保電源輸出走線不會(huì)過于靠近時(shí)鐘電路線路,限制串?dāng)_的機(jī)率; 其他信號(hào)走線也是如此。一個(gè)好的設(shè)計(jì)建議是在時(shí)鐘線旁邊運(yùn)行一個(gè)接地走線,如果這一點(diǎn)不可行,則應(yīng)該增加時(shí)鐘線與其他信號(hào)線之間的距離。

目標(biāo)芯片

目標(biāo)芯片的一個(gè)常見問題是信號(hào)的終止。如果沒有適當(dāng)?shù)慕K止,將會(huì)發(fā)生阻抗不匹配,并且能量將反射到線路上。這些脈沖可能非常大,以至于使器件錯(cuò)誤的觸發(fā),導(dǎo)致電路錯(cuò)誤操作(并且可能是災(zāi)難性的)。對(duì)于時(shí)鐘電路來說,最流行的終止方式是在信號(hào)線中串聯(lián)一個(gè)電阻,并把他放到盡可能靠近信號(hào)源的位置。電阻要匹配時(shí)鐘驅(qū)動(dòng)器的輸出阻抗與傳輸線的阻抗。這樣,電阻就會(huì)吸收掉返回的能量,進(jìn)而不再影響時(shí)鐘芯片。

使用抖動(dòng)衰減器

在很多時(shí)候,即使采用了所有故障排除技術(shù),抖動(dòng)也可能達(dá)不到要求。當(dāng)這種情況發(fā)生時(shí),一種方法是可以在時(shí)鐘樹中添加抖動(dòng)衰減器來clear-up時(shí)鐘信號(hào)。像IDT的8V19N407或Silicon Lab的Si5317等器件采用PLL架構(gòu)來實(shí)現(xiàn)抖動(dòng)的衰減(通常是倍頻)。PLL用于過濾來自輸入時(shí)鐘的噪聲并產(chǎn)生低抖動(dòng)輸出時(shí)鐘。降低環(huán)路濾波帶寬會(huì)增加參考時(shí)鐘的抖動(dòng)衰減量,使得從輸入到輸出傳輸?shù)亩秳?dòng)較小(圖8)。

結(jié)論

抖動(dòng)的優(yōu)化起始于時(shí)鐘樹的設(shè)計(jì)和電路元件的選擇,不同的應(yīng)用場(chǎng)合有不同的方案,在進(jìn)行硬件設(shè)計(jì)之前,工程師應(yīng)該利用芯片供應(yīng)商的線上資源來評(píng)估時(shí)鐘電路的性能。這樣做可以在設(shè)計(jì)后期節(jié)約時(shí)間和成本,并且簡(jiǎn)化器件選擇和采購(gòu)。

但是,即使利用線上資源,采用已有的設(shè)計(jì)技術(shù)并仔細(xì)選擇時(shí)鐘芯片后,也不能保證抖動(dòng)能夠完全符合芯片數(shù)據(jù)手冊(cè)上的參數(shù),很多其他的影響也會(huì)引入不必要的噪聲。因此,測(cè)試和故障排除是不可或缺的。

分析并消除抖動(dòng)不是一個(gè)簡(jiǎn)單的過程。采用優(yōu)秀的設(shè)計(jì)原則、選擇高質(zhì)量的元器件、用適當(dāng)?shù)膬x器對(duì)電路進(jìn)行檢測(cè)、采用系統(tǒng)的方法來分析解決所發(fā)現(xiàn)的問題,通常會(huì)得到令人滿意的結(jié)果。如果沒有做到這些,建議開發(fā)人員求助于時(shí)鐘芯片供應(yīng)商。基本上所有優(yōu)秀的公司都會(huì)提供設(shè)計(jì)和故障排除服務(wù),開發(fā)人員所獲得的經(jīng)驗(yàn)可用于下一個(gè)項(xiàng)目的時(shí)鐘電路設(shè)計(jì)。

-

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6677文章

2463瀏覽量

205108 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131675

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電子書:電源研發(fā)過程中常見的問題

頻譜分析儀在使用過程中常見故障匯總

電路設(shè)計(jì)的常見問題

線切割加工中常見問題處理

放大器電路設(shè)計(jì):如何避免常見問題

時(shí)鐘電路設(shè)計(jì)過程中常見問題分析

時(shí)鐘電路設(shè)計(jì)過程中常見問題分析

評(píng)論