聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

intel

+關注

關注

19文章

3483瀏覽量

186336 -

代碼

+關注

關注

30文章

4823瀏覽量

68918 -

性能

+關注

關注

0文章

271瀏覽量

19022

發布評論請先 登錄

相關推薦

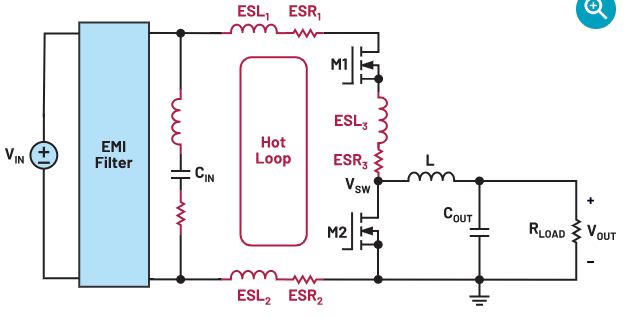

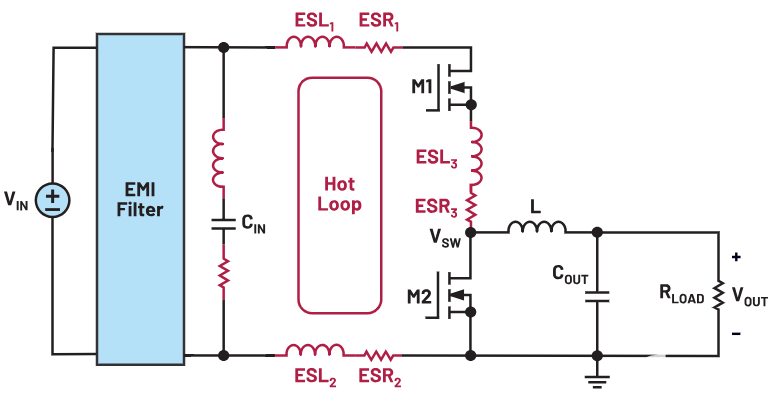

如何通過最小化熱回路PCB ESR和ESL來優化開關電源布局

如何通過最小化PCB的等效串聯電阻(ESR)和等效串聯電感(ESL)來優化熱回路布局設計。本文研究并比較了影響因素,包括解耦電容位置、功率FET尺寸和位置以及過孔布置。通過實驗驗證了分析結果,并總結了最小化PCB ESR和ESL

手動最小化前面板運行內存會驟降,而程序控制最小化不行

有個程序,剛打開運行時占內存140M左右,手動把前面板最小化就會降至20M左右,把前面板還原顯示后內存會逐漸升到60M左右,而如果我在程序里添加一個指令,就是按

發表于 08-11 23:55

PCB布局提示和技巧:最小化去耦電感

的作者的話來說,Hubing等。聲稱在某些條件下電容器的位置“不重要”,盡管他們可能已經將結論擴展到“研究的有效性范圍之外”。無論如何,這是電容器之間相互作用重要性的另一個例子。并且平

發表于 07-27 11:59

如何通過最小化熱回路來優化開關電源布局?

)。本文討論如何通過最小化PCB的等效串聯電阻(ESR)和等效串聯電感(ESL)來優化熱回路布局設計。本文研究并比較了影響因素,包括解耦電容位置、功率FET尺寸和位置以及過孔布置。通過實驗驗證了分析結果,并總結了最小化PCB E

如何通過最小化熱回路PCB ESR和ESL來優化開關電源布局

設計。本文研究并比較了影響因素,包括去耦電容位置、功率FET尺寸和位置以及過孔布局。通過實驗驗證了分析的有效性,總結了最小化PCB ESR和ESL的有效方法。

如何通過最小化熱回路PCB ESR和ESL來優化開關電源布局

設計。本文研究并比較了影響因素,包括去耦電容位置、功率FET尺寸和位置以及過孔布局。通過實驗驗證了分析的有效性,總結了最小化PCB ESR和ESL的有效方法。

從“正確”到“正確和有效”:一個最小化的案例研究

從“正確”到“正確和有效”:一個最小化的案例研究

評論