引言

當今,開放式數(shù)控系統(tǒng)正在工業(yè)領(lǐng)域得到廣泛應(yīng)用。其中,工控機通過PCI總線連接專用運動控制卡的數(shù)控系統(tǒng)最為流行。在運動控制卡中,由于DSP采用多總線哈佛結(jié)構(gòu)使得處理指令和數(shù)據(jù)可以同時進行,因此相比傳統(tǒng)控制中的單片機具有更多的優(yōu)勢。同時,運動控制卡與PC機通過PCI局部總線通信,能夠達到很高的數(shù)據(jù)傳輸速率,從而還保證了數(shù)控系統(tǒng)的實時性。

系統(tǒng)概述

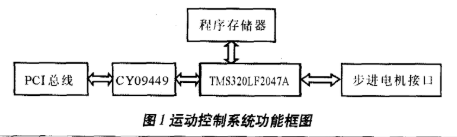

系統(tǒng)的功能框圖如圖1所示。該系統(tǒng)的核心是TI公司的16位定點DSP芯片TMS320LF2407A。DSP芯片負責(zé)接收PCI局部總線的命令和參數(shù),然后經(jīng)過特定的運動控制算法,如系統(tǒng)位置、速度調(diào)節(jié)、插補算法等,從而完成對步進電機的精確運動控制。同時DSP芯片還負責(zé)將反饋信息傳輸給PCI局部總線,并且控制系統(tǒng)外圍I/O模塊。DSP芯片與計算機的通信通過PCI橋接芯片CY09449實現(xiàn)。

DSP模塊

DSP芯片TMS320LF2407A采用高性能靜態(tài)CMOS工藝,供電電壓僅3.3V;指令周期縮短到33ns。

作為系統(tǒng)的核心,TMS320LF 2407A主要完成復(fù)雜的運動控制算法,比如升降頻控制、插入補償?shù)取1驹O(shè)計主要是完成雙軸步進電機控制,故插入補償采用經(jīng)典的DDA算法。由于本設(shè)計對步進電機采用無反饋控制,這樣對步進電機的升降頻控制就顯得格外重要,這也成了整個系統(tǒng)設(shè)計的一個難點。根據(jù)步進電機變速過程動力學(xué)特性,以指數(shù)曲線前段規(guī)律作為前后沿的近似梯形波,進而確定升降頻特性,這樣既能保證步進電機運行過程不會失步,又充分發(fā)揮了步進電機的固有性能,使升頻過程達到時間最短的要求。下面討論一下升降頻控制的算法實現(xiàn)。

升降頻控制

為實現(xiàn)所確定的運行頻率—時間函數(shù),通常是將其離散化,即將其轉(zhuǎn)換為脈沖時間間隔對脈沖個數(shù)的函數(shù)。另一種方法是按升降頻過程所走過的脈沖步數(shù)通過定步中斷來變頻。但是離散化方法既會引起頻率突跳和失步,又要進行復(fù)雜的迭代運算,而定步法同樣需要進行迭代。這兩種方法在DSP上都不易實現(xiàn)且靈活性較差。為此本文研究了一種稱為定時的方法。

設(shè)最高運行頻率為fh(電機恒速段的速度),升頻段總時間為ts。則根據(jù)步進電動機指數(shù)型升頻過程的頻率—時間關(guān)系:

f(t)=fM-(fM-fb)*exp(-t/T) (1)

式中fb為步進電動機起動頻率;fM為極限運行頻率;T為驅(qū)動系統(tǒng)時間常數(shù)

則有fh=f(ts)=fM-(fM-fb)*exp(-ts/T)

從而得到

ts=T*ln((fM-fb)/(fM-fh)) (2)

將ts等分為N段,得到各段時間為:ta=ts/N

則在第i個等分段ta內(nèi)脈沖切換頻率和要送出的脈沖數(shù)分別為:

f[i]=f(i*ta)=fM-(fM-fb)*exp(-i*ta/T)(3)

X[i]=ta*f[i] (4)

故升頻段的總步數(shù)為:

P=X[0]+X[1]+…+X[N-1] (5)

將脈沖間隔1/f[i]轉(zhuǎn)換為DSP內(nèi)部16位定時器的時間常數(shù)K[i]。轉(zhuǎn)換關(guān)系式為

K[i]=f_DSP/f[i], i=0,1,2…, N-1 (6)

由于降頻段特性變化規(guī)律與升頻段相反,可知降頻序列是升頻序列的逆序列。

電機在恒速步進階段,以fh的換相頻率步進。因此對應(yīng)的定時器時間常數(shù)為:

K[N]=f_DSP/fh (7)

恒速段總步數(shù)為:

X_h=X_total-2*P (8)

式中X_total為步進電機運動的總步數(shù)。

電機運行前,由主程序計算出升頻段和恒速段定時器時間常數(shù)序列K[i](i=0, …,N-1),存放于DSP的SARAM中,形成一個K-P升速表格。當電機運行時,在線查表,并取出K[i]用于設(shè)置DSP的PWM中周期寄存器的值,從而不斷改變PWM波形的周期,實現(xiàn)對電機的速度調(diào)節(jié)。根據(jù)升速、降速或高頻恒速,決定升速表地址指針增1、減1或不變。通過這種定時的方法,一方面提高了系統(tǒng)的靈活性,可根據(jù)輸入的最高頻率、起動頻率等參數(shù)改變升降速表,另一方面升降速表的求取不占用運行時間,從而提高了運行效率。

系統(tǒng)的部分軟件流程

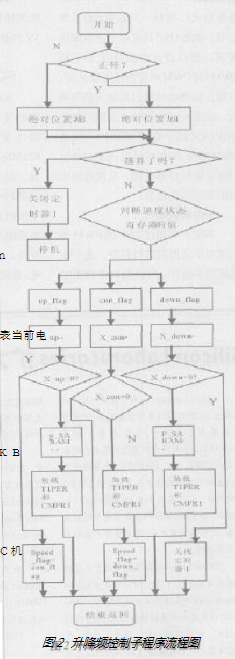

圖2為升降頻控制子程序流程圖,其中:p_SARAM為指向電機升降速時間常數(shù)表的指針,采用DSP的內(nèi)部SARAM來存放該表;X_up、X_con、X_down分別代表電機在升速段、恒速段、降速段要走的總步數(shù);up_flag、con_flag、down_flag分別代表當前電機的運動狀態(tài)(升速、恒速、降速)。

DSP與PC機的通信

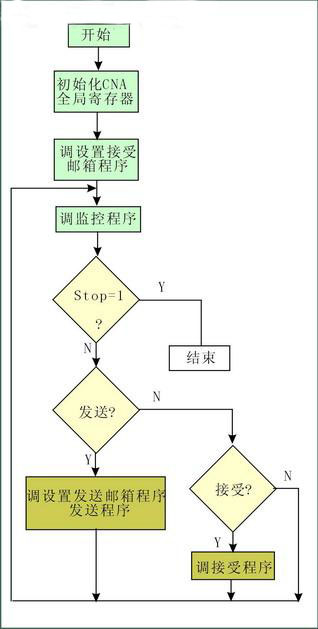

DSP與PC機的通信通過CY09449連接,CY09449內(nèi)部帶有128KB雙向靜態(tài)SRAM,為了在工作中,使PC機和DSP對SRAM的訪問不會發(fā)生沖突,本設(shè)計中把SRAM均分為兩個單元A和B, PC機和DSP對這兩部分的操作采用乒乓操作模式。由于DSP具有外部數(shù)據(jù)存儲器擴展能力,所以該SRAM完全可以作為DSP的外擴數(shù)據(jù)存儲器,這樣在設(shè)計中便采用DSP的外部數(shù)據(jù)存儲器有效信號/DS來作為CY09449的片選信號/SELECT。

DSP的編碼接口

本設(shè)計也考慮到如果需要對電機進行高級精確控制時,就需要對電機進行閉環(huán)控制。一般情況下,會運用光電編碼器作為系統(tǒng)的閉環(huán)反饋元件。由于本設(shè)計是針對雙軸步進電機的運動,而單軸的光電編碼器就輸出兩相相差為90°的脈沖信號A、B,以及歸零信號Z(都是差分形式),這樣一共就有6路反饋信號。但是DSP只有兩個正交編碼單元,所以設(shè)計中把DSP的引腳PWM9和PWM10設(shè)為通用輸入腳。這樣,反饋信號經(jīng)過高速光耦隔離后,就送入到DSP的正交編碼接口QEP1/QEP2、QEP3/QEP4,以及PWM9/PWM10,然后由DSP對該反饋信號進行計算處理,從而得出電機的實際運動信息。

步進電機接口

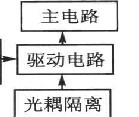

本設(shè)計中通過DSP的PWM單元來對步進電機進行控制。由于電機是功率器件,所以由DSP輸出的PWM波形不能直接輸入到驅(qū)動器中,而是必須采用光耦進行隔離,這樣才能避免電機的大電壓信號把DSP燒壞。此外由于DSP輸出的PWM信號很弱,如果直接加在電機驅(qū)動器上,驅(qū)動器將檢測不到該信號,所以在DSP的PWM信號輸出級需加長線驅(qū)動。本設(shè)計中采用了5V的差分長線驅(qū)動器AM26LS31。

PCI模塊

本系統(tǒng)選擇PCI局部總線作為DSP與上位機的通信方式,主要是因為PCI總線速率最高可達528Mbps,實時性強。PCI總線的開發(fā)一般可以有兩種方案實現(xiàn):一種是用FPGA實現(xiàn);另一種則是使用專用的PCI接口芯片。為節(jié)省時間本系統(tǒng)選擇專用芯片CY09449進行開發(fā)。該芯片采用3.3 V 單電源供電,兼容3V和5V 的PCI信號環(huán)境。CY09449的電源可由PCI槽引出,PCI槽可以提供3.3V、5V、12V電壓,在PCI槽有兩個引腳需特別注意:PRSNT1和PRSNT2,這兩個引腳接地和懸空的4種組合直接決定PCI卡的功率。CY 09449在使用時,某些引腳要加阻值為1k?~1Ok?的下拉或上拉電阻。根據(jù)本系統(tǒng)地具體情況在該設(shè)計中,SCL、SDA、ALE、/BE[2]、RDY_IN引腳加上拉電阻, TEST_MODE引腳加下拉電阻。

結(jié)語

基于PCI總線,配以數(shù)據(jù)處理能力強大的DSP設(shè)計的步進電機運動控制卡,在開放式數(shù)控系統(tǒng)中能夠發(fā)揮出理想的運動控制性能。隨著數(shù)控系統(tǒng)的普及和產(chǎn)品檔次的提高,這種運動控制卡將會有廣泛的應(yīng)用前景。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

349892 -

芯片

+關(guān)注

關(guān)注

456文章

51155瀏覽量

426301 -

工控機

+關(guān)注

關(guān)注

10文章

1753瀏覽量

50743

發(fā)布評論請先 登錄

相關(guān)推薦

TMS320LF2407和TMS320LF2407a 有什么區(qū)別啊。。。

基于TMS320LF2407A的調(diào)音器設(shè)計

如何使用TMS320LF2407A的bootrom

基于TMS320LF2407A和CY09449芯片設(shè)計的運動控制卡

基于TMS320LF2407A的全數(shù)字單相變頻器的設(shè)計及實現(xiàn)方法

TMS320LF2407A為數(shù)字控制系統(tǒng)的設(shè)計提供了參考

TMS320LF2407A 矢量控制變頻器的開發(fā)經(jīng)驗

基于TMS320LF2407A直流電機閉環(huán)調(diào)速控制系統(tǒng)的設(shè)計

TMS320LF2407A基于CAN總線技術(shù)的數(shù)字交流伺服系

基于DSP芯片TMS320LF2407A的全數(shù)字單相變頻器的

基于TMS320LF2407A和CY09449芯片實現(xiàn)運動控制卡的設(shè)計

基于TMS320LF2407A和CY09449芯片實現(xiàn)運動控制卡的設(shè)計

評論