信號源是指收音頭、高頻頭、錄音卡座、錄像卡座等器件。微機及輔助設備完成信號的提取、數模轉換、數字信號處理等功能。信號源是雷達系統的重要組成部分。雷達系統常常要求信號源穩定、可靠、易于實現、具有預失真功能,信號的產生及信號參數的改變簡單、靈活。信號發生器又稱信號源或振蕩器,是用來產生各種電子信號的儀器,在生產實踐和科技領域中有著廣泛的應用。傳統的RC或LC自激振蕩器方式的信號源組成較繁雜,調試較困難,不易實現程控,已不能適應新的要求;而由采用專用IC芯片構成的信號發生器。另外,采用FPGA+D/A可實現正弦信號發生器的設計,同時可實現頻率步進調節;但當輸出高頻信號時,需要高速D/A來配合工作,成本較高。頻率合成與鎖相技術的應用,可獲得高精度的信號源。目前,頻率合成技術是研制信號源的最關鍵技術。

該設計采用直接數字頻率合成(DDS)技術,使用DDS芯片AD9850與超低功耗的MSP430F149單片機配合,可輸出精確控制的正弦波和方波信號。AD9850是AD公司推出的低功耗直接數字頻率合成器芯片,可以產生從直流到62.5 MHz的寬頻率信號,從投放市場至今已廣泛應用于雷達系統、低功耗頻率源中;MSP430是TI公司開發的一類具有16位總線的帶FLASH的單片機,該設計將AD9850與MSP430F149結合提出一種具有較高性價比和集成度、低功耗的嵌入式信號源設計方案。在控制流程中,通過4x 4矩陣鍵盤設定頻率值,MSP430為AD9850計算頻率控制字,并且將頻率控制字通過串行方式寫入其中,結合鍵盤上步進調節增量"1 Hz","10 Hz","100 Hz"鍵,使得頻率可以精確到步長為1 Hz的調節;產生正弦波時,經過低通濾波器濾除信號的高頻分量,通過增益可調的寬帶放大器放大輸出所需信號。

1 系統設計

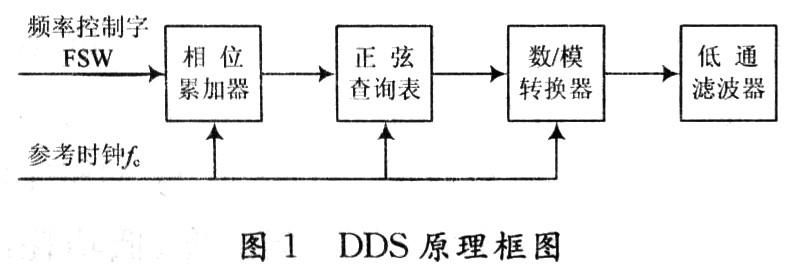

1.1 DDS技術原理與結構

DDS是一種全數字化的頻率合成器,由相位累加器、波形ROM、D/A轉換器和低通濾波器構成。時鐘頻率給定后,輸出信號的頻率取決于頻率控制字,頻率分辨率取決于累加器位數,相位分辨率取決于ROM的地址線位數,幅度量化噪聲取決于ROM的數據位字長和D/A轉換器位數。DDS有如下優點:⑴頻率分辨率高,輸出頻點多,可達個頻點(N為相位累加器位數);⑵頻率切換速度快,可達us量級;⑶頻率切換時相位連續;⑷可以輸出寬帶正交信號;⑸輸出相位噪聲低,對參考頻率源的相位噪聲有改善作用;⑹可以產生任意波形;⑺全數字化實現,便于集成,體積小,重量輕。DDS信號發生器通過改變相位增量寄存器的值△phase(每個時鐘周期的度數)來改變輸出頻率。每當N位全加器的輸出鎖存器接收到一個時鐘脈沖時,鎖存在相位增量寄存器中的頻率控制字就與N位全加器的輸出相加。在相位累加器的輸出被鎖存后,它就作為波形存儲器的一個尋址地址,該地址對應波形存儲器中的內容就是一個波形合成點的幅度值,然后經D/A轉換變成模擬值輸出。當下一個時鐘到來時,相位累加器的輸出又加一次頻率控制字,使波形存儲器的地址處于所合成波形的下一個幅值點上。最終,相位累加器檢索到足夠的點就構成了整個波形。合成信號的波形取決于ROM表中的幅度序列,通過修改數據可以產生任意波形,如果要產生多種波形,只需把所需的多種波形數據存放到波形ROM表中。

DDS系統輸出正弦波的頻率計算公式為:

式中:fo為輸出正弦波的頻率;fo為系統的時鐘頻率;FSW為頻率控制字;N為相位累加器的字長,頻率控制字與輸出頻率成正比。由取樣定理,所產生的信號頻率能超過時鐘頻率的50 %,在實際應用中,為了保證信號的輸出質量,輸出頻率不要高于時鐘頻率的33 %,以避免混疊或諧波落入有用輸出頻帶內。

DDS的頻率分辨率定義為:

由于基準時鐘的頻率一般固定,因此相位累加器的位數決定了頻率分辨率;位數越多,分辨率越高。

該信號源采用DDS專用芯片AD9850產生正弦信號。AD9850采用CMOS工藝,其功耗在3.3 V供電時為155 mW,擴展工業級溫度范圍為-40~+80℃,采用28腳SSOP表面封裝形式,AD9850內含可編程DDS系統和高速比較器,能實現全數字編程控制的頻率合成。AD9850支持的時鐘輸入最高為125 MHz,頻率控制字的位數為32位。由式(2)可以計算出在125 MHz時鐘輸入時分辨率為0.021 9 Hz,該設計中選用30 MHz的有源晶振,故其分辨率按式(2)計算得0.006 9 Hz.

1.2 系統總體設計

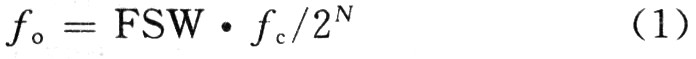

該系統采用MSP430F149對DDS進行控制構成方波正弦波信號源的系統框圖如圖2所示。

該信號源由MSP430F149單片機、DDS芯片AD9850、低通濾波器(LPF)、4×4軟鍵盤、1602液晶顯示屏和外部參考時鐘源、寬帶放大器和穩壓電源等組成。其中,低通濾波器是信號源中的關鍵器件,負責濾除正弦輸出信號中的高頻、雜散信號和諧波信號;穩壓電源的+5 V電壓經過電平轉換后為MSP430和AD9850提供+3.3 V的電源電壓;外部參考時鐘源選用30 MHz有源晶振,MSP430F149與AD9850采用串行通信方式連接。

1.3 硬件設計

MSP430是德州公司新開發的一類具有16位總線的帶FLASH 的單片機,由于其性價比和集成度高,受到廣大技術開發人員的青睞。它采用16位的總線,外設和內存統一編址,尋址范圍可達64K,還可以外擴展存儲器。具有統一的中斷管理,具有豐富的片上外圍模塊,片內有精密硬件乘法器、兩個16位定時器、一個14路的12位的模數轉換器、一個看門狗、6路P口、兩路USART通信端口、一個比較器、一個DCO內部振蕩器和兩個外部時鐘,支持8M 的時鐘。由于為FLASH型,則可以在線對單片機進行調試和下載,且JTAG口直接和FET(FLASH EMULATION TOOL)的相連,不須另外的仿真工具,方便實用,而且,可以在超低功耗模式下工作,對環境和人體的輻射小,測量結果為100mw左右的功耗(電流為14mA左右),可靠性能好,加強電干擾運行不受影響,適應工業級的運行環境,適合與做手柄之類的自動控制的設備。

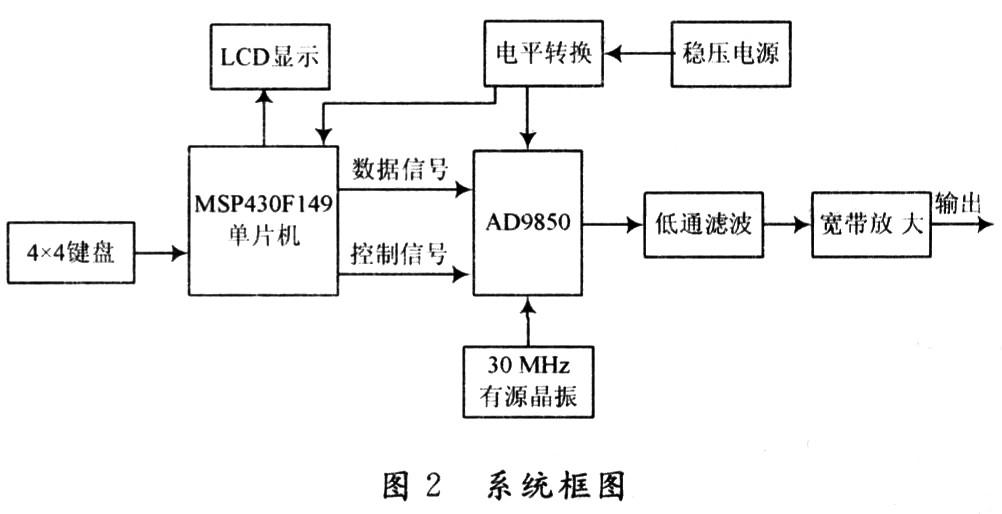

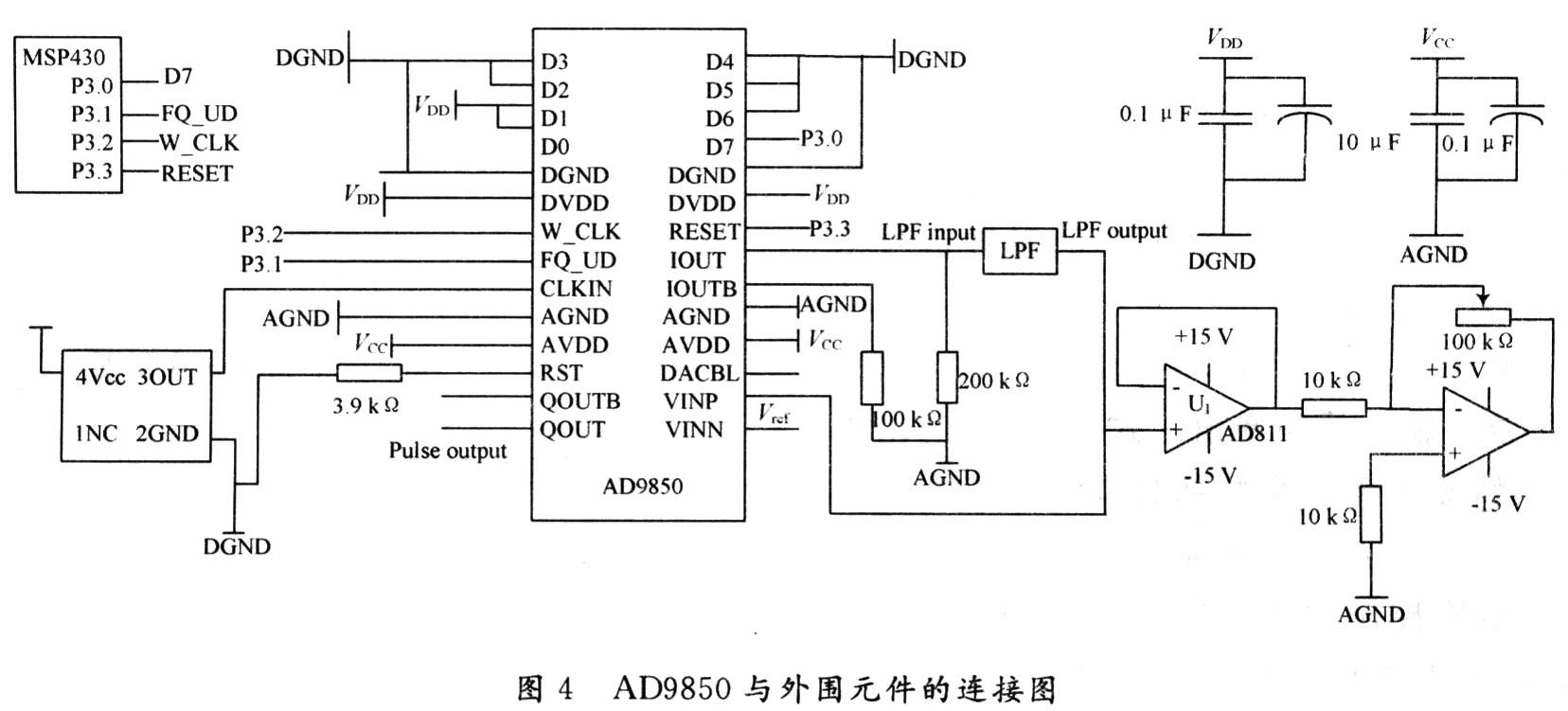

該信號源選用MSP430F149作為核心控制器,為了節省I/O資源,方便系統功能擴展,MSP430與DDS芯片AD9850之間采用串行通信方式,接口電路如圖3所示。AD9850與外圍元件的硬件連接圖如圖4所示,AD9851的正弦輸出信號端IOUT接至外部的低通濾波器,濾除高頻雜散和諧波后,一路信號經過寬大放大器AD811放大后輸出需要的正弦信號,另一路再回接到AD9851內部比較器的正向輸入端(VINP)以得到方波信號。其中:DGND為數字地;AGND為模擬地;VCC為模擬部分的電源電壓;VDD為數字部分的電源電壓。D7,FQ_UD,W_CLK,RESET分別接至MSP430的P3.0,P3.1,P3.2,P3.3上。為降低噪聲信號對放大器的影響,在低通濾波器與寬帶放大器之間接一級高速電壓跟隨器隔離,AD9850的輸出信號峰峰值為1~2 V,為增大AD9850輸出信號幅值,采用單位增益帶寬為140 MHz,Sr=2 500 V/μs的高速寬頻帶運放AD811進行信號放大,并且通過調節反饋電阻來改變增益,從而調節輸出信號幅度。放大電路的最大放大倍數,可以滿足一般的應用需求。

1.4 低通濾波器設計

對于不同濾波器而言,每個頻率的信號的減弱程度不同。當使用在音頻應用時,它有時被稱為高頻剪切濾波器,或高音消除濾波器。低通濾波器概念有許多不同的形式,其中包括電子線路(如音頻設備中使用的hiss濾波器、平滑數據的數字算法、音障(acousticbarriers)、圖像模糊處理等等,這兩個工具都通過剔除短期波動、保留長期發展趨勢提供了信號的平滑形式。低通濾波器在信號處理中的作用等同于其它領域如金融領域中移動平均數(movingaverage)所起的作用;低通濾波器有很多種,其中,最通用的就是巴特沃斯濾波器和切比雪夫濾波器。DDS的雜散主要以下三個方面:

(1)ROM幅度量化誤差:相位轉化為幅度,是通過尋址ROM實現的,然而ROM地址中存有的波形幅度值字長是有限的,ROM存儲能力有限而引起的舍位誤差就是幅度量化誤差;

(2)相位截斷誤差:為了提高DDS的精度,DDS的相位累加器位數都取得非常大,但ROM的容量是有限的,因此只利用相位累加器的高M位ROM尋址,其低(N-M)位被截斷。由此引入的截斷誤差是DDS雜散的主要;

(3)DAC的轉換誤差,即DAC中非線性引起的轉換誤差:DAC有限的分辨率、非線性特性以及轉換過程中出現的尖峰脈沖均會導致頻譜質量變壞。因此,低通濾波器的使用是非常必要的,其性能的優劣直接關系到整個DDS的技術指標。

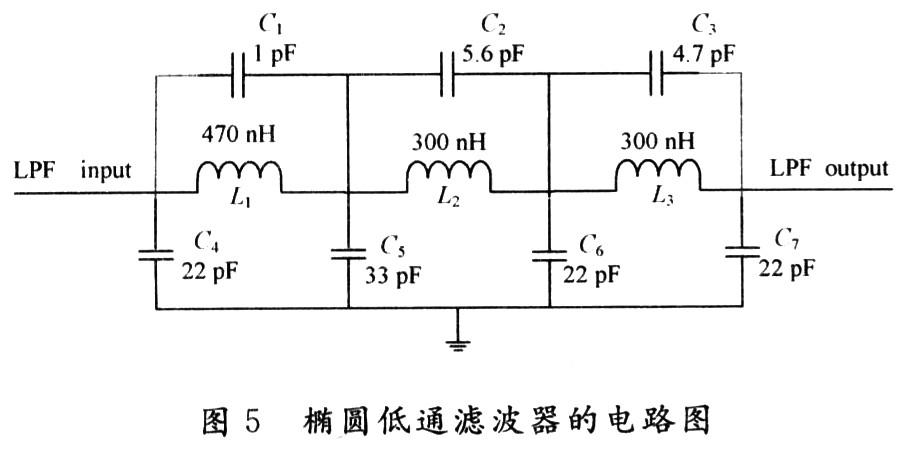

巴特沃斯濾波器是濾波器的一種設計分類,其采用的是巴特沃斯傳遞函數,有高通、低通、帶通、帶阻等多種濾波器類型。切比雪夫濾波器也是濾波器的一種設計分類,其采用的是切比雪夫傳遞函數,也有高通、低通、帶通、高阻、帶阻等多種濾波器類型。同巴特沃斯濾波器相添加圖片比,切比雪夫濾波器的過渡帶很窄,但內部的幅頻特性卻很不穩定。但是其過渡帶下降迅速,過渡帶很窄。在該系統中,為了使輸出信號頻率最高10 MHz時能夠最低程度地降低AD9850外部系統時鐘30 MHz的干擾,采用具有較窄過渡帶特性的橢圓濾波器,并采用7階橢圓低通濾波。根據系統要求,輸出信號的頻率可達10 MHz,設定其通帶為10 MHz,且7階濾波具有下降速度更快的過渡帶,可以有效地濾除10 MHz以上的高頻干擾。考慮到實際的橢圓濾波器設計與理論分析是有所不同的,在此使用Multisim 9經行仿真后得出橢圓濾波器的具體參數。橢圓低通濾波器的電路圖如圖5所示。

2 系統軟件設計

軟件設計主要分為菜單操作和頻率控制值計算兩部分。在系統中通過外接4×4軟鍵盤輸入設定頻率和調整步進。一共16個按鍵,不同的按鍵代表著不同的數字和功能,除了正常的10個數字鍵0~9外,為了方便頻率值的輸入,還設計了菜單鍵、刪除鍵、步進一、步進十、確認鍵、輸出鍵等功能鍵。通過輸入0~9數字鍵,輸入設定頻率;按下確認鍵,輸出相應頻率的波形;按下菜單鍵,可根據需要按下1,2,3數字鍵,分別選擇1 Hz,10 Hz,100 Hz三個檔位的頻率步進;按下確認鍵,此后按下步進+、步進一即可對輸出信號進行頻率的步進調整;欲重新設定頻率只需按下刪除鍵,再次輸入預設的頻率即可。

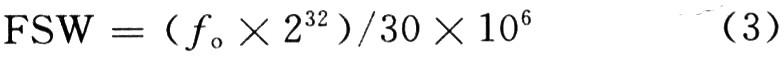

該系統中單片機與AD9850采用串行通信方式連接。其中,頻率控制字的計算:AD9850的時鐘信號采用30 MHz,根據式(1)得:

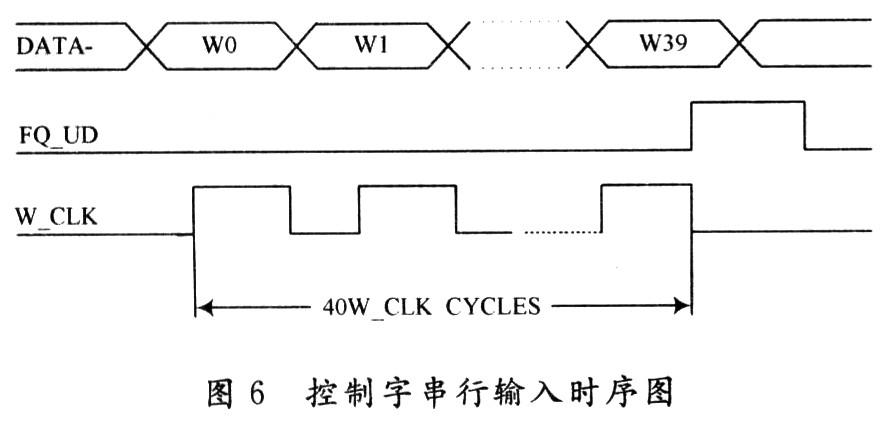

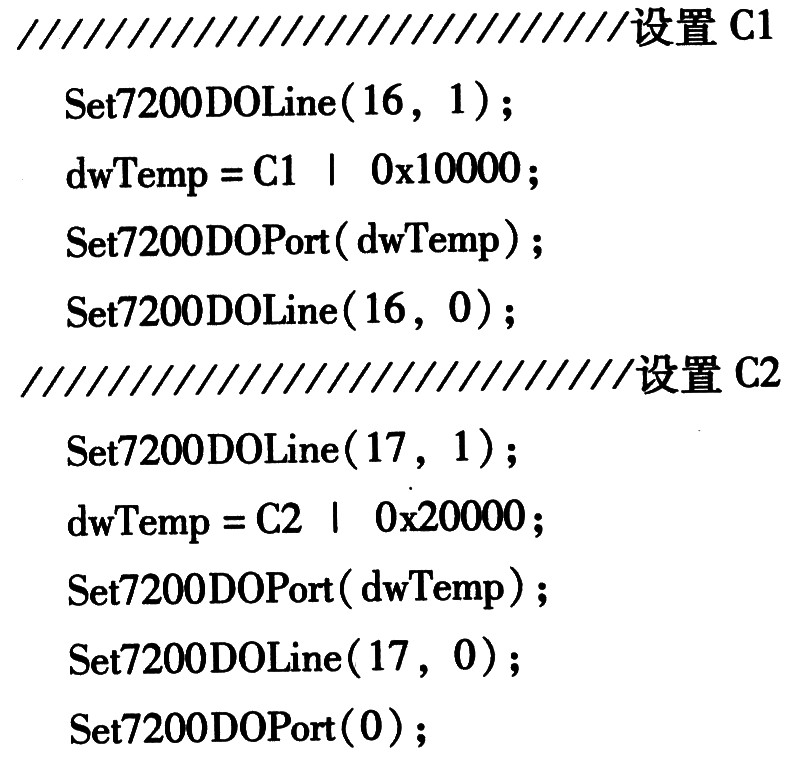

式中:fo為從鍵盤上輸入的頻率值。式(3)計算的結果在不影響精度的情況下舍去小數部分,轉換為32位的頻率控制字。AD9850有40位控制字,32位用于頻率控制,5位用于相位控制,1位用于電源休眠(PowerDown)控制,2位用于選擇工作方式。這40位控制字可通過并行方式或串行方式輸入到AD9850.實際應用中,工作方式選擇位通常設定成00,該系統中AD9850的40位控制字高8位設置為00H.串行接口方式下需滿足的時序關系為:在W_CLK的上升沿,引腳D7上的數據自最低有效位開始逐位串行移人輸入寄存器,40位數據輸入結束后,任何W_CLK上升沿到來,都會造成數據順序移出并導致原來數據無效。此時,FQ_UD端的上升沿將40位數據裝入頻率/相位控制寄存器,更新芯片的輸出頻率和相位,同時把地址指針復位到第一個輸入寄存器,等待下一組新數據的寫入。AD9850的控制字串行輸入時序圖如圖6所示。

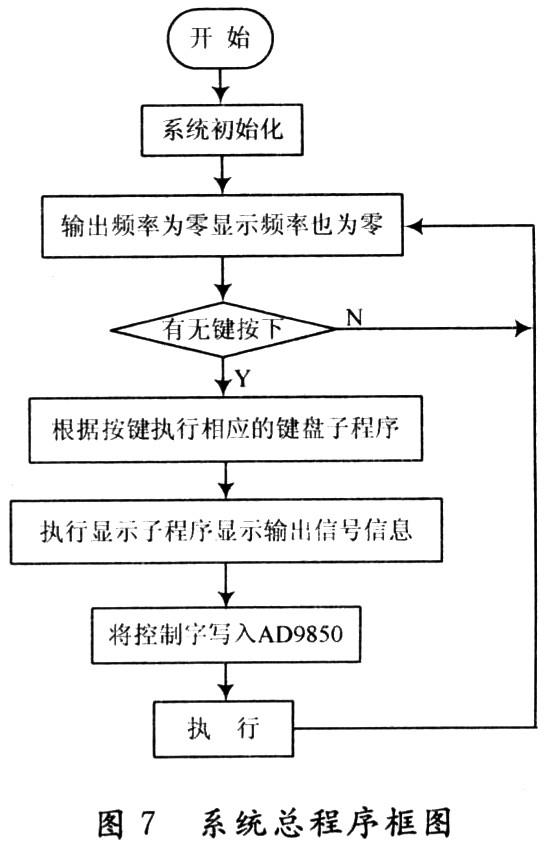

該系統的總程序框圖如圖7所示,程序開始后,運行初始化程序,包括初始化單片機MSP430F149、初始化AD9850、初始化液晶顯示模塊1602等。然后掃描鍵盤狀態,檢查到有鍵按下就運行鍵值處理程序,對按鍵值進行查表處理,之后執行相應的子程序。輸入的信號相關信息通過運行液晶顯示程序,在LCD上顯示正確的輸入數據和提示字符。在按下確認鍵后,MSP430F149計算出所需信號的數據或控制命令,將其傳送到AD9850,輸出最終信號。

3 系統測試與結果分析

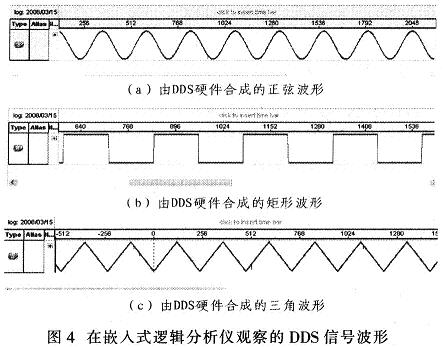

為了檢驗本系統的實際性能,在完成所有設計后,使用HDSTO22M型示波表對該系統進行實測,經過實驗測試系統達到下列性能指標:輸出信號頻率范圍為1 Hz~10 MHz;步進調整為1 Hz,10 Hz,100 Hz三檔步進;失真度無明顯失真;輸出電壓峰峰值為1~10 V;頻率穩定度優于10-4.

4 結 語

在此給出一種基于DDS芯片AD9850和MSP430F149單片機的嵌入式信號源設計方法,該信號源可輸出頻率范圍為1 Hz~10 MHz的正弦波和方波,且具有頻率設定1 Hz,10 Hz,100 Hz多檔步進調整和幅度調節的功能。可以通過按鍵進行頻率值設定,并有LCD顯示波形的頻率等信息,經實驗測試,在1 Hz~10 MHz頻率范圍內,得到的正弦波方波信號具有頻率穩定性好,頻率準確度高及頻率分辨率高等特點。

該設計的創新點在于:將DDS芯片AD9850與超低功耗的MSP430F149單片機結合,提出了具有較高性價比和集成度、低功耗的嵌入式信號源設計方案;并且AD9850與MSP430F149采用串行連接方式,節省單片機的I/O資源,便于系統的功能擴展和產品升級。該信號源具有精度高,頻率范圍寬,頻率輸出穩定,體積小,功耗低,控制靈活方便的特點,可廣泛應用于日常教學和科研工作中,如果再經過結構優化,將具有良好的市場前景。

-

單片機

+關注

關注

6042文章

44617瀏覽量

637566 -

轉換器

+關注

關注

27文章

8742瀏覽量

147749 -

嵌入式

+關注

關注

5090文章

19176瀏覽量

306892 -

濾波器

+關注

關注

161文章

7859瀏覽量

178694

發布評論請先 登錄

相關推薦

基于FPGA和DDS的信號源設計

DDS工作原理是?用DDS芯片AD9858寬帶雷達信號源要設計最佳?

基于DDS芯片AD9851的信號源設計與實現

單片機脈沖信號源的CPLD實現方案

基于DDS的雷達校準信號源設計

DDS器件AD9851在信號源中的應用

基于DDS技術的多路同步信號源的設計

基于AD9850_DDS芯片的寬頻信號源

基于AD9850 DDS芯片的寬頻信號源

DDS技術的原理介紹及用其和單片機進行嵌入式信號源的設計

DDS技術的原理介紹及用其和單片機進行嵌入式信號源的設計

評論