2.1項(xiàng)目背景及可行性分析

這個(gè)項(xiàng)目旨在利用JBits實(shí)時(shí)可重構(gòu)系統(tǒng)完成一個(gè)基于二維離散小波變換核的全面設(shè)計(jì)過(guò)程 ,這包括仿真 ,調(diào)試 ,以及搭建 硬件與可重構(gòu)計(jì)算平臺(tái)的接口。 JBits API的發(fā)展使對(duì)Xilinx 4000 系列和Virtex系列 器件配置比特流成為可能 。應(yīng)用JBits API, 設(shè)計(jì)者可以繞開(kāi)傳統(tǒng)的邏輯綜合和物理實(shí)現(xiàn)步驟 而允許高速比特流的重構(gòu)。比較于asic 使用JBits 可以創(chuàng)造更高性能的電路以用于實(shí)時(shí)可重構(gòu)系統(tǒng) 。因此 JBits API成為 設(shè)計(jì)一個(gè)有效的基于fpga的 實(shí)時(shí)可重構(gòu)和可進(jìn)化設(shè)計(jì)的必要工具。

2.2 應(yīng)用背景

隨著信息技術(shù)的飛速發(fā)展,計(jì)算機(jī)系統(tǒng)面臨的問(wèn)題越來(lái)越復(fù)雜,如何保證復(fù)雜系統(tǒng)的可靠性成為一個(gè)不容忽視的問(wèn)題。可進(jìn)化硬件給我們提供了一個(gè)很好的解決方案。可進(jìn)化硬件EHW(Evolvable Hardware)是將進(jìn)化算法和可編程邏輯元件融合在一起而產(chǎn)生的一種新的硬件研究流派。當(dāng)所使用的環(huán)境發(fā)生變化時(shí),或被放置于未知的環(huán)境中時(shí),這種硬件會(huì)自動(dòng)地改變內(nèi)部結(jié)構(gòu),使之經(jīng)常處于最適合狀態(tài),快速高效地完成規(guī)定的任務(wù)。

可編程門陣列(FPGA)以其獨(dú)有的優(yōu)點(diǎn)為國(guó)外多數(shù)研究人員用作硬件進(jìn)化平臺(tái)。EHW利用FPGA的在線可編程技術(shù)(ISP)及動(dòng)態(tài)重構(gòu)技術(shù),將FPGA的配置信息作為染色體,通過(guò)遺傳算法(GA)對(duì)其進(jìn)行反復(fù)的適應(yīng)度計(jì)算,交叉和變異,最終進(jìn)化出符號(hào)環(huán)境要求的個(gè)體(即電路配置),從而使電路適合環(huán)境的變化。

與此同時(shí),隨著FPGA技術(shù)的發(fā)展,芯片的性能越來(lái)越強(qiáng)、規(guī)模越來(lái)越大、開(kāi)發(fā)的周期越來(lái)越長(zhǎng),使得芯片設(shè)計(jì)業(yè)正面臨一系列新的 問(wèn)題:設(shè)計(jì)質(zhì)量難以控制,設(shè)計(jì)成本也越來(lái)越高。IP(Intelligence Property)技術(shù)解決了當(dāng)今芯片設(shè)計(jì)業(yè)所面臨的難題。IP是指可用來(lái)生成ASIC和PLD的邏輯功能塊,又稱IP核(IP Core)或虛擬器件(VC)。設(shè)計(jì)者可以重復(fù)使用已經(jīng)設(shè)計(jì)并經(jīng)過(guò)驗(yàn)證的IP核,從而專注于整個(gè)系統(tǒng)的設(shè)計(jì),提高設(shè)計(jì)的效率和正確性,降低成本。目前數(shù)字IP已得到了充分的發(fā)展,可以很方便地購(gòu)買到IP核并整合到SoC的設(shè)計(jì)中。

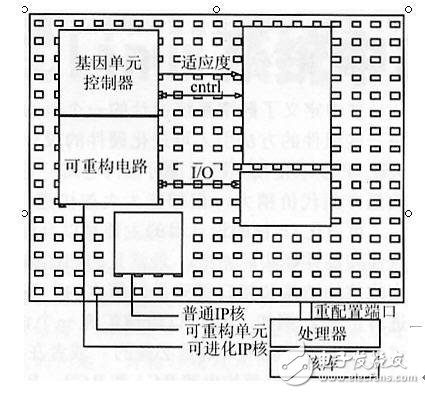

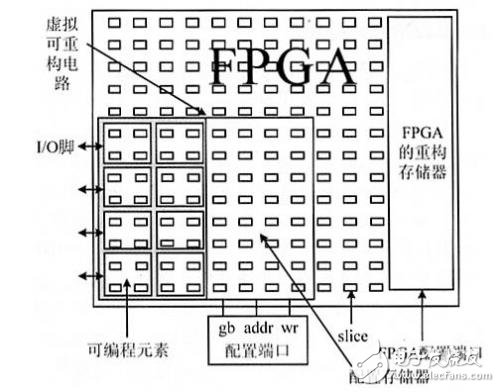

圖 1 FPGA 中的 可進(jìn)化ip核和 普通 ip核

因此,可以考慮將進(jìn)化硬件的思想應(yīng)用于IP核的設(shè)計(jì)中,設(shè)計(jì)一種可進(jìn)化的IP核,根據(jù)當(dāng)前的環(huán)境進(jìn)化出相應(yīng)的電路,并能夠在普通的可重構(gòu)器件中實(shí)現(xiàn)。

2.3 研究現(xiàn)狀

1 可進(jìn)化IP核

從進(jìn)化硬件的經(jīng)驗(yàn)可知,系統(tǒng)通常只有一部分是適應(yīng)性的(可進(jìn)化的),另一部分可以通過(guò)傳統(tǒng)的不可變的電路來(lái)實(shí)現(xiàn)。同樣,使用IP核構(gòu)造的系統(tǒng)也是有些IP核是可進(jìn)化的,有些IP核是不可變的。可進(jìn)化的那些IP核稱為可進(jìn)化組件或可進(jìn)化IP核。

可進(jìn)化IP核像普通的IP核一樣被存儲(chǔ)在組件庫(kù)中,在被下載并放在一個(gè)可重構(gòu)器件中后,它們將自動(dòng)地進(jìn)化它們的內(nèi)部電路。當(dāng)不再需要適應(yīng)性行為時(shí),可以從可重構(gòu)器件中刪除可進(jìn)化IP核。可進(jìn)化IP核和普通IP核的復(fù)用方式相同。

2 可進(jìn)化IP核的一般體系結(jié)構(gòu)

如圖1所示,可進(jìn)化IP核由可重構(gòu)電路,基因單元和控制器構(gòu)成(本文中可重構(gòu)電路是指可進(jìn)化IP核內(nèi)的一個(gè)部分;可重構(gòu)器件是指整個(gè)可重構(gòu)平臺(tái),如FPGA)。這里要強(qiáng)調(diào)的是,基因單元不包含適應(yīng)度計(jì)算,它只實(shí)現(xiàn)基因的操作、染色體存儲(chǔ)和適應(yīng)度存儲(chǔ)。適應(yīng)度的計(jì)算和環(huán)境由其它的核來(lái)提供。基因單元生成一些配置并上載到可重構(gòu)電路中去,環(huán)境對(duì)這些配置進(jìn)行評(píng)估,并將適應(yīng)度值發(fā)送給IP核。可進(jìn)化IP核實(shí)際上是一個(gè)由環(huán)境控制的電路生成器。

環(huán)境(由其它核提出)和可進(jìn)化IP核之間的通信如下:首先IP核被初始化(生成初始化種群),然后進(jìn)入如下無(wú)限循環(huán)——當(dāng)環(huán)境發(fā)生變化后,環(huán)境計(jì)算當(dāng)前電路配置的適應(yīng)度,并判斷電路是否適應(yīng)環(huán)境。如果染色體存儲(chǔ)器中的配置不可用,則向IP核發(fā)出控制信息,IP核開(kāi)始進(jìn)化。即基因單元把硬件配置信息作為染色體,根據(jù)適應(yīng)度對(duì)其進(jìn)行交叉、變異等遺傳操作,生成一個(gè)新的種群。環(huán)境對(duì)新種群進(jìn)行適應(yīng)度計(jì)算,并判斷是否有滿足當(dāng)前環(huán)境的個(gè)體(配置)。若沒(méi)有,向IP核發(fā)控制信息,遺傳單元繼續(xù)對(duì)電路配置進(jìn)行進(jìn)化,直至有滿足當(dāng)前環(huán)境的配置為止;若有,則將適應(yīng)度值發(fā)給IP核,IP核用這個(gè)新生成的最優(yōu)配置來(lái)重配置可重構(gòu)電路,并在染色體存儲(chǔ)器中保存當(dāng)前最優(yōu)配置及其適應(yīng)度值,等待來(lái)自環(huán)境的下一個(gè)請(qǐng)求。

環(huán)境總是要求下載當(dāng)前最優(yōu)的進(jìn)化電路,因此,IP核必須保存目前為止最優(yōu)的配置,并且在需要的時(shí)候提供出去。可進(jìn)化IP核總是屏蔽重構(gòu)過(guò)程,因此它對(duì)于外部環(huán)境來(lái)說(shuō)是不可見(jiàn)的。

對(duì)于一些特殊的應(yīng)用,必須為它們開(kāi)發(fā)專用的可進(jìn)化IP核,因?yàn)榉从硲?yīng)用的要求基因單元和可重構(gòu)電路的體系結(jié)構(gòu)將使進(jìn)化過(guò)程優(yōu)于一個(gè)隨機(jī)的搜索。由于適應(yīng)度計(jì)算是在IP核外進(jìn)行的,因此IP核原則上支持動(dòng)態(tài)適應(yīng)度函數(shù)和無(wú)限的進(jìn)化。可進(jìn)化IP核可以用軟件實(shí)現(xiàn)。

三 項(xiàng)目實(shí)施方案

3.1方案基本功能框圖

圖2 系統(tǒng)框圖

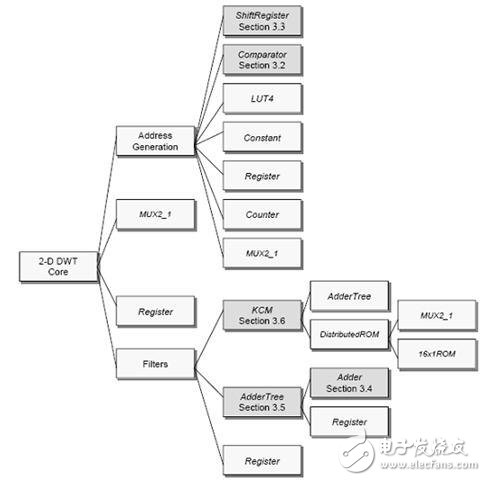

圖3 DWT2D核原理圖

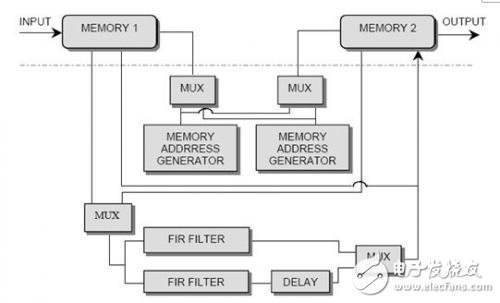

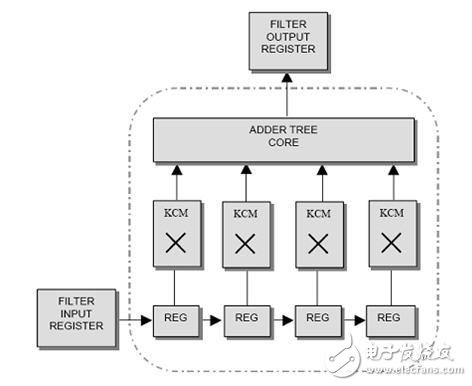

圖 4 由四個(gè)RTP核構(gòu)成的四拍FIR濾波器

1.硬件部分

可進(jìn)化IP核的實(shí)現(xiàn)

3.1 實(shí)現(xiàn)中的問(wèn)題

可復(fù)用的IP核通常有軟核、固核和硬核三種。本文討論的是軟核。本文的目標(biāo)是,設(shè)計(jì)和實(shí)現(xiàn)以HDL源代碼(例如,VHDL)表示的可進(jìn)化IP核。其優(yōu)點(diǎn)是IP核的表示獨(dú)立于平臺(tái),這樣它們就可以在各種不同的目標(biāo)結(jié)構(gòu)中運(yùn)行。要解決的主要問(wèn)題是,可進(jìn)化的IP核的內(nèi)部可重構(gòu)電路的自動(dòng)重構(gòu)(因?yàn)樗鼈兪强蛇M(jìn)化的)。

圖 5 用vertex slice 實(shí)現(xiàn)的虛擬可重構(gòu)電路

當(dāng)一個(gè)可進(jìn)化IP核從一個(gè)組件庫(kù)中被下載到可重構(gòu)器件的一個(gè)指定位置時(shí),它的內(nèi)部可重構(gòu)電路必須進(jìn)行重構(gòu)。這就意味著這個(gè)可重構(gòu)器件中的一些可編程塊必須能配置這個(gè)可重構(gòu)器件的其它內(nèi)部可編程塊。另外,這個(gè)可進(jìn)化IP核(它的基因單元)能被放置于這個(gè)可編程陣列(即可重構(gòu)器件)的任何位置,也就是說(shuō),這個(gè)可重構(gòu)器件中必須支持內(nèi)部重構(gòu)。

FPGA以其動(dòng)態(tài)可重構(gòu)的優(yōu)點(diǎn),無(wú)疑是可進(jìn)化IP核的最佳實(shí)現(xiàn)平臺(tái)。然而,通常的FPGA并不支持內(nèi)部重構(gòu),而只允許通過(guò)一個(gè)特殊的配置接口外部重構(gòu)(如圖5)。目前,只存在一種支持內(nèi)部重構(gòu)的平臺(tái),就是單元陣列,但這種芯片目前還相當(dāng)少。因此,為了在普通FPGA器件實(shí)現(xiàn)可進(jìn)化IP核,使之能在實(shí)際應(yīng)用中發(fā)揮作用,必須采用其它的一些方法。硬件虛擬化是基于FPGA的系統(tǒng)常用的一種設(shè)計(jì)技術(shù)。從這個(gè)思想出發(fā),本文采用了一個(gè)被稱為虛擬可重構(gòu)電路的技術(shù)來(lái)實(shí)現(xiàn)可進(jìn)化硬件中的內(nèi)部可重構(gòu)電路。但文中對(duì)設(shè)計(jì)虛擬可重構(gòu)電路的概念進(jìn)行了擴(kuò)展。

3.2 虛擬可重構(gòu)電路

一些FPGA芯片支持部分重構(gòu),也就是允許可重構(gòu)系統(tǒng)的一部分重構(gòu),而不影響其余部分的運(yùn)行。部分重構(gòu)的優(yōu)點(diǎn)在于,其重構(gòu)所花的時(shí)間比全部重構(gòu)更少。本文以支持部分重構(gòu)的Xilinx Virtex FPGA為例,來(lái)說(shuō)明虛擬可重構(gòu)電路的實(shí)現(xiàn)。IP核可以動(dòng)態(tài)地下載到FPGA或從FPGA刪除。所有的操作都通過(guò)Virtex重構(gòu)端口和Jbits接口來(lái)完成。當(dāng)一個(gè)可進(jìn)化IP核被下載時(shí),它的重構(gòu)位串在指定位置構(gòu)靠下列單元;虛擬可重構(gòu)電路、基因單元和控制器。

圖5表明,虛擬可重構(gòu)電路實(shí)際上是一種在普通FPGA上實(shí)現(xiàn)的新的可重構(gòu)電路。本例中由八個(gè)可編程元素構(gòu)成,由Virtex單元(slice)實(shí)現(xiàn)。Virtex單元實(shí)現(xiàn)新的可編程元素陣列、新的布線電路和新的配置存儲(chǔ)器。虛擬電路能內(nèi)部重構(gòu),但如果有其它新的配置存儲(chǔ)器與之連接,也可從FPGA的I/O引腳配置。

這種方法的優(yōu)點(diǎn)在于:可根據(jù)具體的應(yīng)用需要準(zhǔn)確地設(shè)計(jì)可編程元素陣列、布線電路和配置存儲(chǔ)器。虛擬可重構(gòu)電路的重構(gòu)方式和粒度能準(zhǔn)確地反映具體應(yīng)用的需要。通過(guò)虛擬可重構(gòu)電路,很容易把領(lǐng)域知識(shí)插入到基因單元和可重構(gòu)電路的體系結(jié)構(gòu)中,從而獲得電路軟件模型的精確實(shí)現(xiàn)。

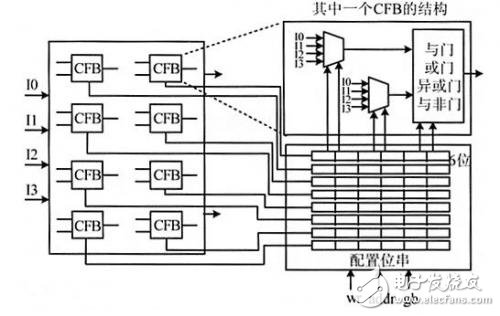

圖6給出了一個(gè)虛擬可編程元素的例子。這個(gè)虛擬可重構(gòu)電路由8個(gè)這樣的元素構(gòu)成,有4個(gè)輸入和2個(gè)輸出。這些虛擬可編程元素稱為可重配置功能塊CFB(Configurable Functional Blocks)。每個(gè)CFB對(duì)應(yīng)一個(gè)配置位串(這里的位串為6位),其中兩個(gè)配置位決定了CFB的功能,其它四位定義了輸入的連接信息。布線電路由多路器組成,它們由配置存儲(chǔ)器中的位串控制。配置存儲(chǔ)器由Virtex單元構(gòu)成,一個(gè)Virtex單元包含兩個(gè)觸發(fā)器,用于存儲(chǔ)配置位串中的兩位。配置存儲(chǔ)器的所有位都連到多路器,多路器控制布線和CFB中功能的選擇。

虛擬可重構(gòu)電路中CFB的數(shù)量由具體的應(yīng)用決定。虛擬可重構(gòu)電路用結(jié)構(gòu)級(jí)VHDL語(yǔ)言來(lái)描述,但是一些基本的電路(例如“MAX”電路)用行為級(jí)來(lái)描述。虛擬可重構(gòu)能在不同的目標(biāo)器件下綜合,目標(biāo)器件并不需要支持部分重構(gòu)。

圖 6 虛擬可重構(gòu)電路及其中一個(gè)CFB的實(shí)現(xiàn)

3.3 基因單元和控制器

基因單元和控制器的實(shí)現(xiàn)通常有兩種選擇:采用普通微處理器實(shí)現(xiàn),或者設(shè)計(jì)一個(gè)專用的電路來(lái)實(shí)現(xiàn)。

專用的電路是指一種進(jìn)化算法的硬件實(shí)現(xiàn),目前在可進(jìn)化硬件領(lǐng)域已經(jīng)開(kāi)發(fā)了很多這樣的實(shí)現(xiàn)。這種算法的優(yōu)點(diǎn)是電路的進(jìn)化速度快,適合于復(fù)雜的應(yīng)用。

采用微處理器實(shí)現(xiàn)時(shí),可以購(gòu)買或免費(fèi)獲得現(xiàn)成的微處理器軟核,如Xilinx提供的MicroBlaze和PicoBlaze微控制器IP核,Altera生產(chǎn)Nios核,等等。此外,如果給出的目標(biāo)可重構(gòu)器件中有片上處理器,可以使用片上處理器,Xilinx Virtex II Pro XC2VP50芯片包含四個(gè)PowerPC處理器。處理器必須通過(guò)編程來(lái)執(zhí)行程序,它們能和核周圍的環(huán)境進(jìn)行通信并完成對(duì)染色體的基因操作。此外,處理器還負(fù)責(zé)內(nèi)部虛擬可重構(gòu)電路的重構(gòu)。

2. 軟件部分

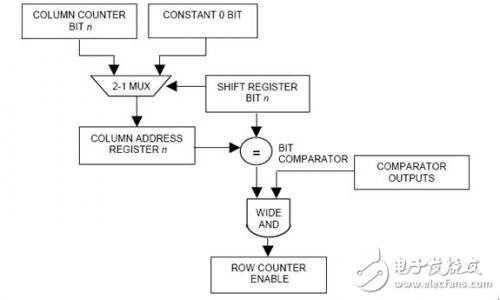

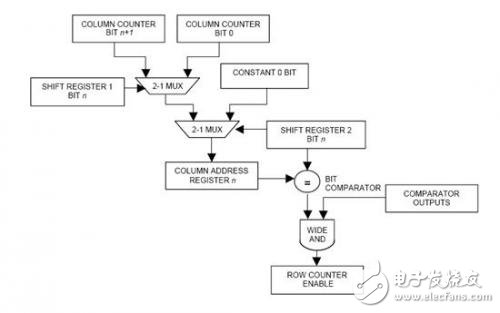

(1)bit n 的生成過(guò)程

圖 7 輸出地址bit n 的生成

圖 8 輸入地址bit n 的生成

(2)部分代碼

1 #Configuring F and G look-up tables with JBits

/* define row and column values */

int row = 5; int col = 4;

/* define logic function for F LUT */

int[] F_LUT_Vals = Expr.F_LUT(“~(F1&F2&F3&F4)”);

/* define logic function for G LUT */

int[] G_LUT_Vals = Expr.G_LUT(“~(F1|F2|F3|F4)”);

/* set the F LUT value for slice 0 */

jbits.set(row, col, LUT.SLICE0_F, F_LUT_Vals);

/* set the G LUT value for slice 1 */

jbits.set(row, col, LUT.SLICE1_G, G_LUT_Vals);

2 #: Adding and configuring an OutputCore

/* create a signal to run to the cross bar pins on the Slaac1V X2 */

Bus XBar = new Bus(“XP_XBAR”, null, 20);

/* create a new board */

Slaac1VBoard slaac1V = new Slaac1VBoard(“SLAAC1V”);

/* add a cross bar output core to slaac1V board instance */

int XBarOutput = slaac1V.addOutput(Xbar.getName(), XBar);

/* configure the IOB resources output operation */

slaac1V.setOutputInvertT(XBarOutput, true);

/* implement the slaac1V board */

slaac1V.implement(0, “slaac1V.ucf”);

3 #Code showing how Slaac1V SRAMs are distinguished through signal names.

/* define memory signals for Slaac1V X2 memories 0 and 1 */

Bus addr[] = new Bus[2];

Bus data[] = new Bus[2];

/* memory address */

addr[0] = new Bus(“XP_MEM0_ADDR”, null, 18); /* SRAM 0 */

addr[1] = new Bus(“XP_MEM1_ADDR”, null, 18); /* SRAM 1 */

/* memory data */

data[0] = new Bus(“XP_MEM0_DATA”, null, 12); /* SRAM 0 */

data[1] = new Bus(“XP_MEM1_DATA”, null, 12); /* SRAM 1 */

4 #AdderTree input index computations and partitioning process

/* calculate the “parent” adder index */

int log = (int) Math.ceil(Math.log((double)range)/Math.log(2.0));

int parentAdder = low + (int) Math.pow(2.0,log - 1);

/* calculate the right sided adder input index */

range = high - parentAdder;

log = (int) Math.ceil(Math.log((double)range)/Math.log(2.0));

int RHSIndex = ((int) Math.pow(2.0, log - 1)) + parentAdder;

/* calculate the left sided adder input index */

range = parentAdder - low;

log = (int) Math.ceil(Math.log((double)range)/Math.log(2.0));

int LHSIndex = ((int) Math.pow(2.0, log - 1)) + low;

/* partition left hand side of parent adder recursively */

AIndex[parentAdder - 1] = LHSIndex - 1;

deriveAdderTree(low, parentAdder);

/* partition right hand side of parent adder recursively */

if (RHSIndex != parentAdder)

{

BIndex[parentAdder - 1] = RHSIndex - 1;

deriveAdderTree(parentAdder, high);

}

else /* required if there is an odd number of tree inputs */

{

BIndex[parentAdder - 1] = treeInPort.length - 1;

}

5 # Slaac1VBoard.java code

public class Slaac1VBoard extends Board

{

public Slaac1VBoard(String name) throws CoreParameterException

{

super(name);

setXCVPackage(xcvPackage);

setGCLK(GCLK);

};

private XCVPackage xcvPackage[] =

{

new xcv1000_fg680(), new xcv1000_fg680(), new xcv1000_fg680()

};

private static int GCLK = 2;

}; /* end of Slaac1V board class. */

3.2 需要的開(kāi)發(fā)平臺(tái)

硬件平臺(tái)軟件平臺(tái)

PC機(jī)Linux

XUPV5-LX110T開(kāi)發(fā)板QT

ISE

ModelSim

Jbit

-

FPGA

+關(guān)注

關(guān)注

1630文章

21794瀏覽量

605129 -

soc

+關(guān)注

關(guān)注

38文章

4196瀏覽量

218782 -

IP

+關(guān)注

關(guān)注

5文章

1715瀏覽量

149802

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

圖像的二維離散小波變換問(wèn)題

怎樣去設(shè)計(jì)9/7二維離散小波變換系統(tǒng)?

基于DSP Builder的小波變換設(shè)計(jì)實(shí)現(xiàn)

二維DCT在粗粒度可重構(gòu)處理器上的實(shí)現(xiàn)

一種基于二維離散小波變換的醫(yī)學(xué)圖像增強(qiáng)算法

基于FPGA的二維提升小波變換IP核設(shè)計(jì)

關(guān)鍵基于二維小波變換的圖像矢量分解消噪方法

9/7二維離散小波變換的系統(tǒng)設(shè)計(jì)及FPGA實(shí)現(xiàn)

基于FPGA的快速9/7整形離散小波變換系統(tǒng)

圖像的二維提升小波變換的FPGA實(shí)現(xiàn)

雙運(yùn)算核提升小波變換的FPGA硬件實(shí)現(xiàn)

基于FPGA的快速9/7整形離散小波變換系統(tǒng)的設(shè)計(jì)過(guò)程與仿真

純二維雙正交偶對(duì)稱小波變換

多級(jí)二維整數(shù)小波變換的FPGA實(shí)現(xiàn)資料詳細(xì)說(shuō)明

升級(jí)!昊衡科技應(yīng)變場(chǎng)重構(gòu)軟件從二維擴(kuò)展到三維

基于FPGA二維離散小波變換核的實(shí)時(shí)可重構(gòu)系統(tǒng)的設(shè)計(jì)及仿真

基于FPGA二維離散小波變換核的實(shí)時(shí)可重構(gòu)系統(tǒng)的設(shè)計(jì)及仿真

評(píng)論