1 引言

在微弱信號檢測方法中,常需要使直流量經光電調制后轉變為交流信號進行測量,以扣除背景噪聲來提高系統信噪比。星載紫外遙感儀器同樣采用了壓頻轉換和調制解調實時扣除背景噪聲、零點飄移的方案,但其原有實現背景噪聲扣除功能的單元在與MCU接口及軟件控制上稍顯繁瑣,而且布線面積較大。如能將背景噪聲扣除功能設計成為具有通用接口和易操作的專用集成電路,對該儀器的升級換代有積極的意義。

硬件描述語言VerilogHDL 提供了是一種在廣泛的抽象層次上描述數字系統的方式,以其C語言風格,容易掌握等特點贏得了眾多硬件設計師的青睞。通過軟件編程來實現硬件功能后,下載到FPGA或CPLD大規模可編程邏輯器件,能將電路板級產品集成為芯片級產品。

為此,本文使用VerilogHDL進行編程,采用自頂向下的設計方法,經仿真驗證和綜合后,得到了具有通用接口和軟件易于操作的背景噪聲電路,彌補了原有單元的不足,取得了較好結果。

2 背景噪聲扣除電路原理

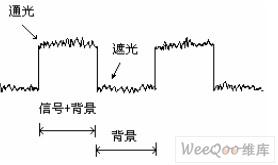

紫外光譜遙感儀器電控部分由斬光器,精密高壓電源及光電倍增管,單片機控制單元,同步累加解調單元,前置低噪聲放大器,壓頻轉換組成。其中斬光器將空間輻射光斬切成為交替的“信號+背景”和“背景”的光信號,使得光電倍增管輸出的信號如圖1所示。調制后的信號放大后,經壓頻轉化后變為頻率信號,通過同步累加單元的處理。同步累加解調單元采用四片四位二進制加減計數器SN54HC193進位位相連組成16位加減計數器,并配以邏輯門電路組成實現的。背景噪聲的扣除功能是依靠16位加減計數器由時序控制,在通光狀態下加計數,在遮光狀態下減計數,經多周期計數實現。

圖1經斬光器調制后由光電倍增管輸出的信號

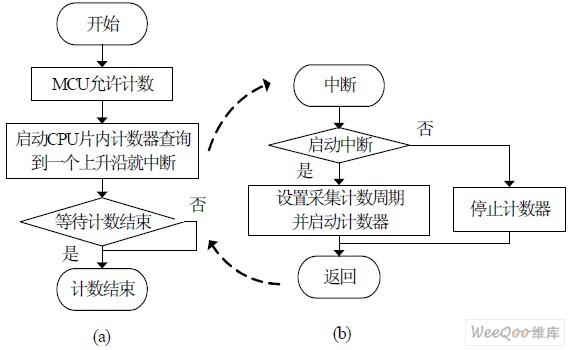

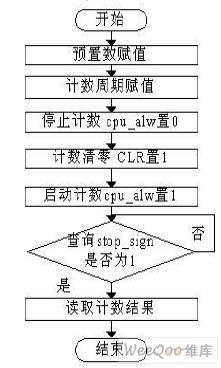

背景噪聲扣除原理簡單,但時序控制較繁瑣。原有電路因布線面積和硬件芯片不易過多等諸多考慮,計數周期及啟停控制采用軟件兩次中斷設置來實現。如圖2所示第一次為中斷本文課題于國家自然科學基金資助項目項目批準號:60538020為啟動計數,查詢到斬光器信號第一個上升沿時進入,設置好計數周期后再次啟動MCU片內計數器,以保證準確的查詢到第一個上升沿時啟動計數器。第二次為停止中斷,采集計數周期溢出后停止計數。

圖2 軟件控制采集計數啟停流程圖

(a) MCU查詢計數完成流程圖 (b)中斷執行計數器的啟停控制流程圖

易見原背景噪聲扣除功能單元需要與MCU接口的數據線較多,需16條,且因不同微處理器片內資源不同,軟件操作可能會更繁瑣,可移植性不強。

綜上,如果將背景噪聲扣除功能單元設計成一個8位數據總線接口,高低字節分時復用,能對16位二進制數預置數和計數周期進行設置,操作上僅由MCU給出啟動信號后,等查詢完成信號便可讀取計數結果的電路,則可大大減少線路板面積,使接口更簡單,提高可操作性和移植性。

3 背景噪聲扣除電路的VerilgHDL設計

依據自頂向下設計思想和自底向上的實現方法,背景噪聲扣除電路的可劃分為主模塊(backnoise_deduct),16位二進制加減計數模塊(bit16addsub),采集控制模塊(Ctrol),讀寫接口模塊(Addselec)四個模塊。

主模塊負責調用其它三個模塊,并將輸入輸出接口進行連接。16位二進制加減計數模塊負責在信號脈沖到來時,對給定的預置數在調制周期的高電平時加計數,在低電平時減計數。采集控制模塊負責當MCU給出允許計數命令后,自動查詢調制頻率的第一個上升沿啟動計數,在計數周期達到后停止計數,完成計數后通知MCU。讀寫接口模塊負責與MCU接口,接收儲存計數周期(斬光器信號或調制信號的周期數)和16位的預置數,并將最后計數結果返回MCU。

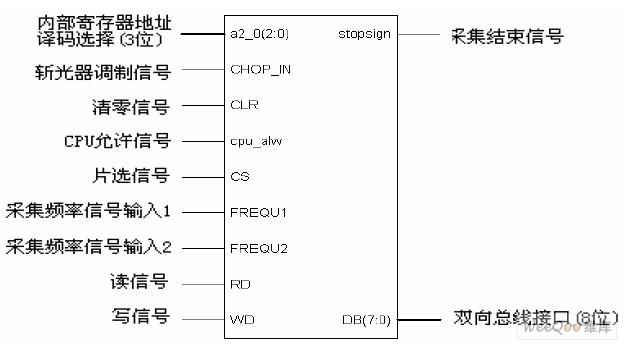

主模塊的外部接口如圖3所示。FREQU1, FREQU2為采樣頻率輸入1和2;CHOP_IN斬光器或調制頻率輸入,CLR為清零信號,高電平有效;cpu_alw為MCU發出的允許信號,高電平有效;stopsign是采集完成信號,高電平為完成;WD,RD,CS為是寫、讀、片選信號;DB為8位雙向數據總線;a2_0為3線片內寄存器地址譯碼選擇接口。

圖3 背景噪聲扣除主模塊綜合生成原理圖的外部接口

16位二進制加減計數模塊(bit16addsub)是背景扣除電路的具體實現單元,代碼如下所示。

module bit16addsub(

input wire FREQU,//采樣頻率輸入

input wire CHOP_IN,//斬光器輸入

input EN,//啟停控制

input wire CLR,//請零

input wire [15:0] STA_NUM,//初始數值

output reg[15:0] result_num //計數結果輸出

);

always @(posedge FREQU or posedge CLR)//對采集信號和清零信號敏感

begin

if(CLR==1)//清零

result_num<=STA_NUM;//重新讀入預置數

else if(EN==1&&CHOP_IN==1&&FREQU==1)

result_num<=result_num+1;//在使能的狀態下調制的信號高電平時加計數

else if(CHOP_IN==0&&EN==1&&FREQU==1)

result_num<=result_num-1;//在使能的狀態下調制信號的低電平時減計數

end

endmodule

采集控制模塊(Ctrol)是整個設計的時序控制核心,它輸出的ctrol與16位二進制加減計數模塊(bit16addsub)的EN向連接便可實現自動控制計數的啟動,待計數周期溢出時停止,計數完成后由stopsign后給出高電平信號通知MCU。其完整代碼如下:

module Ctrol(input wire reset, //復位信號

input wire cpu_alw, //MCU允許信號

input wire chop_in, //斬光器輸入計數

input wire [16:0] status_in, //計數周期數值

output reg ctrol, //加減計數器的啟停控制信號

output reg stopsign //計數完成信號

);

reg [16:0]num_count;//內部計數周期寄存器

always @(posedge reset or posedge chop_in)

begin

if(reset)//復位

begin

num_count<=status_in; //讀入計數周期

ctrol<=0;??????????? //停止計數

stopsign<=0;???????? //沒有完成計數

end

else if(chop_in==1&&cpu_alw==1)//允許計數

begin

if(num_count>0) //采集未完成

begin

ctrol<=1;????????? //16加減計數器使能

num_count<=num_count-1;//計數周期減一

end

else

begin

ctrol<=0;?????????? //計數停止

stopsign<=1;??????? //通知MCU

end

end

end

endmodule

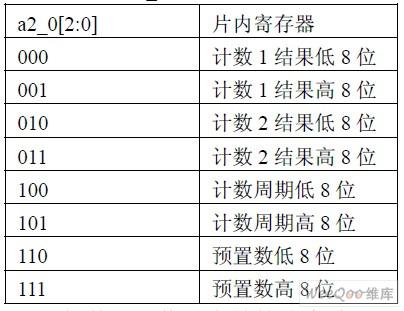

讀寫接口模塊(Addselec)在編程時采用通用的雙向數據總線輸入輸出方法,經過a2_0的3線譯碼選擇寄存器地址,可對計數周期和預置數進行賦值,并可讀出最后計數結果。表1給出了譯碼對應的寄存器地址。

表1 a2_0譯碼選擇真值表

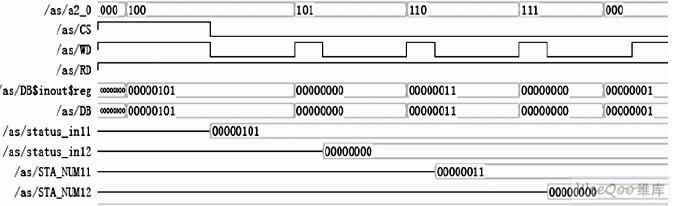

圖4給出了使用ModelSim 軟件對寫信號有效的仿真波形,顯示最后計數周期低、高8位寫入的數值為00000101、00000000,預置數低、高8位數值為00000011、00000000。

圖4 計數周期和預置數在總線寫入時的波形仿真結果

4背景噪聲扣除電路與MCU接口及軟件操作

圖5背景噪聲扣除電路的軟件操作流程

采用上述設計的集成背景噪聲扣除電路在與MCU接口時十分方便。以MCS51系列單片機8051為例,最簡單的連接方式為采用P1口與CLR、cpu_alw、stop_sign相連接,址線與CS、a2_0連接(可據電路規模設置片選方式),數據線、讀寫正常連接即可。軟件操作不需要中斷,操作流程如圖5所示。更簡單的做法是在系統初始化時將預置數和計數周期賦值為固定值即可。

5 結束語

本文介紹了采用計數器與門電路組成的背景噪聲扣除電路的實現原理和工作方式,并分析了其局限性,然后提出了一種基于VerilogHDL 語言的背景噪聲扣除電路的設計,使電路接口更為簡單,軟件更易操作,增強了移植性。該設計已經應用于在研的紫外遙感儀器中,為儀器的更新換代提供了技術支持。本文以通用性和簡便性出發設計的背景噪聲扣除電路的設計,將適用于以光電調制微弱直流量轉換為交流信號測量的方案。

本文作者創新點:針對原有背景噪聲扣除功能單元的局限性,用VerilogHDL語言設計出了接口方便、易操作的背景噪聲扣除電路,使其有具備了較強的通用性和適用性。

-

芯片

+關注

關注

456文章

51155瀏覽量

426442 -

放大器

+關注

關注

143文章

13627瀏覽量

214032 -

mcu

+關注

關注

146文章

17316瀏覽量

352311

發布評論請先 登錄

相關推薦

用TLV320ADC3101芯片做語音的ADC轉換,有比較大的背景噪聲怎么解決?

PIN管運放兩級放大,第一級引入背景噪聲,怎么去除?

無源壓電蜂鳴器背景噪聲消除

簡單的輸入接口電路設計細節分析

求一種基于VerilogHDL語言的背景噪聲扣除電路的設計

TMS320C6713在雙通道數字去噪聲系統中的應用解析

基于利用LMV1088麥克風數組放大器消除語音通信系統中背景噪聲

聯發科技攜手合作伙伴共建AIoT生態

采用高CMRR差分放大器消除應用中視頻信號的背景噪聲

精密測量院在利用高精度超導重力儀提取微弱背景噪聲信號方面獲進展

接口簡單且易操作的VerilogHDL的背景噪聲扣除電路設計

接口簡單且易操作的VerilogHDL的背景噪聲扣除電路設計

評論