在設計基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設備進行輸入輸出信號的測試,借助測試探頭把信號送到測試設備上進行觀察分析。當然,前提是需要保留足夠多的引腳,以便能選擇信號來驅動I/O進行測試。但是外部的測試設備在測試FPGA系統(tǒng)時,常會遇到這樣的情況:FPGA的I/O引腳數(shù)量不夠豐富,PCB布線和封裝丁藝復雜導致I/O引腳引出困難,外部測試探頭有影響FPGA信號時序和完整性的可能。

如果能在FPGA內(nèi)部嵌入具有外部測試設備功能的邏輯測試模塊,那么以上問題就可以一一解決。SignalTapII就是這樣一種嵌入式邏輯分析器(embedded logicanaIyzer),簡稱為SignalTapII ELA。它是QuartusII軟件中集成的內(nèi)部邏輯分析軟件,使用它可以實時觀察內(nèi)部信號波形,方便用戶查找設計的缺陷。

1 SignalTapII ELA的原理

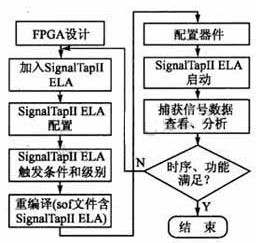

SignalTapII ELA是Quartus軟件中第二代系統(tǒng)級調(diào)試工具。將SignalTapII ELA代碼和系統(tǒng)邏輯代碼組合交由QuartusII編譯、綜合、布局布線,生成sol文件中內(nèi)含SignalTapII ELA,把sof文件配置到FPGA內(nèi)。FPGA運行時,一旦滿足待測信號的觸發(fā)條件,SignalTapII ELA就立即啟動,按照采樣時鐘的頻率捕獲待測信號數(shù)據(jù)并暫存于FPGA片內(nèi)的RAM中,采樣數(shù)據(jù)不斷刷新片內(nèi)存儲器,最后通過JTAG口將捕獲的信號從片內(nèi)RAM傳至Quartus II實時顯示。SignalTapII ELA的原理流程如圖1所示。

實際工程中,加入SignalTapII ELA不會影響系統(tǒng)原有的邏輯功能。

2 SignalTapII ELA的配置

SignalTapII ELA基本配置過程如下:

①添加采樣時鐘。SignalTaplI ELA在時鐘的上升沿進行采樣,可以使用設計系統(tǒng)中的任何信號作為采樣時鐘,根據(jù)Altera公司的建議最好使用同步系統(tǒng)全局時鐘作為采樣時鐘。但是在實際應用中,多數(shù)使用獨立的采樣時鐘,這樣能采樣到被測系統(tǒng)中的慢速信號,或與工作時鐘相關的信號。當然采樣時鐘的頻率要大于被測信號的最高頻率,否則被測信號波形會有較大誤差。

②定義采樣深度。采樣深度決定了待測信號采樣存儲的大小,而可以采樣的深度是根據(jù)設計中剩余的RAM塊容量和待測信號的個數(shù)決定的。若待測信號較多,則在同樣I/O Bank個數(shù)情況下采樣深度較淺。待測信號個數(shù)的增減和采樣深度的深淺會直接改變RAM塊的占用情況,采樣深度的范圍為0~128 KB。

③定義RAM類型。設置占用片內(nèi)何種RAM塊資源,隨著采樣深度的改變,RAM塊的數(shù)據(jù)線和地址線寬度可以分割成多種組合。例如:采樣深度是1 KB,RAM數(shù)據(jù)線、地址線可以分割成2×512或4×256等多種組合。依此類推。

④定義觸發(fā)位置。Pre trigger position表示采樣到的數(shù)據(jù)12%為觸發(fā)前,88%為觸發(fā)后;Center trigger position表示采樣的數(shù)據(jù)處于觸發(fā)前后各一半;Post trigger position表示采樣到的數(shù)據(jù)88%為觸發(fā)前,12%為觸發(fā)后。

⑤觸發(fā)條件級數(shù)設置。SignalTapII ELA支持多觸發(fā)級的觸發(fā)方式,最多可支持10級觸發(fā),幫助濾除不相干的數(shù)據(jù),更快地找到需要的數(shù)據(jù)。若有多級觸發(fā)條件,首先分析第一級觸發(fā)條件。若第一級為TRUE,則轉到分析第二級是否滿足,直到分析完所有觸發(fā)條件均為TRUE才最終觸發(fā)時鐘采樣數(shù)據(jù)。

⑥觸發(fā)條件。設定約束性的觸發(fā)條件。可以允許單個信號的獨立觸發(fā)條件Basic,直接采用單個外部或設計模塊內(nèi)部的信號;也可以允許多個節(jié)點信號的組合觸發(fā)條件Advanced,構成觸發(fā)函數(shù)的觸發(fā)條件方程。例如:使能信號ENA與4位輸出信號Q相與后觸發(fā),觸發(fā)條件=ENA&(Q=15)。

⑦添加待測信號。可以使用Node Finder中的SignalTapII ELA Filter查找所有預綜合和布局布線后的SignalTapII ELA節(jié)點,添加待測的中間信號和端口信號。SignalTapII ELA不可測試的信號包括:邏輯單元的進位信號、PLL的時鐘輸出、JTAG引腳信號、LVDS(低壓差分)信號等。

完成STP配置,將sof文件配置到FPGA,運行SignalTapII ELA,當待測信號條件滿足時,數(shù)據(jù)捕獲開始,捕獲的數(shù)據(jù)以波形的形式表示出來。SignalTapII ELA也可將捕獲數(shù)據(jù)通過多余的I/O引腳輸出,以供外部的測試設備使用。

3 實例分析

本文以一個基于DDR SDRAM高速數(shù)據(jù)采集IP核的設計為例,具體說明如何用SignalTapII ELA來進行FPGA在線調(diào)試。使用Altera公司的器件CyclonelI系列FPGA EP2C5F256C6,該器件支持SignalTap II ELA。

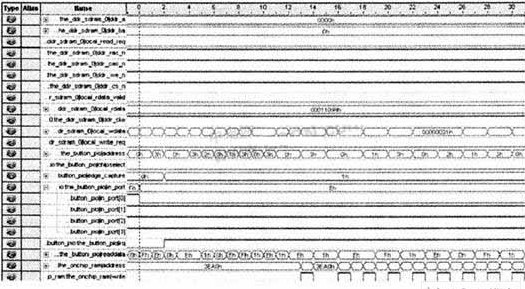

當前需要測試來自3個模塊的信號:外部存儲器DDR SDRAM與FPGA的接口信號、FPGA內(nèi)部輸入輸出PIO寄存器信號、FPGA內(nèi)部RAM接口信號。

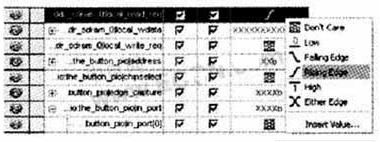

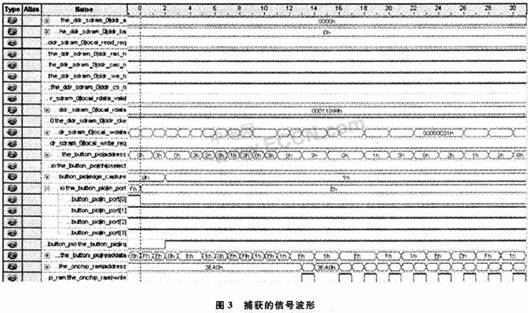

先關閉增量編譯,設置采樣時鐘為外部獨立時鐘CLK=50 MHz;采樣深度為256;RAM類型為M4K,數(shù)據(jù)寬度分割為256×1;觸發(fā)位置為Pre trigger position;觸發(fā)信號為DDR SDRAM讀操作信號;觸發(fā)條件為Basic單信號觸發(fā);觸發(fā)條件級數(shù)為1級。從圖2可知,該觸發(fā)信號設置為上升沿觸發(fā)有效。重新編譯后將包含SignalTapIIELA的sof配置文件下載到FPGA中,圖3即是從SignalTap II ELA數(shù)據(jù)窗觀察到的來自FPGA內(nèi)部實時信號的捕獲波形。

如果設計文件中添加SignalTapII ELA后編譯時間顯著增加,可以考慮使用Start Analysis&Elaboration代替Start Analysis&Synthesis,這樣可以顯著縮短編譯時間。

加入SignalTapII ELA后,如果發(fā)現(xiàn)一些用于調(diào)試的邏輯(比如調(diào)試用的計數(shù)器)被優(yōu)化掉,不能出現(xiàn)在波形中,可以嘗試這樣解決:在HDL設計文件中對要調(diào)試的信號添加保持或保護屬性。

保持屬性主要用于信號和網(wǎng)絡節(jié)點。代碼如下(以VHDL為例):

signal my_signal:bit;

attribute syn_keep:boolean;

attribute syn_keep of my_signal signal is true;

保護屬性主要用于寄存器。代碼如下(以VHDL為例):

signal my_reg:std_logic;

attribute preserve:boolean;

attribute preserve of my_signal:signal is true;

通過改變待測信號的觸發(fā)方式和條件,可以捕獲到其他相類似的信號波形,這里就不一一列舉。

需要注意的是,SignalTapII ELA本身是一塊獨立邏輯資源,需要占據(jù)FPGA資源。比如RAM、LE等,資源消耗量與需采集的數(shù)據(jù)量成正比,采集存儲的數(shù)據(jù)深度由設計中的內(nèi)部RAM剩余大小決定。在調(diào)試完成后,需將SignalTapII ELA從系統(tǒng)邏輯設計中移除,以免浪費資源和影響設計的性能。

結 語

通過對FPGA內(nèi)部信號的捕獲測試,可以實現(xiàn)對系統(tǒng)設計缺陷的實時分析和修正。與外部測試設備相比,可以總結出SignalTapII ELA的幾點優(yōu)越性:不占用額外的I/O引腳,不占用PCB上的空間,不破壞信號的時序和完整性,不需額外費用;從多方面證實,該測試手段可以減少調(diào)試時間,縮短設計周期。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605246 -

pcb

+關注

關注

4324文章

23159瀏覽量

399330 -

示波器

+關注

關注

113文章

6281瀏覽量

185665

發(fā)布評論請先 登錄

相關推薦

如何對DSP設計進行實時分析?

實用FPGA的調(diào)試工具—ChipScope Pro

用FPGA動態(tài)探頭與數(shù)字VSA對DSP設計實時分析

SignalTapII ELA設計的FPGA在線調(diào)試技術

SignalTapII ELA調(diào)試工具實現(xiàn)對FPGA設計缺陷的實時分析和修正

SignalTapII ELA調(diào)試工具實現(xiàn)對FPGA設計缺陷的實時分析和修正

評論