1 引言

有兩種基本的數字化采樣方式:實時采樣(real-time sampling)與等效采樣(equivalent time sampling)。實時采樣對波形逐點采集,可以實時顯示輸入信號的波形,因此適用于任何形式的信號波形,重復或者不重復的,單次的或者連續的。由于所采集的樣點是按時間順序的,因而易于實現波形的顯示功能;實時采樣的主要缺點是時間分辨率較差。每個樣點的采樣、量化、存儲必須在小于采樣間隔的時間內完成。根據Nyquist 采樣定理為能夠完成的重建波形采樣頻率至少應為信號最高頻率的2倍,因此對實時采樣提出了更高的要求。鑒于此出現了等效采樣技術。等效采樣技術可以實現很高的數字化轉換速率。其基本原理就是通過多次觸發,多次采樣而獲得并重建信號波形。前提是信號必須是重復的。等效采樣通過多次采樣,把在信號的不同周期中采樣得到的數據進行重組,從而能夠重建原始的信號波形。

2 等效采樣的原理和方法

等效采樣的基本原理是把高頻、快速信號變成低頻、慢速重復信號。一般在重復信號的每個周期或相隔幾個周期取一個樣,而每個取樣點分別取自每個輸入信號波形不同的位置上,若干個取樣點成為一個周期,可以組成類似于原信號的一個周期的波形,但是周期拉長了。例如采集一個靜止圖像幀數據(采樣每秒30 幀標準)的采樣方案。假定一幅畫面的帶寬是6MHz.采用實時采樣方式,感覺采樣定理,采樣頻率應為12MHz。如果采用等效時間采樣方式,可以采樣100kHz 的模數轉換器,每隔120 個像素采樣一次,幀間采樣率稍低于100kHz保證挪后一個像素。則對第一幀采樣的結果是1,121,241…像素的數據,第二幀則是2, 122,242…像素的數據。這樣持續4 秒,采集120 幀數據,從而得到400k 的整個圖像幀數據。顯然再這個過程中我們利用了畫面的靜止特性,也就是利用了信號的重復性。

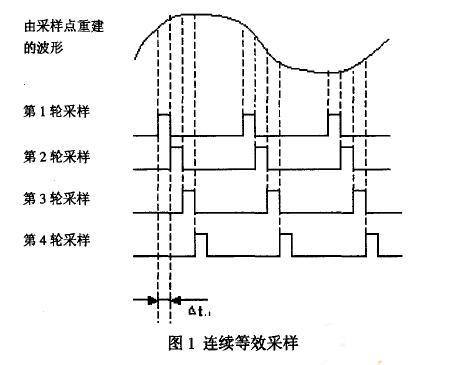

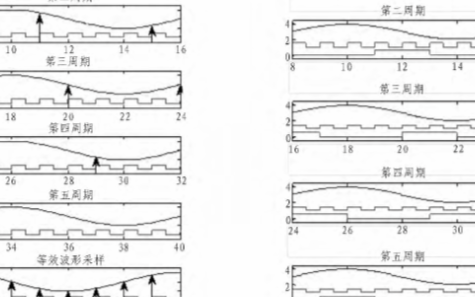

有兩種等效采樣的方法:隨機等效采樣和連續等效采樣。連續等效采樣在每個觸發捕獲一個樣值,而不依賴于時間/格的設置和掃描速度,每發現一個觸發經過一個雖然很短卻明確的延遲(deltat) ,就獲得樣值。當發生下一次觸發肘,延遲增加一段小的增量△t。這個增量就是等效樣的周期。數字轉換器則又采下一個樣值。該過程重復多次. deltat 不斷增加到前一個捕獲量中,直到時間窗口填滿。如圖1 示:

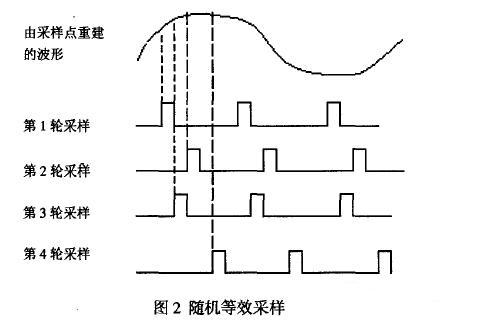

隨機等效采樣采用內部的時鐘,它與輸入信號和信號觸發的時鐘不同步,樣值連續不斷的獲得,而且獨立于觸發位置。通過記錄采樣數據與觸發位置的時間差來確定采樣點在信號中的位置來重建波形。這就產生了準確測量與采樣觸發點相關的位置的問題。這是隨機等效采樣的難題之一。盡管采樣在時間上是連續的,但是相對于觸發器則是隨機的,由此產生了隨機等效時間采樣的說法。如圖2 所示.。

對于按照等效采樣得到的信號是否包含有原信號的全部頻率成分,下面給出分析。

將連續信號x(t)和沖激函數p(t)相乘即可得到采樣后的離散信號x(n Ta)。

x(n Ta)=x(t)xp(t) (1)

由于輸入信號是周期信號,所以對于任一采樣點x(t-kT-mTl-jTa)

因為T1/Ta, 為整數,有

F[x(t-kT-mTl- jTs)]=F[x(t-qTs )]eiPTax(2)

所以采樣點x(t-kT-m Tl –jTa )所包含的信息和x(t-q Ta)所包含的信息量相同,因此我們用采樣點x(t-kT-mTI-j Ta)來代替x(t-q Ta)重建輸人信號的波形。

采樣數據經過重組算法重組后p(t)變為

由此可以看出,此結論和我們熟悉的采樣定理具有相類似的結果。只要等效采樣的微小的時間增量△t 足夠的小即滿足1/△t≥2fmax就可以恢復出原信號。

不管采用哪一種方式,最后對采集的數據通過特定的算法進行重組,都實現原始輸入信號波形的重建。重組后的數據的采樣事都是每一輪采樣之間采樣信號之間的延遲的微小增量△t來確定的。通過控制這個△t的大小,就可以控制等效采樣的頻率,也就是實際采樣的頻率。如果這個△t足夠的小,也就是等效采樣的頻率足夠高,對各種高頻成分都可以采集到。這樣就實現了低頻采集高頻。

3 基于EDA 技術的等效采樣方案

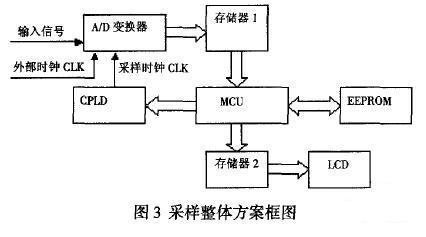

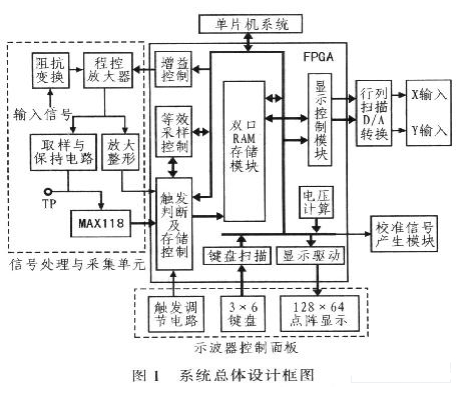

本方案是關于連續等效時間采樣的研究結果。等效時間采樣是針對輸入信號是周期信號的采樣方法,并且對復雜的周期信號失效。本方案由于采用了基于EDA 技術的采樣信號發生電路,可以解決復雜周期信號等效采樣失效的問題,進一步降低了對輸入信號的要求。本方案的另一大特色是,改變了連續等效采樣一個采樣信號只能做一次采樣的方式,在整個工作過程中,A/D 變換器在采樣信號的控制下,一直處于工作狀態。采樣效率可以達到隨機等效采樣的水平,又可以避免隨機等效采樣的不可控制時隙的問題。整體方案框圖如圖3 。

其中, A/D 變換器有兩個工作時鐘,對應于兩種工作狀態。一個時鐘是由外部震蕩器產生,一個由CPLD 產生;存儲器1為雙端口存儲器,用來暫存采集的數據;存儲器2 存放重組后的數據;CPLD 用來產生采樣信號;MCU 負責整個系統的控制,并完成數據重組。

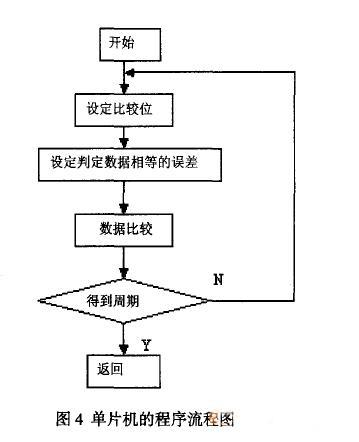

本方案的工作過程分兩步,首先A/D 對輸入信號采樣,采集后的數據存放到RAMI 中,然后單片機對采集后的數據處理計算出輸入信號的周期或者周期的整數倍。傳統的等效采樣信號的產生多采用電平觸發的方式,在輸入信號相同電平的位置就產生一次觸發。傳統方式僅僅由一個位置的電平相同就確定為下一周期的開始,用這種方式來判斷周期是很不嚴格的,如果對于復雜的周期信號,如果在一個周期中有兩個或者更多個相同的電平,這種方法明顯是失效的。本方案由于A/D 變換器對輸入信號的一個周期內采集了連續的足夠多的數據,通過判斷這些數據的周期來得到輸入信號的周期。這種方法相當于對不同周期的多個位置進行電平的比較,可以解決復雜周期信號的等效采樣失效問題。CPLD 根據獲得的周期數據產生采樣信號。

第二種工作狀態下為等效采樣模式, A/D 變換器根據CPLD產生的采樣信號對輸入信號進行采樣。采集后的數據存放到RAM1 中,然后由MCU 對采集后的數據按照本文提出的數據重組算法進行重組,重組后的數據存放到RAM2中,可以供顯示設備使用或者進行進一步的處理。整個過程的控制由單片機完成,本方案采用的MCU 為89C51 。

4 信號周期的獲得

傳統的觸發方式多采用電平觸發,這種方法對復雜的周期信號失效。本方案采用數字化方法來直接獲得輸入信號的周期。當有信號輸入時, A/D 芯片首先工作在連續采樣模式下,直到存儲器滿。因為輸入信號為周期信號,設周期為T ,又設A/D轉換器的時鐘周期為T1,則最多經過T*T1時間后采樣數據開始重復。單片機可以對采集的數據通過比較算法很容易的得出輸入信號的周期或者周期的整數倍。這個數據就是采樣信號產生的基礎。CPLD 根據得到的信號的周期來產生采樣信號。

5 采樣信號的產生

采樣信號必須滿足以下幾個要求:(1)可以重復產生。(2)每個采樣信號根據等效采樣的周期產生一個步進。本方案的采樣信號,改變了傳統的采樣信號每個周期只能產生一個采樣信號,每個采樣信號產生一個采樣數據的方式,在輸入信號的每個周期內一直按照A/D 變換器的工作頻率進行采樣。達到和隨機等效采樣基本相同的速度。并旦避免了測量與采樣觸發點相關的垂直和水平位置。特別是對頻率低于A/D 變換器時鐘的輸入信號有明顯的優勢。

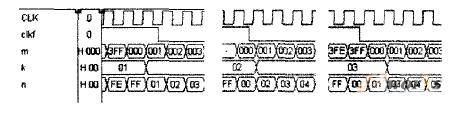

下面是用VHDL 語言編寫的采集信號的發生程序及其仿真波形。

UBRARY IEEE; USE IEEE.STD_WGIC_1164.ALL;

ENTITY clk_d IS

PORT(CLK:INSTD)_LOGIC; clkf: OUTSTD_LOGIC);

END clk_d;

ARCHITECTURE behav OF clk_d IS

SIGNAL m:STD_LOGIC_VECTOR(9 DOWNTO 0);

SIGNAL n,k:STD_LOGIC_VECTOR (7 DOWNTO O);SIGNALn7,fc:STD_LOGIC:='O';

BEGIN

PROCESS(clk)

BEGIN

IF clk'EVENT AND CLK='1' THEN

IF m =0000000000 THEN k=k+l;n=k; m

END IF; END IF;

END PROCESS;

PROCESS(n7)

BEGIN

IF n7'EVENT and n7='O' then fc=not fc; END IF;

END PROCESS;

n7=n(7);clkf=fc;

END behav;仿真波形如下圖所示:

由以上仿真波形可以看到采樣信號以輸入信號的周期為間隔移動了一個時鐘(CLK)周期這樣經過若干輪采樣以后,將以采集的數據剛好以時鐘(CLK)頻率完成對輸入信號的采樣。根據Nyquist 采樣定理,將可以采到輸入信號中頻率為clk/2 的成分,這樣就可以實現用低頻采集高頻信號。

6 結束語

通過對連續等效采樣的研究。進一步降低了等效采樣對輸入周期信號的要求,解決了復雜周期信號采樣失效問題。同時由于EDA 技術的使用,還可以方便的產生采樣信號,使A/D 變換器一直工作于采樣模式下,改變了傳統的采樣模式下一個采樣信號只能采集一個數據的問題,提高了系統的工作速度,可以達到和隨機等效采樣相同的性能,并且又避開了隨機等效采樣中測量與采樣觸發點相關的垂直和水平位置的問題,大大降低了硬件電路的復雜性。

本文創新點是用EDA 技術,方便地產生了采樣信號,大大簡化采樣觸發電路,解決了傳統等效采樣對復雜周期信號失效的問題,進一步降低對輸入信號的要求,并提高了系統的工作速度,而且降低了硬件電路的復雜性。

-

分辨率

+關注

關注

2文章

1068瀏覽量

41965 -

eda

+關注

關注

71文章

2769瀏覽量

173440 -

模數轉換器

+關注

關注

26文章

3209瀏覽量

126888

發布評論請先 登錄

相關推薦

EDA技術有什么特征?

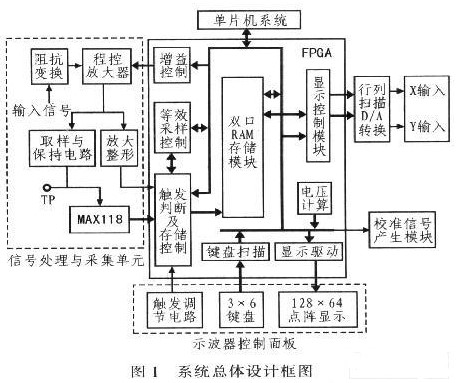

等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計

基于單片機的等效采樣示波器設計

基于FPGA的等效采樣存儲示波器設計

基于FPGA采樣技術的等效時間采樣原理剖析

等效時間采樣技術的原理作用及采用FPGA器件實現系統的設計

采用實時采樣和等效采樣相結合實現數字示波器的設計

基于FPGA的等效時間采樣原理的實現

采用EDA技術的等效采樣方案介紹

采用EDA技術的等效采樣方案介紹

評論