點(diǎn)擊上方藍(lán)字關(guān)注我們

在電阻抗多頻及參數(shù)成像技術(shù)中正交序列數(shù)字解調(diào)法的抗噪性能對信號每周期的采樣點(diǎn)數(shù)決定,采樣點(diǎn)數(shù)越多,抗噪性能越高。當(dāng)采樣信號頻率很高時(shí),為了在被采樣信號的一周期內(nèi)多采樣,就需要提高采樣時(shí)鐘的頻率,但是由于系統(tǒng)的ADC 器件時(shí)鐘速率并不能達(dá)到要求的高頻速率或者存儲處理速度等不能滿足要求因此我們可以采用低速ADC 器件通過等效時(shí)間采樣來對寬帶模擬信號進(jìn)行數(shù)據(jù)采集從而使系統(tǒng)易于實(shí)現(xiàn)。

1 等效時(shí)間采樣原理

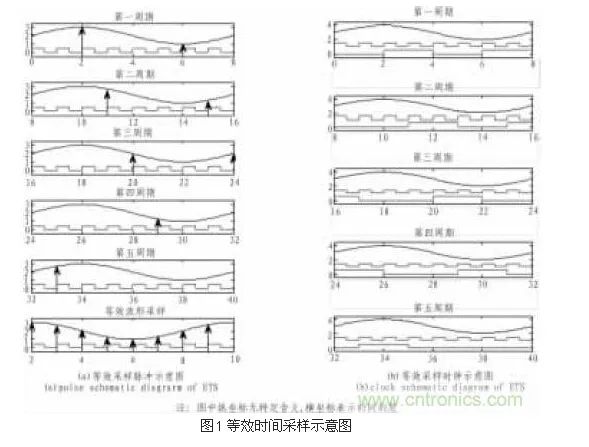

等效時(shí)間采樣技術(shù)是把周期性或準(zhǔn)周期性的高頻、快速信號變換為低頻的慢速信號。在電路上只對取樣前的電路具有高頻的要求,大大降低采樣變換后的信號處理、顯示電路對速度的要求,簡化了整個系統(tǒng)的設(shè)計(jì)難度。等效時(shí)間采樣分為順序采樣(sequential equivalent sampling)、隨機(jī)采樣(random equivalent sampling) 以及結(jié)合這兩種方式的混合等效采樣(compound equivalent sampling)。在下面我將介紹等效時(shí)間采樣中的混合時(shí)間采樣,對于周期性信號的等效時(shí)間采樣如圖1(a)所示。

在周期中的橫軸(時(shí)間)的第2 與第6 處的時(shí)鐘上升沿對模擬信號進(jìn)行采樣,圖中的箭頭表示采樣時(shí)刻。在一個周期中可以采集兩個點(diǎn),緊接著在第二個周期橫軸的第11與第15 處的時(shí)鐘上升沿對模擬信號進(jìn)行采樣。為了方便觀察在此將至第五周期的波形縱向排列。可以看到第二周期比周的采樣點(diǎn)距離各自周期起始點(diǎn)的時(shí)間晚了一個時(shí)鐘周期。第三周期比第二周的采樣點(diǎn)距離第三周期起始點(diǎn)的時(shí)間晚了一個時(shí)鐘周期。在第四周期進(jìn)行采樣時(shí)我們可以發(fā)現(xiàn)第二個采樣點(diǎn)已經(jīng)進(jìn)入第五周期。如果我們在第五周期周試圖繼續(xù)用以上方式進(jìn)行采樣即第五周期比第四周的采樣點(diǎn)距離起始點(diǎn)的時(shí)間晚一個時(shí)鐘周期,那么我們會發(fā)現(xiàn)在第五周期的采樣起始點(diǎn)采樣到的值重復(fù)了周期采樣到的數(shù)值。所以此時(shí)我們可以終止采樣那么我們就得到了如圖1 中的第6 個波形示意圖所表示的在一個周期的正弦波形中采到的8 個數(shù)據(jù)點(diǎn)。

我們通過將高頻時(shí)鐘進(jìn)行分頻已達(dá)到或者接近滿足處理速度時(shí)鐘要求。在圖1(b)中幅度的時(shí)鐘信號為采樣時(shí)鐘。由圖1(b)可以很清楚的看到分頻后的時(shí)鐘波形,分頻后的時(shí)鐘波形在時(shí)鐘的上升沿對信號進(jìn)行采樣,那么就會得到如圖1(a)中所表示的等效時(shí)間采樣。

2 基于FPGA的等效時(shí)間采樣實(shí)現(xiàn)

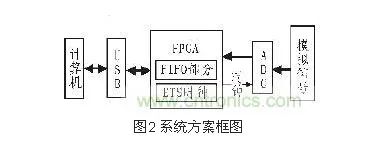

2.1 系統(tǒng)硬件實(shí)現(xiàn)框圖

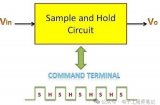

系統(tǒng)的總體框圖如圖2,F(xiàn)PGA 控制的等效采樣時(shí)鐘連接到ADC 器件的時(shí)鐘部分,ADC 器件在時(shí)鐘的控制下對寬帶模擬信號進(jìn)行采樣,采集到的數(shù)據(jù)傳送到FPGA 中的FIFO,F(xiàn)PGA 再將FPGA 中FIFO 的數(shù)據(jù)傳遞到USB 中的FIFO,然后USB 將USB 中FIFO 數(shù)據(jù)推送到計(jì)算機(jī),計(jì)算機(jī)對接收到的數(shù)據(jù)進(jìn)行重構(gòu)處理。對于信號周期的獲取,在電阻抗多頻及參數(shù)成像技術(shù)中采集信號的周期是由發(fā)送信號的周期決定, 而對于其他復(fù)雜周期信號的周期獲得可以通過所采用的方法獲得。

2.2 等效時(shí)間采樣時(shí)鐘的程序?qū)崿F(xiàn)

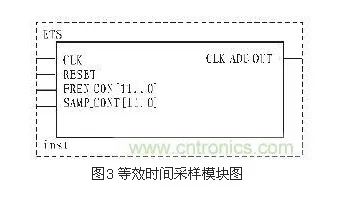

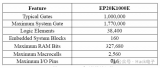

圖3 展示了基于FPGA 生成的等效時(shí)間采樣模塊的輸入端口與輸出端口。其中CLK 表示高頻時(shí)鐘的輸入,RESET表示的是復(fù)位輸入端,F(xiàn)REN_CON表示的是分頻控制輸入用于控制高頻時(shí)鐘的分頻數(shù),SANM_CONT 表示的是模擬信號的周期包含多少個高頻時(shí)鐘信號的波形,CLK_ADC_OUT 表示的是輸出時(shí)鐘端口,此端口連接到模數(shù)轉(zhuǎn)換器件(ADC)的時(shí)鐘輸入端口。

3 波形仿真

波形仿真是以模擬信號的一周期等于8 個CLK 時(shí)鐘周期,CLK_ADC_OUT 是對CLK 進(jìn)行4 分頻且分頻后的時(shí)鐘占空比為50%為假設(shè)的。1 號箭頭指向的時(shí)鐘上升沿標(biāo)志著周期結(jié)束,上升沿之后進(jìn)入第二周期。同理,2號箭頭所指時(shí)鐘的上升沿標(biāo)志著第二周期的結(jié)束,上升沿之后標(biāo)志著進(jìn)入第三周期。

在個周期中從CLK 的個上升沿開始計(jì)時(shí)同時(shí)對CLK 進(jìn)行分頻可以得到CLK_ADC_OUT 時(shí)鐘信號, 在周期中在CLK 的第二個上升沿CLK_ADC_OUT 電平翻轉(zhuǎn)(存在延時(shí)), 在第二周期中在第三個上升沿CLK_ADC_OUT電平翻轉(zhuǎn), 在第三個周期中在CLK 的第四個上升沿CLK_ADC_OUT 電平翻轉(zhuǎn)。可以看出波形仿真圖是對圖1(a)、(b)兩圖表達(dá)時(shí)鐘的實(shí)現(xiàn)。在這里應(yīng)該注意到,在周期中雖然也有8 個CLK 的上升沿,但是并沒有表示出如1 號箭頭所指CLK 時(shí)鐘上升沿之后與第二周期個CLK 時(shí)鐘上升沿之間的波形。

本文介紹了等效時(shí)間采樣的基本原理、系統(tǒng)實(shí)現(xiàn)的具體方案。等效時(shí)間采樣技術(shù)實(shí)現(xiàn)了利用低速的ADC 器件對寬帶模擬信號的采集, 降低了系統(tǒng)對ADC 器件的要求以及系統(tǒng)實(shí)現(xiàn)的復(fù)雜度。本文介紹的等效時(shí)間采樣技術(shù)由于使用了FPGA 采樣技術(shù), 使得在被采樣信號的一個周期中相較于一個周期僅能采集一個點(diǎn)的順序等效時(shí)間采樣有很大的提高,并且可以控制被采集信號一個周期中的采集點(diǎn)數(shù)從而可以根據(jù)后續(xù)器件處理速度實(shí)現(xiàn)變頻控制采樣。通過FPGA 實(shí)現(xiàn)等效采樣時(shí)間,降低了系統(tǒng)實(shí)現(xiàn)的復(fù)雜度,同時(shí)可以十分方便的對代碼進(jìn)行修改使系統(tǒng)的調(diào)試更加簡便。

?

?

?

?

掃碼加微信邀請您加入FPGA學(xué)習(xí)交流群

歡迎加入至芯科技FPGA微信學(xué)習(xí)交流群,這里有一群優(yōu)秀的FPGA工程師、學(xué)生、老師、這里FPGA技術(shù)交流學(xué)習(xí)氛圍濃厚、相互分享、相互幫助、叫上小伙伴一起加入吧!

點(diǎn)個在看你最好看

原文標(biāo)題:基于FPGA的等效時(shí)間采樣原理的實(shí)現(xiàn)

文章出處:【微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21759瀏覽量

604322

原文標(biāo)題:基于FPGA的等效時(shí)間采樣原理的實(shí)現(xiàn)

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

采樣示波器的原理和應(yīng)用

ADC08DL502采樣率最高到500M,這么高的采樣率的時(shí)鐘是否可以直接從FPGA輸出給ADC?

ADS6149采樣率250Mhz,后級接Xilinx FPGA,輸入1Mhz正弦波,在FPGA接口采樣得到異常采樣點(diǎn),為什么?

ADC采樣保持過程的具體時(shí)間要如何確定?

FPGA驅(qū)動AD芯片之實(shí)現(xiàn)與芯片通信

AMC1306的采樣率可以達(dá)到多少?模擬信號轉(zhuǎn)換為數(shù)字信號轉(zhuǎn)換時(shí)間是多少?

ADS1675IPAG采樣等待時(shí)間可以減小嗎?

FPGA門數(shù)的計(jì)算方法

采樣頻率和信號頻率之間的關(guān)系

信號采樣的算法原理是什么

信號采樣的基本過程包括哪些環(huán)節(jié)

微變等效電路和小信號等效電路的區(qū)別

運(yùn)算放大器采樣保持電路的工作原理

基于FPGA的等效時(shí)間采樣原理的實(shí)現(xiàn)

基于FPGA的等效時(shí)間采樣原理的實(shí)現(xiàn)

評論