引言

隨著電子技術的發展,對遙測信號的幀結構的可編程度、集成度的要求越來越高,用于時間統一系統的B碼源的設計也趨于高度集成化。為了適應現代靶場試驗任務的要求,我們采用Altera的CPLD器件,將用于產生B碼的各種門電路集成在一個芯片,通過高度集成的系統可以用于產生標準的串行時間碼向測量設備發送,測量設備對接收到的B碼進行解調能產生出系統所需的絕對時間和各種控制信號。此B碼產生系統可作為基地設備檢測調試用,也可作實踐教學設備。

1 IRIG-B碼介紹

在靶場試驗中隨著設備所需信息量的增加,對標準化時統設備要求也就越來越高,其中關鍵的問題之一就是選用什么樣的時間碼。IRIG-B(美國靶場儀器組-B型格式)DC時間碼以其實際優越性能,成為時統設備首選的標準碼型。

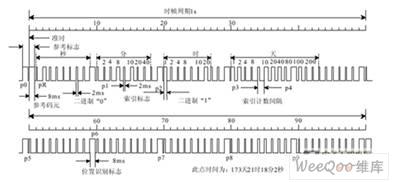

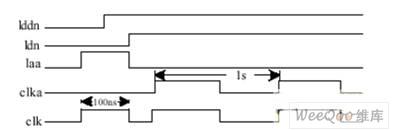

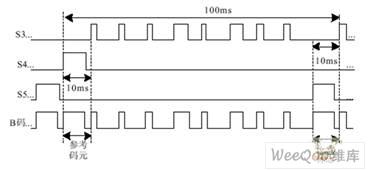

IRIG(Inter-Range Instrumentation Group)是美國靶場司令部委員會的下屬機構,稱為"靶場時間組"。IRIG時間標準有兩大類:一類是并行時間碼格式,這類碼由于是并行格式,傳輸距離較近,且是二進制,因此遠不如串行格式廣泛;另一類是串行時間碼,共有六種格式,即A、B、D、E、G、H。它們的主要差別是時間碼的幀速率不同。B碼的主要特點是時幀速率為1幀/s;攜帶信息量大,經譯碼后可獲得1、10、100、1000c/s的脈沖信號和BCD編碼的時間信息及控制功能信息;高分辨率;調制后的B碼帶寬,適用于遠距離傳輸;分直流、交流兩種;具有接口標準化,國際通用。IRIG-B(DC)時間碼格式如圖1所示。其幀速率為1幀/s,可將1幀(1s)分為10個字,每字為10位,每位的周期均為10ms。每位都以高電平開始,其持續時間分為3種類型:2 ms(如二進制"0"碼和索引標志) 、5ms(如二進制"1"碼)和8ms(如參考碼元,即每秒開始的第一字的第一位;位置標志P0~P9,即每個字的第十位)。第一個字傳送的s是信息,第二個字是min信息,第三個字是h信息,第四、五個字是d(從1月1日開始計算的年積日)。另外,在第八個字和第十個字中分別有3位表示上站和分站的特標控制碼元(參考圖1)。

圖1 IRIG-B(DC)時間碼格式

2 硬件電路設計

B碼信號是否正確,是否被正確地解調出來,關鍵在于能否按照B碼的變化規律產生預置信號。本課題的難點在于按照其本身的變化規律安排好產生B碼的各種時序。

用9個十進制計數器級聯組成時鐘電路,用來產生時間信號--天、時、分、秒信號。四種信號經過緩存后順序送入并串轉換電路,將并行碼串行輸出,由7個產生時序脈沖的4017級聯產生B碼所需的三種脈沖形式,經過邏輯門的控制將串行輸出的時間碼轉化成B碼。將所有計數器、緩存器、并串轉換電路、時序脈沖產生器、各種邏輯門等集成到可編程器件(CPLD)中,即用將一個完整的系統集成到一個芯片中。外圍電路只需一個時鐘電路和上電置數電路即可。由于采用了可編程器件,用軟件編程可以把一個硬件系統集成到一個芯片中,大大簡化了硬件電路,并且可以對芯片內部的電路進行仿真和多次編程,調試起來很方便。

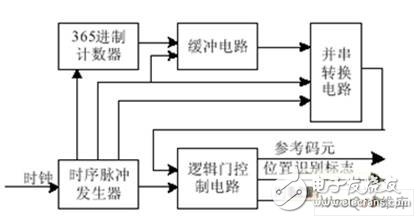

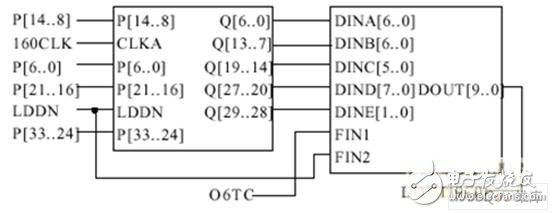

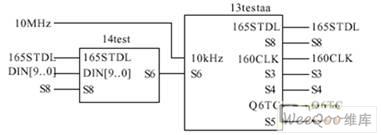

根據確定的方案,設計的硬件電路如圖2所示。可編程器件EPM7128SLC84-15內部電路如圖3所示。

圖2 系統總體框圖

圖3 可編程芯片內部電路框圖

硬件電路由可編程芯片、主時鐘、置數電路三部分組成。芯片內部電路由365進制計數器、緩沖電路、并串轉換電路、時序脈沖發生器及邏輯門控制電路組成。

圖2中,置數電路將預置好的時間置入,使得芯片內部的365進制計數器從此時刻開始計數。主時鐘是頻率為10MHz的晶振,作為芯片內部時序脈沖發生器的時鐘信號。可編程芯片內部電路設計是本課題設計的核心。圖3中,時序脈沖發生器由七級4017級聯而成,由外輸入時鐘作為第一級的時鐘。第七級產生的秒信號作為365進制計數器的時鐘,該計數器組由九個十進制同步計數器74LS162組成,輸出7位二進制形式的秒信號,7位分信號,6位時信號,10位天信號(分為低八位和高二位天信號兩組)。輸出的時間信號送至緩沖器,由時序脈沖發生器的第六級輸出周期為100ms的時鐘信號作為緩沖器的內部時鐘,將緩沖過的時間信號以B碼的格式順序送入并串轉換電路。并串轉換電路的置位信號由時序脈沖發生器第六級的Q8提供,每100ms將輸入的時間信號鎖存一次,時序脈沖發生器的第五級輸出的周期為10ms的時鐘作為并串轉換的時鐘,將并行數據串行輸出。時序脈沖發生器通過邏輯門的控制產生了B碼的三種脈沖形式:第一種是高電平為2 ms ,低電平為8ms的脈沖(代表邏輯"0");第二種是高、低電平均為5 ms的脈沖(代表邏輯"1");第三種是高電平為8 ms ,低電平為2ms的脈沖(作為位置識別標志和參考碼元)。并串轉換輸出的串行碼經過邏輯門的控制,碼?1"轉化為B碼脈沖的第一種形式,碼元"0"轉化為B碼脈沖的第二種形式,即將二進制的時間信號轉變成為B碼形式。參考碼元、時間碼元、位置識別標志綜合在一起作為真正的B碼輸出。 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w

3 主要單元電路設計

3.1 置數電路

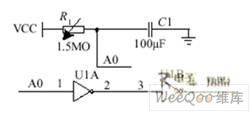

根據課題要求,電路應具有置數功能。置數電路如圖 4 所示,改進后的置數電路如圖 5所示。

圖4 置數電路

圖5 改進的置數電路

將預置的天、時、分、秒在上電的同時置入各個計數器中。由于計數器74LS162是同步計數器,要求置數脈沖有效時(低電平有效)至少有一個時鐘的上升沿。

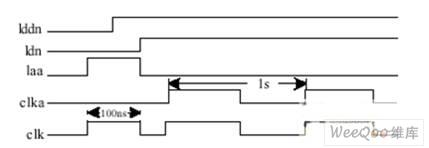

計數器的時鐘是由時序脈沖發生器提供的秒信號,為了保證在置數脈沖有效時存在一個時鐘上升沿,對秒信號作如下改進:

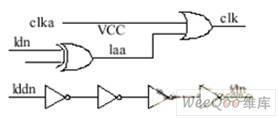

輸入信號clka 由時序脈沖發生器產生,輸出信號clk 作為365進制計數器的時鐘。輸入輸出波形關系如圖 6所示。

圖6 置數電路波形圖

3.2 可編程芯片EPM7128SLC84-15內部電路

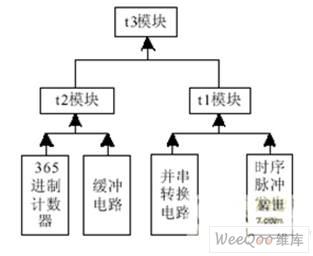

本部分采用層次結構的設計,由底層到頂層將復雜的電路模塊化,最后生成一個頂層模塊。圖7 表示內部電路的層次結構。

圖7 層次結構圖

最底層的四個模塊分別包含四部分較復雜的電路,將四個模塊分為兩組,又生成較高層的模塊t1和t2,模塊t1和t2最終生成最頂層的模塊。采取模塊化設計的優點在于可以由底層到頂層對每一個模塊分別進行仿真,有利于各個模塊間時序的配合。

(1)t2模塊

365進制計數器

該部分電路由九個十進制同步計數器 74LS162級聯而成,稱為計數鏈,生成的模塊形式如圖 8所示。

圖8 計數器模塊 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w

緩沖電路

它的功能是將計數器輸出的5組時間信號以B碼的格式交替輸出。緩沖電路生成的模塊如圖 9所示。

圖9 緩沖電路模塊圖

為簡單起見,用VHDL語言描述如下:

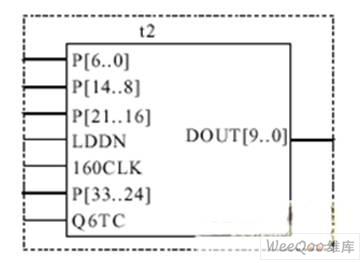

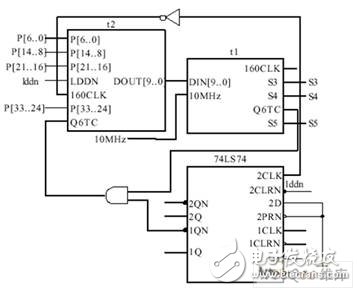

t2模塊是由計數器和緩沖電路合成的較高層的模塊。這個模塊的功能是置數后計數器從此時刻開始按秒計數,將時間信號以B碼的格式并行輸出。兩個模塊的連接情況如圖10所示,t2模塊如圖 11 所示。

圖10 t2模塊內部電路

圖11 t2模塊

(2)t1模塊

并串轉換電路

由于B碼是串行碼,須將t1模塊輸出的并行數據進行并串轉換。并串轉換電路生成的模塊如圖 12 所示。

圖12 并串轉換電路模塊 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w

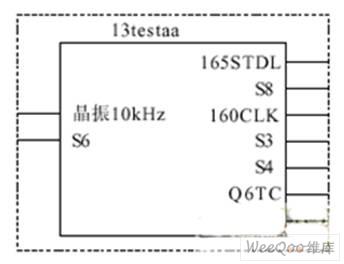

時序脈沖發生器

該部分電路主要由七個脈沖分配器相級聯和一些邏輯門控制組成。完成的主要功能有:產生B碼的3種脈沖形式;提供計數器的時鐘--"S"信號;提供緩沖電路中計數器的時鐘--周期100ms;提供并串轉換電路的置位信號。時序脈沖發生器生成的模塊如圖 13所示。

圖13 時序脈沖發生器模塊

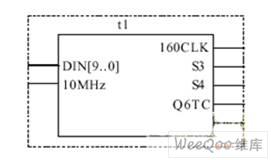

t1模塊是并串轉換電路和時序脈沖發生器合成的較高層的模塊。這個模塊的功能是將t2模塊輸出的并行時間碼串行輸出,由時序脈沖發生器輸出各種控制信號對串行碼控制輸出B碼的三類脈沖,同時輸出t2模塊所需的各類時鐘信號。并串轉換電路模塊和時序脈沖發生器模塊的連接情況見圖14,t1模塊見圖 15。

圖14 t1模塊內部電路

圖15 t1模塊

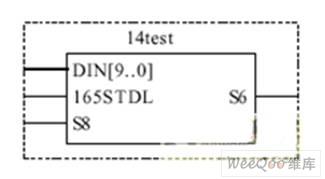

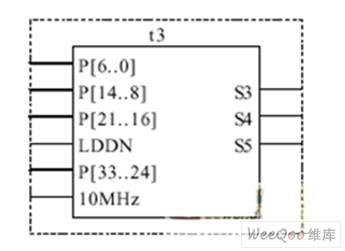

(3)t3模塊

t3模塊是由t1、t2兩個模塊構成的最頂層的模塊,其內部連接如圖16所示。

圖16 t3模塊內部電路圖

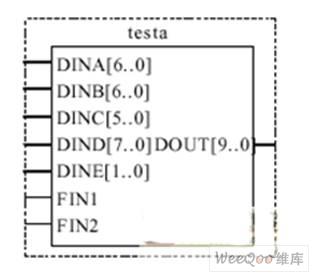

由圖16可見,t3模塊(圖17)將所有內部電路集成,整個電路只有32個輸入端,3個輸出端。將t3模塊直接燒入可編程芯片即可。

圖17 t3模塊 function ImgZoom(Id)//重新設置圖片大小 防止撐破表格 { var w = $(Id).width; var m = 650; if(w

3.3 碼合成電路

可編程芯片輸出了組成B碼的3個分信號,經過1個或門后將3個信號合成了B碼信號,如圖18所示。

圖18 合成B碼波形圖

結語

本設計的難點在于如何正確地安排好芯片內部各個模塊之間的時序。該B碼源通過解調之后能夠顯示正確的時間,達到了很好的效果。該B碼源最大的特點是電路非常簡單,可靠性較高。通過可編程芯片高度集成了一個系統,克服了以往B碼源電路復雜的缺點。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605226 -

Altera

+關注

關注

37文章

787瀏覽量

154073 -

計數器

+關注

關注

32文章

2261瀏覽量

94876

發布評論請先 登錄

相關推薦

ALTERA FPGA/CPLD高配學習指南:入門和高級篇,教程十講全集

Altera FPGA/CPLD設計(高級篇)

理解Altera器件IO輸出的時間參數

altera fpga/cpld設計

FPGA在IRIG-B碼源設計中的應用

CPLD器件在時間統一系統中的應用

ALTERA CPLD器件的配置與下載

基于CPLD的IRIG-B碼對時方式在繼電保護裝置中的應用

基于IRIG-B碼對測控設備時間系統的設計

FPGA教程之ALTERA的CPLD與FPGA器件的詳細資料說明

Altera FPGA CPLD學習筆記

采用Altera的CPLD器件實現時間統一系統的B碼源設計

采用Altera的CPLD器件實現時間統一系統的B碼源設計

評論