引 言

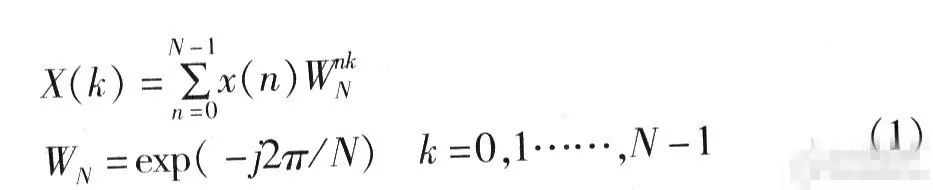

數字信號處理主要研究采用數字序列或符號序列表示信號,并用數字計算方法對這些序列進行處理,以便把信號變換成符合某種需要的形式。在現代數字信號處理中,最常用的變換方法就是離散傅里葉變換(DFT),然而,它的計算量較大。運算時間長,在某種程度上限制了它的使用范圍。快速傅里葉變換(FFT)的提出使DFT的實現變得接近實時,DFT的應用領域也得以迅速拓展。它在圖像處理、語音分析、雷達、聲納、地震、通信系統、遙感遙測、地質勘探、航空航天、生物醫學等眾多領域都獲得極其廣泛的應用。隨著FPGA技術的高速發展以及EDA技術的成熟,采用FPGA芯片實現FFT已經顯示出巨大的潛力。

目前用FPGA實現的FFT處理器結構大致分為四種:遞歸結構、級聯結構、并行結構和陣列結構。遞歸結構只利用一個碟形運算單元對數據進行規律的循環計算,使用硬件資源較少,但運算時間較長。級聯結構每一級均采用一個獨立的碟形運算單元來處理,相對遞歸結構速度上有所提高,不足之處是增加了延時用的緩沖存儲器使用量。并行結構對一級中的蝶形單元并行實現,陣列結構是將每一級的蝶形運算單元全部并行實現,這兩種結構有很高的運算速度,但消耗的資源過大,一般不采用。為了提高運算速度,特別是為了適應多批數據處理,一般采用級聯結構實現FFT處理器。

1 FFT整體結構設計

在FFT算法中,目前大多使用基-2和基-4算法實現級聯結構的FFT處理器,除此之外,也可采用基-8和基-16算法來實現。隨著基數的增大,對于相同點數的離散數列,處理器所分的級數越少,對緩沖存儲器的需求也越小,因此考慮采用基-16算法來實現FFT處理器,但基-16算法只能實現離散數列點數是16的p次冪的FFT。從而,引入混合基思想來改進基-16算法。

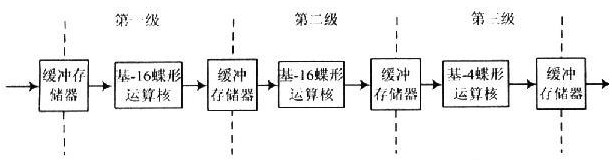

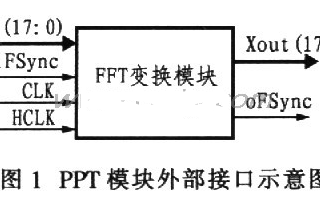

設r1=16P,r2=N/16P=2,4,8,式(2)先將原非16的p次冪的N點FFT分解為16P點的FFT;再分解為N/16P點的FFT。首先對輸入信號進行16P點的FFT運算,然后將結果乘以一個旋轉因子最后將計算出的數據進行一次N/16P點FFT運算,得到的結果即為所需要的N點FFT運算結果。這樣處理,既能減少分解的級數,又能使計算離散數列點數只需是2的整數次冪即可。以1 024點為例,只需分解成兩級基-16運算模塊和一級基-4運算模塊即可實現,其FFT處理器結構圖如圖1所示。在此結構圖的前端增加/減少基-16運算模塊或將最后一級基-4運算模塊改為基-2或基-8運算模塊,就可以實現其他離散數列的點數只需是2的整數次冪的FFT運算。

2 蝶形運算核的實現

2.1 基-16蝶形運算核

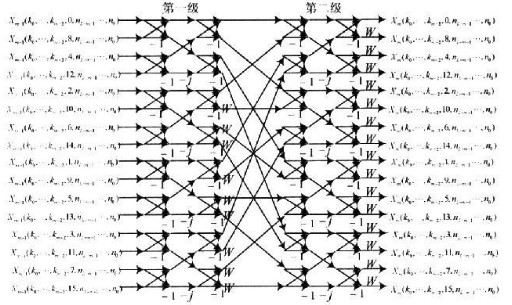

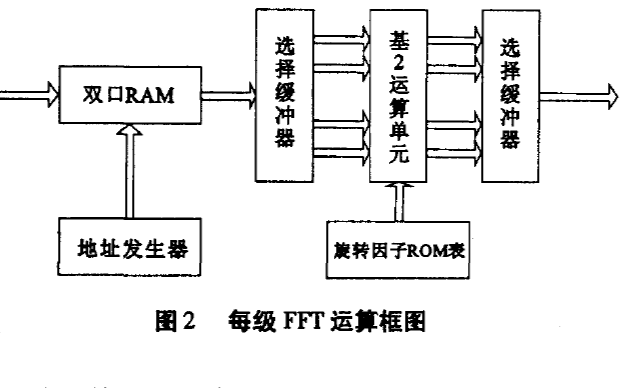

如果直接將基-16蝶形運算公式轉換到硬件中實現基-16運算核,其結構將十分復雜的。因此,采用易實現的頻域抽選基-4算法來實現頻域抽選基-16蝶形運算核。由基-4蝶行運算單元實現的基-16蝶行運算單元如圖2所示。

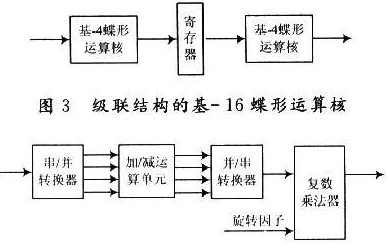

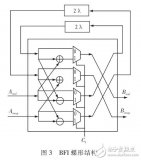

采用并行流水結構實現的基-16運算核,一個數據時鐘可處理16個數據。而每次蝶形運算在一個數據時鐘內只需要計算出一個結果,這將造成資源浪費。因此,采用級聯結構實現的基-16蝶形運算核,用兩個基-4蝶形運算核分別復用4次來實現每一級中的四個蝶行運算,中間用一個串行出入/輸出的寄存器進行連接,其結構框圖如圖3所示。

2.2 基-4蝶形運算核

基-4蝶形運算核的結構如圖4所示,其中加減模塊為兩級流水結構,一次可以計算4個數據。蝶形運算的四個串行輸入數據經串/并轉換器轉換為四路并行數據,進入加減運算單元。計算出的4個并行結果進入并/串轉換器后,串行輸入復數乘法器和旋轉因子相乘然后輸出結果。因為圖1中最后一級的數據只需要進行加減運算不需要再乘以旋轉因子,所以圖1中的基-4蝶形運算核是沒有復數乘法器的,數據從并/串轉換器中直接輸出給緩沖存儲器。

2.3 復數乘法器

雖然現在的高端產中已經集成了可以完成乘法的DSP資源,但也是有限的。因此高效復數乘法器的設計對該設計來講仍然非常的重要。復數乘法的標準式如下:

R+jI=(A+jB)×(C+jD)=(AC-BD)+j(AD+BC)

式中:A,B分別為輸人數據的實部和虛部,C和D分別為旋轉因子的實部和虛部。按照這種標準表達式,執行一次復數乘法需要進行4次實數乘法,2次實數加法和2次實數減法。將上述公式重新整理為:R=(C-D)·B+C(A-B),I=(C-D)A-C(A-B)優化后的復數乘法器需要進行3次實數乘法,2次實數加法和3次實數減法,相比傳統結構多了一個減法器,少了一個乘法器。在FPGA中,加減法模塊所占用的相對裸片面積要小于相同位數的乘法器模塊。這樣的優化還是很有價值的,在FFT吞吐量不變的情況下,可減少25%的乘法器使用量,在乘法器數量一定的情況下可高FFT吞吐量。

3 存儲器單元

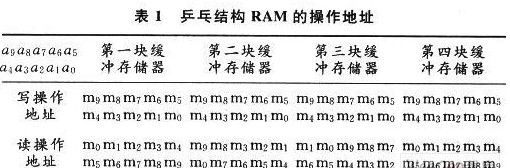

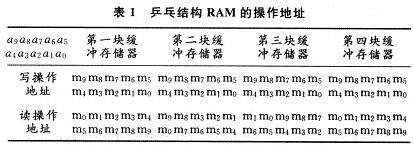

傳統的級聯結構的FFT處理器的緩沖存儲器都是采用乒乓結構,基本思想就是用兩塊相同的RAM交替讀出或寫入數據。即其中一塊RAM在寫入數據時,另一塊RAM用于讀出數據。當用于寫入數據的RAM寫滿時交換讀寫功能。將乒乓結構中RAM的內部存儲單元地址用二進制數a9a8a7a6a5a4a3a2a1a0表示。以寫滿其中以塊RAM為一個周期,用一個二進制計數器m9m8m7m6m5m4m3m2m1m0生成的順序寫入,混序讀取的乒乓結構RAM的操作地址如表1所示。

表1中第一,二,四塊存儲器的寫操作地址和讀操作地址是可以互換的,也就是將數據混序寫入,順序讀取。因此,根據這個規律采用一塊可同時讀寫的雙端口RAM來實現第一,二,四塊存儲器。其基本思想就是對同一個地址進行讀和寫。以用一塊雙端口RAM實現第一塊存儲器的為例,在第一個周期內雙端口RAM按照地址m9msm7m6m5mdm3m2m1m0進行寫操作,即數據是按照自然順序儲存的。在第二個周期按照地址m0m1m2m3m4m5m6m7msm9同時進行讀寫操作,讀出的數據按照倒位序排列,寫入的數據按照倒位序儲存的。 在第三個周期按照地址m9msm7m6m5m4m3m2m1m0同時進行讀寫操作,讀出的數據按照倒位序排列,寫入的數據是按照自然順序儲存的。依次類推下去,讀出的數據都是按照倒位序排列。同樣第二塊和第四塊存儲器的存儲地址也具有這樣類似的循環規律。因此只有第三塊存儲器需要用乒乓結構的RAM實現,與傳統所有存儲器都用乒乓結構RAM實現相比,節省了3/8的存儲單元。設計中用Matlab軟件直接生成旋轉因子,并將其轉化為16位有符號定點數寫入MIF文件。然后用ROM直接調用MIF文件,將旋轉因子預置在ROM中。

4 仿真結果

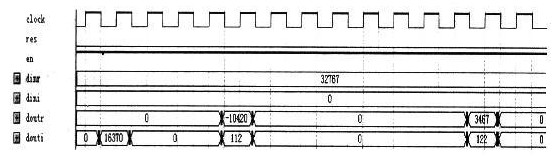

選用Altera公司生產的Cyclone Ⅱ的EP2C35F484C7芯片上進行驗證,在QuartyusⅡ7.2軟件中進行編譯和仿真。通過對高基核的優化處理,該設計對邏輯單元消耗量和傳統用基-4算法實現相近,僅為4 399,但由于本文采用了高基低基組合的混合基算法,在處理1 024點的離散數列時,處理器所分的級數僅為3級,相對傳統的低基數算法,其實現減少了對緩沖存儲器塊數的需求;并通過對緩沖存儲器的優化設計,又比全部用乒乓結構RAM實現的傳統方法節省了3/8的存儲單元,因此占用的存儲資源僅為154 048 b。仿真波形如圖5所示,該仿真結果和Matlab計算結果基本一致,存在一定的誤差是由于有限字長效應引起的。

5 結 語

在100 MHz的時鐘下工作,完成一次1 024點的FFT從輸入初始數據到運算結果完全輸出僅需要54.48μs,且連續運算時,處理一組1 024點FFT的時間僅為10.24 μs,達到了高速信號處理的要求。

-

處理器

+關注

關注

68文章

19404瀏覽量

230797 -

FPGA

+關注

關注

1630文章

21796瀏覽量

605228 -

數字信號處理

+關注

關注

15文章

563瀏覽量

45952

發布評論請先 登錄

相關推薦

一種基于FPGA的可配置FFT IP核實現設計

求一種基于FPGA的64點FFT處理器的設計方案

基于FPGA的FFT處理器的研究與設計

基于FPGA的級聯結構FFT處理器的優化設計

OFDM系統中IFFT與FFT處理器的實現

基于FPGA的FFT實現方案

使用FPGA實現流水線結構的FFT處理器論文講解

采用FPGA芯片實現FFT處理器的設計

采用FPGA芯片實現FFT處理器的設計

評論