合成孔徑雷達成像算法中較為成熟和應用廣泛的算法主要有距離-多普勒(R-D)算法和線性調頻變標(CS)算法。R-D算法復雜度相對較低,運算比較簡單,雖然其成像質量并不高,但是相比對穩定性、存儲空間、功耗與實時性要求都很高的實時SAR成像系統,其應用十分廣泛。在整個有距離-多普勒(R-D)算法中方位脈沖壓縮系統是設計的關鍵。隨著FPGA芯片突飛猛進的發展,實時雷達成像方位脈沖壓縮系統在FPGA上實現變成了可能。

1 脈沖壓縮及方位脈沖壓縮系統的結構

1.1 脈沖壓縮的基本原理

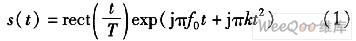

實現脈沖壓縮必須滿足兩個條件:一是發射脈沖必須具有非線性的相位譜并且其脈沖寬度與有效頻譜寬度的乘積》1;二是接收機中必須具有一個壓縮網絡,其相頻特性應與發射信號實現“共軛匹配”。線性調頻信號又稱為Chirp信號,是廣泛應用在信號處理領域的一種脈沖壓縮信號。線性調頻信號是具有矩形包絡的寬脈沖信號,其特點是具有二次型的非線性相位譜和線性頻率譜,即頻率具有線性特性。一維線性調頻信號的表達式為

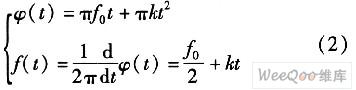

其中,t為時間變量,T為線性調頻脈沖寬度,f0為載頻頻率,k為調頻斜率。信號的相位函數和頻譜函數為

由式(2)可知,信號的調頻斜率與時間成線性關系。

由于線性調頻信號的以上特點,線性調頻信號適合實現脈沖壓縮,是一種典型的脈沖壓縮方法:首先線性調頻脈沖的相位譜是非線性的,具有較大的時間帶寬積;其次匹配濾波器是在輸入為確知信號加白噪聲的情況下,得到最大輸出信噪比的傳遞網絡,滿足壓縮網絡的條件。因此,采用匹配濾波器對信號進行濾波,得到輸出信號最大的信噪比。

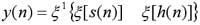

對線性調頻信號進行脈沖壓縮的基本原理可以總結為:對寬脈沖線性調頻信號進行匹配濾波處理,使其能量集中,成為窄脈沖信號,從而獲得線性調頻信號大時間帶寬積所對應的高分辨率。線形調頻信號脈沖壓縮具體實現是先把一維線性調頻信號從時域轉換到頻域,再求其對應匹配濾波器的傳遞函數。匹配濾波器脈沖響應是信號的時間鏡像復共軛,其時域表達式為

h(t)=C·s*(t-t0) (3)

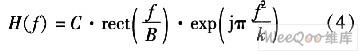

根據駐定相位原理,可以得到匹配濾波器的傳遞函數為

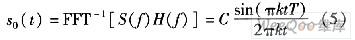

線性調頻信號經過匹配濾波器完成脈沖壓縮過程,輸出表達式為

1.2 方位脈沖壓縮系統的結構

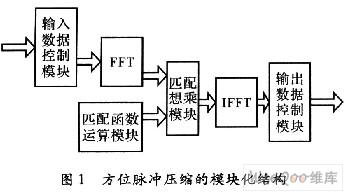

實現R-D算法中方位脈沖壓縮的思路是先將信號經過FFT變換到頻域,然后與匹配函數經過FFT后的結果進行匹配相乘,再經過IFFT得到壓縮好的脈沖。在FPGA上實現時,應該包括輸入\輸出數據控制模塊、FFT\IFFT模塊、匹配函數運算模塊、匹配相乘模塊。數據流及各個模塊的相互關系,如圖1所示。

距離脈沖壓縮的數據先進入輸入數據控制模塊,送入FFT運算模塊,同時匹配函數運算模塊進行工作,輸出計算好的匹配函數,與FFT的輸出結果同時送到匹配相乘模塊中,相乘后的結果送入IFFT模塊中,最后將IFFT的結果經輸出數據控制模塊進行輸出。

2 方位脈沖壓縮系統的FPGA設計

2.1 輸入/輸出控制模塊

輸入數據控制模塊的主要作用是將數據送入FFT模塊,同時給出FFT模塊所需的控制信號,例如數據有效信號。數據流入數據控制模塊時要做好緩存工作,保證其與FFT控制信號同步進入FFT模塊。為了節省FPGA的資源,可以把相同功能的模塊,如FFT/IFFT,進行復用。若FFT與IFFT模塊復用,則應在輸入模塊中加入狀態機來進行控制。狀態1為無任何原始數據輸入并且無IFFT運算的數據輸入的狀態;狀態2為僅有原始數據輸入而無IFFF運算的數據輸入的狀態;狀態3為無原始數據輸入但是有進行IFFT運算的數據輸入的狀態。狀態機僅需要原始數據有效的使能信號與匹配相乘后數據有效的使能信號來進行控制即可。狀態1代表了整個系統處于等待數據輸入初始化的工作狀態。狀態2代表了原始數據進行FFT運算的工作狀態。狀態3代表了匹配相乘后數據進行IFFT的工作狀態。

在FFT模塊與IFFT模塊復用的結構中,輸出控制模塊的作用是當匹配相乘的數據到來時,將其送入輸入數據控制模塊,再由輸入數據控制模塊送入FFT模塊去完成IFFT運算;當計算出IFFT的結果時,輸出數據控制模塊直接將結果輸出。實現上述功能,只需使用狀態機即可,其工作原理與輸入數據控制模塊中的狀態機類似

2.2 FFT/IFFT模塊

在FFF/IFFT模塊的設計上,為了提高設計的性能,增加設計的靈活性,采用Altera公司于2005年4月推出的版本號為2.1.3的FFT的IPcore進行FFT和IFFT運算。該IP core是一個高性能、高度參數化的,執行正向復數FFT與反向復數IFFT的FFT處理器。

2.3 匹配函數運算模塊

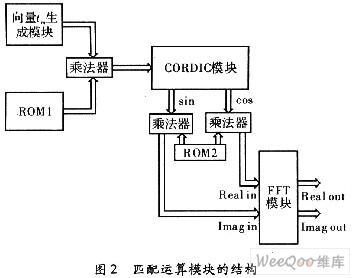

方位壓縮的匹配函數為匹配函數再經過FFT變換到頻域。在FPGA實現時要把模擬參量量化成離散的數字參量來進行處理。其中γm(RB),RB以雷達到場景中心線的距離Rs為參考進行數字量化,即每一個距離單元的RB=Rs+n deltaR,則RB相對每一個距離單元為常數。慢時間tm以脈沖重復時間1/PRF進行數字量化,相對于每一個方位單元為常數。在設計時,由于γm(RB)對于同一個距離單元來說為常數,所以可以把不同距離單元的γm(RB)按一定順序存入一個ROM中,在處理不同的距離單元時讀取相對應的γm(RB)。αr(tm)實現時用漢明窗。對于exp()采用CORDIC算法生成sin,cos來進行實現。若一個距離單元nan有個采樣點,則向量由于PRF為常數,所以僅需設計一個產生向量[-nan/2:nan/2-1]2的模塊,即每個時鐘周期送出向量[-nan/2:nan/2-1]2中的一個數。匹配函數運算模塊的框圖,如圖2所示。

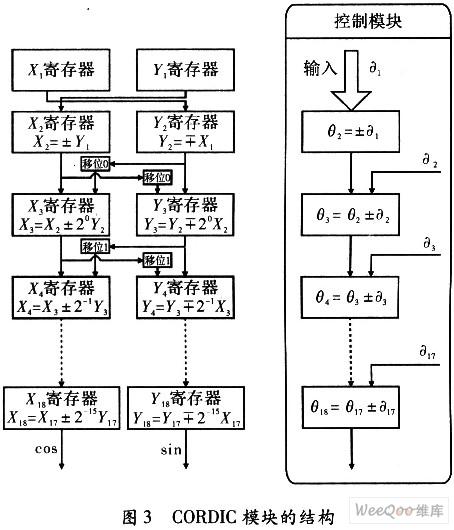

CORDIC模塊的實現是匹配函數運算模塊設計的重點。CORDIC(Coordinate Rotation Digital Com-puter算法即坐標旋轉數字計算方法。主要用于三角函數、雙曲線、指數、對數的計算。CORDIC模塊采用18級流水線結構來實現,如圖3所示。18級寄存器組中下一級寄存器中的輸入數據是上一級寄存器的輸出數據進行移位后相加或減組合得到的。進行加運算還是減運算完全由控制模塊控制。控制模塊的輸入就是整個CORDIC模塊的輸入,即要進行sin,cos計算的角度э1。控制模塊也采用流水線結構與18級寄存器組一一對應,達到對各級流水線的控制。18級流水線設計需要18個時鐘周期來獲取第一個計算結果,而只需要一個時鐘周期來獲取隨后的計算結果。流水線結構的特點非常適合應用于方位脈沖壓縮匹配函數運算的設計:首先,實時成像需要很高的數據吞吐量,這與流水線結構的優勢相符合;其次距離單元的數據是隨著時鐘依次進入運算模塊的,即一個時鐘周期讀人一個距離單元的數據,這與流水線結構的特點十分的吻合。采用流水線結構實現CORDIC算法,可以使匹配函數的數據在每個周期逐個輸出,僅做好同步工作,使匹配函數的數據與距離脈沖壓縮結果對應匹配相乘即可。

2.4 匹配相乘模塊

匹配相乘模塊主要完成的工作,是把距離脈沖壓縮的數據經FFT后的結果與匹配函數對應相乘,再把相乘的結果送出。匹配相乘模塊的核心是復數乘法器。復數乘法器是由4個普通乘法器和兩個加法器組成。假設完成(a+bi)×(c+di)的操作,先分別計算a×c,a×d,b×c,b×d這4個實數與實數的乘法運算,再把減法運算a×c-b×d結果作為復數乘法器輸出的實部,加法運算a×d+b×c的結果作為復數乘法器輸出的虛部。

對數據的同步也是設計的重點。因為距離脈沖壓縮經FFT后的數據與匹配函數的數據并不是同時進入匹配相乘模塊。距離脈沖壓縮經FFT后的數據較先進入,主要是因為匹配函數運算的CORDIC采用流水線結構,需要18個時鐘周期來獲取第一個計算結果而產生匹配函數數據的延遲。所以應該對匹配相乘模塊對距離脈沖壓縮經FFT后的數據進行緩沖。緩沖采用FIFO模塊來實現。FIFO可以采用自帶的IP core。

3 波形仿真與性能分析

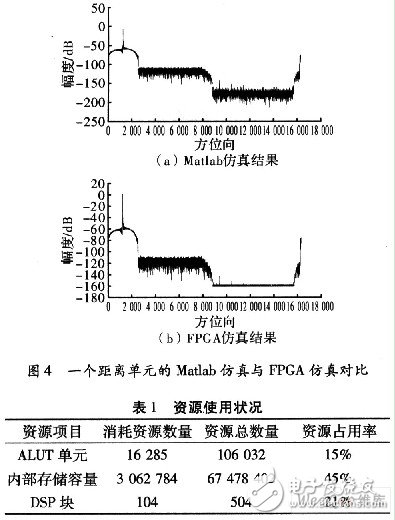

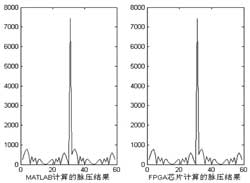

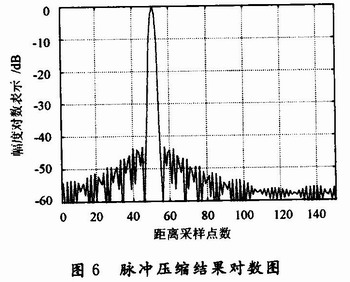

驗證方法采用比對的方法,即單個目標點的仿真數據分別進行理論方位脈沖壓縮仿真和基于FPGA的方位脈沖壓縮仿真,并將得到的仿真結果進行比對。仿真數據中一個距離單元的點數為16 384點。驗證過程是首先在。Matlab軟件環境下對單個點目標的一個距離單元進行方位脈沖壓縮的仿真,即理論仿真,然后再在Modelsim環境下對該距離單元進行方位脈沖壓縮的FPGA仿真,并將得到的結果與Matlab下得到的理論結果進行比較。其比較的波形,如圖4所示。

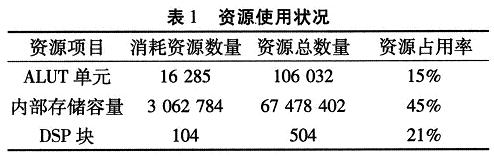

選用Ahera公司芯片EP2S130F780C5進行測試。穩定工作時時鐘頻率可以達到150 MHz。

4 結束語

方位脈沖壓縮系統是這個R-D算法在FPGA實現的關鍵。文中給出的方案通過實驗驗證能夠達到設計的要求。實驗表明,隨著可編程器件規模、速度的不斷提高,采用FPGA實現高速數字信號處理的算法具有可行性和優越性。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605244 -

芯片

+關注

關注

456文章

51155瀏覽量

426312 -

雷達

+關注

關注

50文章

2965瀏覽量

117862 -

壓縮系統

+關注

關注

0文章

9瀏覽量

7968

發布評論請先 登錄

相關推薦

基于FPGA的雷達脈沖壓縮系統設計

基于FPGA的數字脈沖壓縮系統實現

怎么設計基于XQ2V1000FPGA的數字脈沖壓縮系統?

基于FPGA的雷達脈沖壓縮系統該怎么設計?

基于FPGA的脈沖壓縮仿真與實現

基于FPGA的雷達數字脈沖壓縮技術

R-D算法與FPGA芯片實現雷達成像方位脈沖壓縮系統的設計與仿真分析

R-D算法與FPGA芯片實現雷達成像方位脈沖壓縮系統的設計與仿真分析

評論