引言

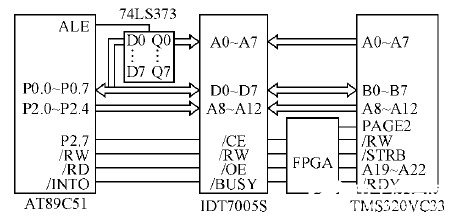

當(dāng)前國際先進(jìn)抗惡劣環(huán)境計(jì)算機(jī)相關(guān)產(chǎn)品的具有一個(gè)顯著特征,即采用由超大規(guī)模FPGA實(shí)現(xiàn)的可定制技術(shù),利用FPGA器件中專門設(shè)計(jì)的硬件乘法器、乘加結(jié)構(gòu)、DSP塊等硬件資源和通用的邏輯單元作為運(yùn)算的硬件基礎(chǔ),以任務(wù)的流水劃分和階段處理為手段,實(shí)現(xiàn)CPU、DSP的計(jì)算技術(shù)的重要補(bǔ)充功能。國外此類超大規(guī)模FPGA以Altera Stratix-x系列、Xilinx Virtex-x系列為主,相關(guān)產(chǎn)品中大都為Xilinx Virtexx系列FPGA,如GE Fanuc的SBC330、SBC610和Curtiss-Wright的VPX6-185等硬件模塊均采用了Xilinx Virtex-x系列FPGA,目前各家公司正在推出集成更多數(shù)量和更大規(guī)模的異構(gòu)技術(shù)產(chǎn)品,如Curtiss-Wright的CHAMP-FX2使用了雙路超大規(guī)模Virtex-5以實(shí)現(xiàn)功能高可伸縮的定制技術(shù)。

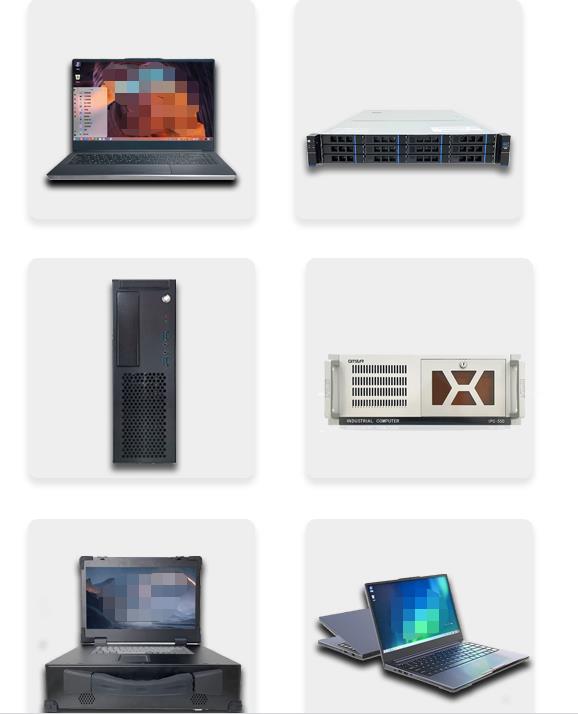

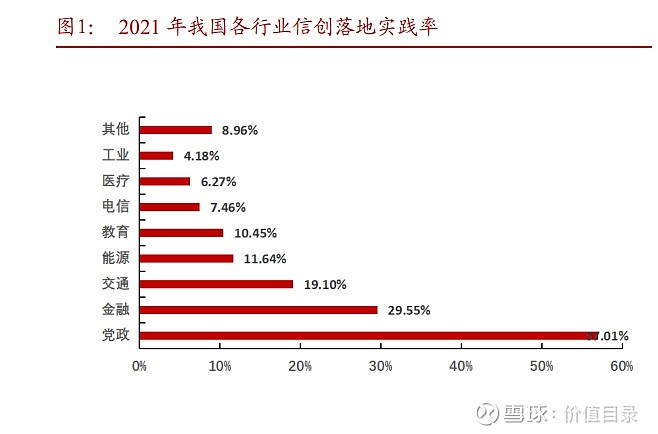

在國內(nèi),抗惡劣環(huán)境計(jì)算機(jī)產(chǎn)品主要以通用計(jì)算機(jī)為主,一般采用CompactPCI、VME等總線,使用1個(gè)單核或雙核CPU,系統(tǒng)性能較低。這些計(jì)算機(jī)通用性不強(qiáng)、種類多、開發(fā)成本高、可重用性弱、質(zhì)量保證難度大、資源利用率不高。而且這些計(jì)算機(jī)一般是使用國外的集成電路設(shè)計(jì)實(shí)現(xiàn),其關(guān)鍵的功能核心部分仍然無法實(shí)現(xiàn)自主可控。

隨著我國在國產(chǎn)基礎(chǔ)軟硬件方面的投入不斷加大以及國家政策的指導(dǎo),國產(chǎn)基礎(chǔ)軟硬件發(fā)展迅速,已接近國外同期水平。國內(nèi)處理器技術(shù)的研究正不斷深入,多核技術(shù)也已被納入相應(yīng)的發(fā)展路線圖。中國科學(xué)院計(jì)算技術(shù)研究所于2009年底推出龍芯3號處理器,龍芯3號片內(nèi)集成4個(gè)處理器核,處理器主頻1GHz以上。當(dāng)前,國內(nèi)基于FPGA的應(yīng)用已相當(dāng)成熟,盡管目前的抗惡劣環(huán)境計(jì)算機(jī)沒有采用可定制技術(shù),但幾乎都集成了Altera或Xilinx FPGA的應(yīng)用,如功能擴(kuò)展模塊、總線接口模塊等,國內(nèi)相關(guān)廠商已掌握時(shí)序邏輯定制技術(shù)、IP核的簡單復(fù)用和實(shí)現(xiàn)技術(shù)等FPGA 應(yīng)用的關(guān)鍵技術(shù),已具備較深厚的可定制實(shí)現(xiàn)技術(shù)基礎(chǔ)。

1、計(jì)算機(jī)組成原理

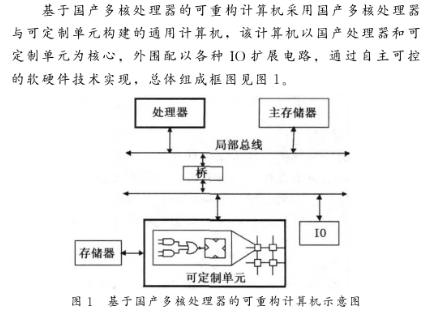

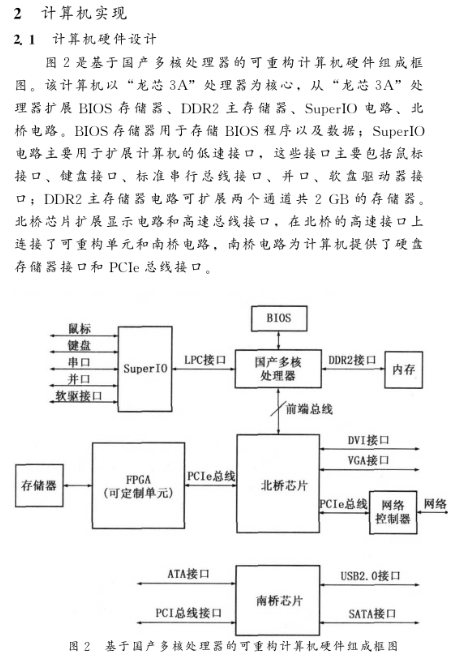

基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)各個(gè)主要的組成功能模塊之間采用高性能串行總線互連,如國產(chǎn)處理器與北橋芯片之間、北橋芯片與可定制單元之間、北橋芯片與南橋芯片之間均采用高速串行總線互連。可定制單元采用可編程邏輯實(shí)現(xiàn),處理器和具備硬件可編程能力的可重構(gòu)邏輯器件(以下簡稱可重構(gòu)器件)相結(jié)合,應(yīng)用的一部分被分配到處理器上執(zhí)行,另一部分則被映射到可重構(gòu)器件上執(zhí)行。微處理器上執(zhí)行的為軟件任務(wù),可重構(gòu)器件上運(yùn)行的硬件功能模塊可稱為硬件任務(wù)。

根據(jù)可定制單元配置文件中的編程信息,改變可定制單元中邏輯單元的功能以及連線的互連方式,從而改變計(jì)算機(jī)的功能,使其既能在設(shè)計(jì)實(shí)現(xiàn)時(shí)定制專用的計(jì)算部件,又能夠?qū)τ?jì)算資源進(jìn)行復(fù)用以實(shí)現(xiàn)多個(gè)不同的計(jì)算任務(wù)。

2.1.1 器件選型

計(jì)算機(jī)器件的選型不僅關(guān)系到計(jì)算機(jī)的整體性能,更重要的是,直接影響到潛在用戶目標(biāo)系統(tǒng)在開發(fā)時(shí)硬件設(shè)計(jì)的復(fù)雜度。因此在完成預(yù)期功能要求的前提下,計(jì)算機(jī)元器件的選型應(yīng)該充分的考慮計(jì)算機(jī)的應(yīng)用環(huán)境,如元器件工作與存儲(chǔ)的溫度范圍等。

2.1.2 內(nèi)存設(shè)計(jì)

龍芯3A處理器上集成2個(gè)DDR2通道,每個(gè)通道支持的容量為1GB,兩個(gè)通道共2GB.每個(gè)通道采用8顆16位位寬1GB的內(nèi)存顆粒,兩個(gè)通道共16顆內(nèi)存顆粒。其中,CLK0、2一組,CLK1、3一組,即顆粒1、2一組時(shí)鐘,顆粒3、4一組時(shí)鐘。特別注意:顆粒的鎖相環(huán)電源及地需用磁珠進(jìn)行隔離。通道的內(nèi)存顆粒連接示意圖如3所示。

2.1.3 電源設(shè)計(jì)

本設(shè)計(jì)的電源能夠提供12V、5V的電壓。其它種類電壓依照不同的電流需求由電源模塊或LDO等提供。系統(tǒng)的上電啟動(dòng)過程,可各路電源同時(shí)上電,也可配置處理器I/O、處理器核電壓、南橋核電壓、北橋核電壓的上電順序。

圖3 內(nèi)存顆粒連接示意圖

2.1.4 時(shí)鐘設(shè)計(jì)

設(shè)計(jì)中選用時(shí)鐘芯片SLG8LP625T來產(chǎn)生處理器HT差分時(shí)鐘200 MHz,北橋的PCIE及HT 差分時(shí)鐘100 MHz、14.318MHz,南橋的A-LINK 差分時(shí)鐘100MHz、14.318MHz、48MHz,4個(gè)PCIE網(wǎng)絡(luò)控制器的差分時(shí)鐘100MHz,SuperIO的48MHz.處理器的HT差分時(shí)鐘為做兼容設(shè)計(jì)采用200 MHz的有源晶振。掛在南橋PCI總線上的PCI橋PLX6254、IDE控制器SiI0680、SuperIO所需的33MHz時(shí)鐘由南橋輸出。處理器的PCI、BIOS時(shí)鐘33MHz由有源晶振及時(shí)鐘Buffer輸出,系統(tǒng)時(shí)鐘、內(nèi)存時(shí)鐘所需的25MHz由有源晶振輸出。4個(gè)網(wǎng)絡(luò)控制器所需25 MHz由Crystal輸出。SATA時(shí)鐘25MHz,RTC時(shí)鐘32.768kHz由Crystal輸出。PCI橋PCI6254時(shí)鐘66MHz由有源晶振輸出。

2.1.5 其它設(shè)計(jì)

由于整個(gè)系統(tǒng)不需要ACPI電源管理,故設(shè)計(jì)中不分S5及S0狀態(tài)的電源,但必要的上電先后順序需要滿足。處理器上電時(shí)序:當(dāng)系統(tǒng)上電時(shí),即由CPCI槽供5V、12V電源,處理器核電壓由3.3V的POWERGOOD作為使能信號產(chǎn)生,滿足要求的上電時(shí)序。系統(tǒng)啟動(dòng)時(shí)序:南北橋核電壓的POWERGOOD信號經(jīng)MAX708延時(shí)200ms后輸出到南北橋芯片,延時(shí)信號的上升沿作為觸發(fā)信號輸出到南橋使整個(gè)系統(tǒng)啟動(dòng)。延時(shí)信號SB_NB_PWRGD與南北橋復(fù)位信號MASTER_RST/經(jīng)與門后作為處理器的復(fù)位信號。南橋的LDT _PG、LDT_RST分別作為HT_POWEROK、HT_RST接到處理器,以滿足HT總線的上電時(shí)序。南橋的PCI_RST作為南橋PCI總線的復(fù)位信號。南橋的A_RST作為全局復(fù)位信號復(fù)位IDE控制器、網(wǎng)絡(luò)控制器、北橋等設(shè)備。系統(tǒng)復(fù)位時(shí)序:復(fù)位按鈕可控制整個(gè)系統(tǒng)的復(fù)位。當(dāng)系統(tǒng)作為CPCI槽上的從設(shè)備時(shí),槽上引入的復(fù)位信號可對整個(gè)系統(tǒng)復(fù)位。

2.2 可重構(gòu)設(shè)計(jì)

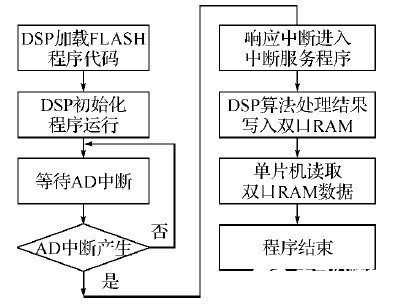

基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)的FPGA 配置優(yōu)化和在線重配置如圖4所示。它能夠在計(jì)算任務(wù)運(yùn)行的同時(shí)對可重構(gòu)器件上的邏輯資源進(jìn)行重構(gòu)。計(jì)算任務(wù)被劃分為多個(gè)配置文件,每次在可重構(gòu)器件上加載的配置文件與計(jì)算任務(wù)中的一個(gè)部分相對應(yīng),因此在計(jì)算任務(wù)的執(zhí)行過程中需要對可重構(gòu)器件進(jìn)行多次重構(gòu)。

圖4 FPGA配置優(yōu)化和在線重配置示意

基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)設(shè)計(jì)流程如圖5,一個(gè)應(yīng)用首先要進(jìn)行軟件、硬件劃分,決定應(yīng)用的什么部分用軟件實(shí)現(xiàn),什么部分用硬件實(shí)現(xiàn)。在軟、硬件劃分時(shí),通常將控制過程的功能模塊由軟件實(shí)現(xiàn),將數(shù)據(jù)計(jì)算密集型的功能模塊由硬件來實(shí)現(xiàn)。在軟、硬件劃分后,就將軟件任務(wù)映射到微處理器,硬件任務(wù)映射到可定制單元(FPGA)。在任務(wù)的劃分階段采用非重疊功能調(diào)度、自動(dòng)化建模(硬件任務(wù)劃分、映射)技術(shù)、可重構(gòu)硬件虛擬抽象等手段實(shí)現(xiàn)可重構(gòu)計(jì)算。

圖5 基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)設(shè)計(jì)流程

2.3 基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)的IP核設(shè)計(jì)

IP設(shè)計(jì)首先是進(jìn)行規(guī)格的定義,根據(jù)規(guī)格提出功能需求后,建議軟硬件的協(xié)同仿真環(huán)境后進(jìn)行子模塊的設(shè)計(jì)實(shí)現(xiàn),具體的設(shè)計(jì)流程見圖6.

基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)的構(gòu)件及IP核集成和測試是為了保證設(shè)計(jì)實(shí)現(xiàn)提供的功能的正確性,保證功能與設(shè)計(jì)規(guī)格的一致性。通過研究掌握當(dāng)前主要的驗(yàn)證手段和驗(yàn)證策略,形成一套成體系的設(shè)計(jì)流程。

2.4 基于FPGA的計(jì)算加速設(shè)計(jì)

以國產(chǎn)多核處理器和可定制單元為載體,采用多核虛擬化、FPGA算法加速、負(fù)載均衡、共享數(shù)據(jù)一致性等技術(shù),在通過FPGA對計(jì)算加速和異構(gòu)多處理數(shù)據(jù)層次之間進(jìn)行強(qiáng)實(shí)時(shí)傳遞的基礎(chǔ)上,實(shí)現(xiàn)可定制異構(gòu)多處理架構(gòu),重點(diǎn)解決計(jì)算加速問題。可定制異構(gòu)多處理架構(gòu)如圖7.

3 、結(jié)束語

基于國產(chǎn)龍芯3A處理器的CPCI計(jì)算機(jī)模塊的研制,不僅實(shí)現(xiàn)核心技術(shù)國產(chǎn)化,消除使用國外產(chǎn)品的安全隱患,擺脫受制于人的不利局面,而且隨著龍芯處理器的更新?lián)Q代,龍芯3A處理器是目前國產(chǎn)處理器中性能最高的芯片,4個(gè)核心處理器,每個(gè)核主頻可到800MHz左右,基于國產(chǎn)多核處理器的可重構(gòu)計(jì)算機(jī)采用國產(chǎn)多核處理器和FPGA實(shí)現(xiàn),具有良好的計(jì)算性能。

圖6 IP核設(shè)計(jì)流程

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19404瀏覽量

230876 -

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605336 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7534瀏覽量

88488

發(fā)布評論請先 登錄

相關(guān)推薦

迅為3A6000_7A2000核心主板龍芯全國產(chǎn)處理器LoongArch架構(gòu)

迅為3A6000_7A2000開發(fā)板龍芯全國產(chǎn)處理器與龍芯 3A5000完全兼容

【懸賞100塊】如何實(shí)現(xiàn)FPGA可重構(gòu)計(jì)算(Android平臺(tái))

星載可重構(gòu)計(jì)算機(jī)硬件驗(yàn)證平臺(tái)設(shè)計(jì)

我國首臺(tái)龍芯3A高性能計(jì)算機(jī)誕生

龍芯3A4000處理器實(shí)測 未來或?qū)⑦_(dá)到主流桌面處理器可用的水平

龍芯3A4000處理器的性能測試,相同主頻性能提升幅度超過100%

龍芯芯片出貨量突破50萬顆,3A/3B5000系列主頻可提升2.5GHz以上

龍芯3C5000 16核處理器全國產(chǎn)工業(yè)計(jì)算機(jī)模塊成功上市

國產(chǎn)計(jì)算機(jī)平臺(tái)介紹——龍芯

國產(chǎn)龍芯3A6000微型計(jì)算機(jī)BOX-T6A11-LX,加速國產(chǎn)化替代

龍芯中科榮獲個(gè)人計(jì)算機(jī)處理器成就獎(jiǎng)

國產(chǎn)計(jì)算機(jī)平臺(tái)介紹——龍芯

龍芯ITX主板GM7-3601搭載龍芯3A5000處理器的工控主板

基于國產(chǎn)龍芯3A處理器和FPGA器件實(shí)現(xiàn)可重構(gòu)計(jì)算機(jī)的設(shè)計(jì)

基于國產(chǎn)龍芯3A處理器和FPGA器件實(shí)現(xiàn)可重構(gòu)計(jì)算機(jī)的設(shè)計(jì)

評論