很多總線標準中,從設備必須譯碼所有的地址,這稱為全地址譯碼。比如在PCI總線中,每一個從設備都必須具有32位的地址輸入,并對這32位的地址進行譯碼以確定如何響應主設備的請求。

片上總線規范比如Wishbone規范支持部分地址譯碼。在部分地址譯碼總線規范中,從設備只需要譯碼自己所使用的地址空間。比如如果一個從設備只有4個地址,它就只需譯碼2比特地址而不是32位地址。這樣做的好處是:地址譯碼速度快,地址譯碼邏輯少,從設備可自由定義地址總線寬度。

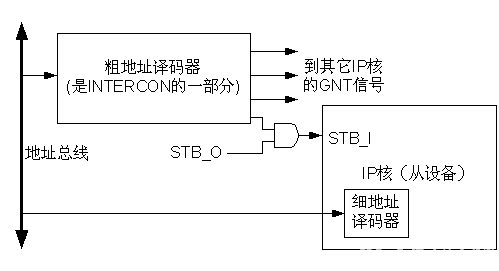

圖26 Wishbone部分地址譯碼的實現

Wishbone部分地址譯碼的實現如圖26所示。對于圖中所示IP核,我們假設其只有4個地址,對應4組寄存器。地址譯碼器首先譯碼出其地址并給出選擇信號,該選擇信號與共享總線的STB_O相與輸入到IP核的STB_I。而地址總線的最低2位被直接連接到IP核,IP核再根據這兩位譯碼出當前操作選中的是具體哪個寄存器。

Wishbone共享總線示例中的仲裁器可以設計如下:

//the ACMP0 is for slave0: Flash

//the ACMP1 is for slave1: SRAM

module address_decoder2S(addr_i,ACMP0,ACMP1);

input [31:0]addr_i;

output ACMP0,ACMP1;

parameter ADDR_LOW_S0=32'b0;

parameter ADDR_HIGH_S0=32'h1FFFFF;//2M space for Slave 0;

//the rest of the space for Slave 1,so we do not need a dummuy slave;

assign ACMP0=addr_i<=ADDR_HIGH_S0;

assign ACMP1=~ACMP0;

endmodule

-

寄存器

+關注

關注

31文章

5363瀏覽量

120952 -

總線

+關注

關注

10文章

2900瀏覽量

88293 -

Wishbone

+關注

關注

0文章

16瀏覽量

10439

原文標題:【博文連載】Wishbone總線地址譯碼

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

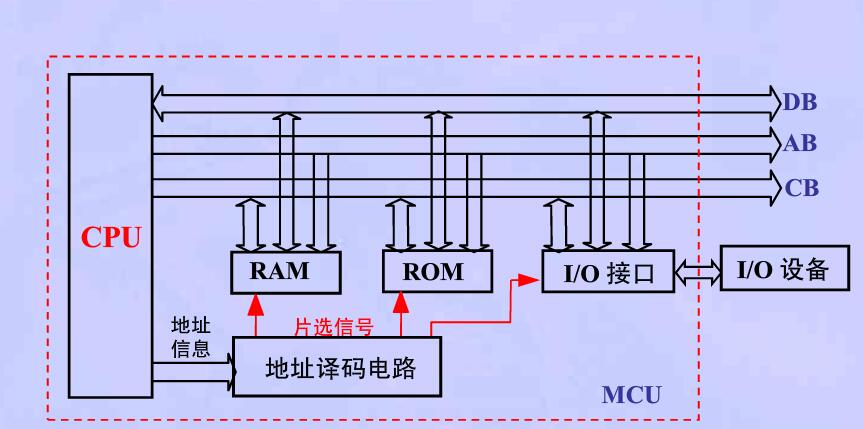

51單片機P0口已用作地址\數據總線,還能用來當做普通I\O使用嗎?

請問AD5933電路設計需要把模擬部分和數字部分地隔離嗎?

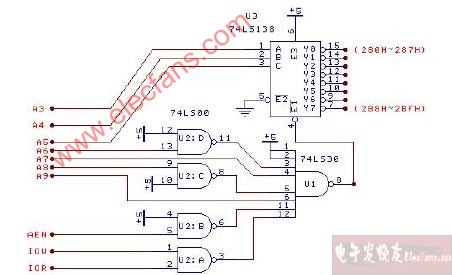

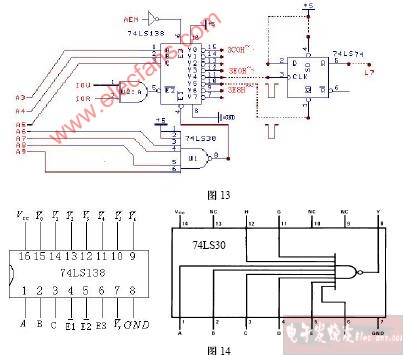

IO接口地址譯碼電路

I/O地址譯碼實驗

Wishbone部分地址譯碼的實現

Wishbone部分地址譯碼的實現

評論