你在解決系統計時問題時,是不是需要使用分立式晶振和振蕩器呢?對于大多數硬件設計師來說,這看起來的確是一個顯而易見的方法,又有誰會到互聯網上費時費力地搜尋那些包括時鐘發生器IC和緩沖器/分布器件的經優化時鐘樹解決方案呢。雖然節省時間,但是這個使用分立式晶振和振蕩器的方法經常會導致物料清單 (BOM) 成本的增加,并且會降低整個系統的性能。WEBENCH? Clock Architect(時鐘架構師)是業內首款時鐘和定時工具;這個工具建議用戶使用一個包含TI廣泛計時產品庫中器件的系統時鐘樹解決方案。這個已獲專利的多部分推薦算法—這款工具的精髓所在—為那些尋找高性能、靈活計時解決方案的設計師們提供快速解決方案,以及順暢的使用體驗。

除了推薦經優化的時鐘樹解決方案,這款工具特有先進鎖相環 (PLL) 濾波器設計功能和相位噪聲仿真功能,從而使你能夠仿真并優化時鐘樹設計,以滿足系統的需求。我們來一起看一看最近升級后的某些新特性。

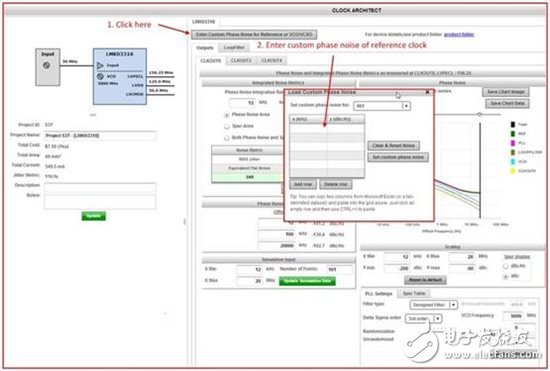

現在你可以輸入與外部基準有關的定制相位噪聲系統配置,比如說晶體振蕩器 (XO)、壓控晶體振蕩器 (VCXO) 和壓控振蕩器 (VCO)。外部基準源的準確建模可以極大地提升器件輸出時鐘相位噪聲/抖動仿真結果的精度。請見圖1。

圖1.輸入與基準時鐘有關的定制相位噪聲

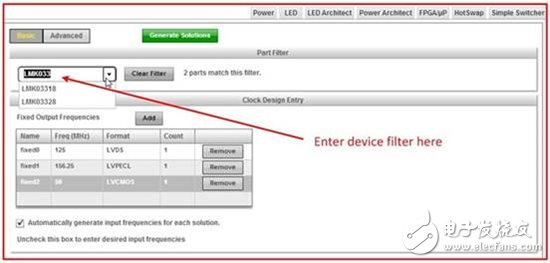

WEBENCH Clock Architect讓你從一個下拉列表中選擇一個特定的TI計時器件(或者使用常規表示法的多個器件)。圖2是你在選擇所需器件、敲入輸入和輸出頻率、并且設計一個環路濾波器或仿真相位噪聲時的屏幕截圖。

圖2:器件過濾器

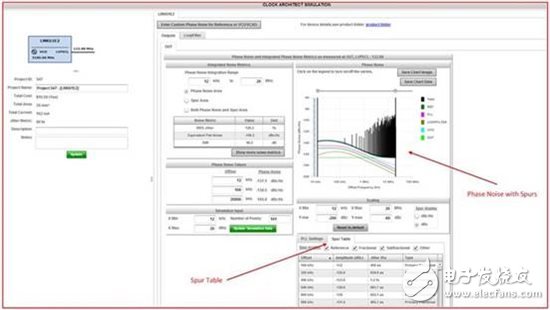

在這款工具中得出的相位噪聲仿真值與實際芯片性能進行緊密匹配。然而,直到最近,分數倍分頻鎖相環 (fractional-N PLL) 的相位噪聲仿真并不包含雜散。對WEBENCH Clock Architect的最近一次升級包括PLL相位檢測器的建模, 以及針對大多數器件的分數、次分數和其它部件特有雜散的建模。我們一直努力提高這款工具的雜散建模水平,并且不斷升級與特定產品相關的功能。圖3顯示的是一個分數倍分頻鎖相環的示例,以及它所生成的帶有雜散的輸出時鐘相位噪聲曲線圖。

圖3:帶有雜散的輸出時鐘相位噪聲曲線圖

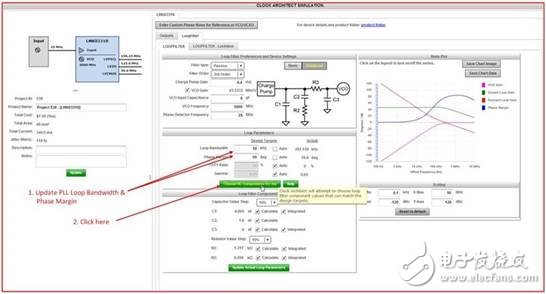

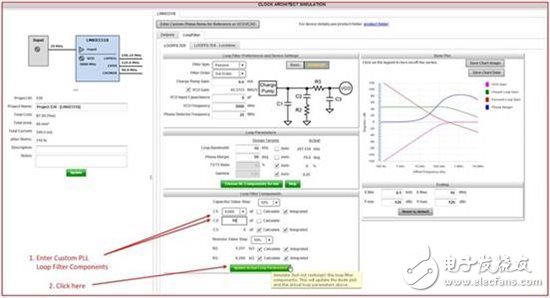

我們也對PLL濾波器設計功能進行了某些升級。在最近發布的版本中,如圖4的屏幕截圖中所示,高級用戶能夠定制PLL帶寬、相位裕量和gamma值等環路濾波器參數。你可以輸入定制環路濾波器組件值或者從一個整數值列表中選擇(如果這款器件提供這些數據的話),然后通過仔細查看波特圖來檢查環路穩定性(圖5)。由于包含有PLL鎖定時間建模功能,你可以驗證環路濾波器設計策略對于PLL鎖定時間(以及相位噪聲)的影響,并考慮必要的設計均衡與取舍(圖6)。

圖4:定制環路參數選擇

圖5:定制環路濾波器組件選擇和仿真

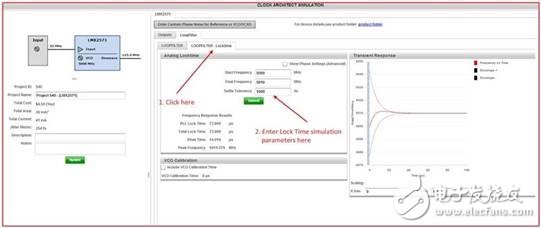

圖6:鎖定時間仿真和估算

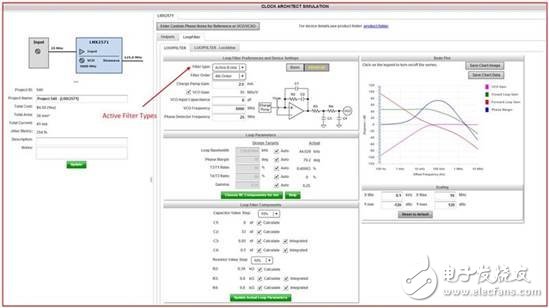

直到近期,WEBENCH Clock Architect還只能夠支持無源環路濾波器設計。現在,由于最新的一次升級,這個工具支持有源環路濾波器設計(在Advanced(高級)設置下)。相對于有源環路濾波器,無源環路濾波器通常由于其低成本、簡單性和帶內相位噪聲等因素而受到用戶歡迎。不過,在特定情況下—當VCO需要的調諧電壓高于PLL電荷泵所能提供的電壓時,或者當VCXO的輸入阻抗不足時—就必須使用有源濾波器了。請見圖7中的下拉菜單。

圖7:有源環路濾波器選型和仿真

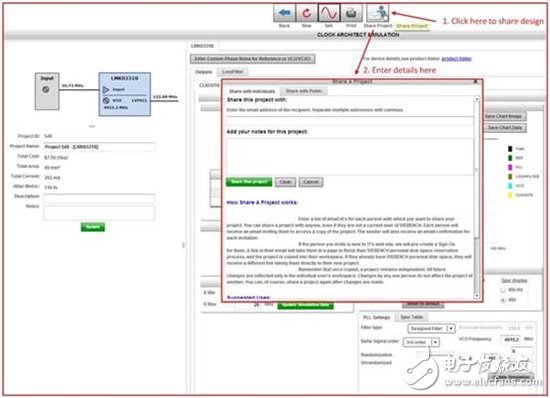

對WEBENCH Clock Architect的最后一個重大升級就是可以與其他用戶分享設計。只需單擊圖8中顯示的Share Project(分享項目)按鈕,你就可以生成一個包含所有設計細節的PDF格式的報告。

圖8:分享設計

為了滿足應用的嚴格要求,TI具有一個健康的產品庫,其中包含靈活且高性能時鐘發生器、時鐘抖動消除器、射頻 (RF) PLL/合成器、時鐘緩沖器和振蕩器。

我所中意的時鐘發生器和可編程振蕩器分別是LMK03328和LMK61E2。這些器件具有超低RMS抖動性能(典型值100fs)、靈活性(集成EEPROM和ROM),以及豐富特性(支持頻率裕量設定)。當你的下一個設計使用這些器件以及TI.com內所提供的很多其它器時,你可以用WEBENCH Clock Architect來仿真這個設計的相位噪聲。

-

振蕩器

+關注

關注

28文章

3847瀏覽量

139278 -

過濾器

+關注

關注

1文章

432瀏覽量

19685 -

環路濾波器

+關注

關注

3文章

26瀏覽量

13182

發布評論請先 登錄

相關推薦

分立式整流器的整流原理

航天級100krad–2.5V分立式負LDO線性穩壓器電路

晶體振蕩器怎么判斷好壞

愛普生LVDS差分晶振MG7050VAN,X1M0004210003高頻振蕩器6G無線晶振

PMP23242.1-微處理器單元 (MPU) 分立式汽車電源PCB layout設計

如何判斷是否需要使用分立式晶振和振蕩器呢?

如何判斷是否需要使用分立式晶振和振蕩器呢?

評論