0 引言

AIS系統是一種船舶交通信息交換系統,船載AIS設備不斷發送自身信息,如航向、噸位等,用以領航調度、避免碰撞。隨著海運貿易的高速增長,迫切需要建立對大片海域船舶動態的實時監控系統,衛星平臺因覆蓋范圍廣而受到重視。加拿大等國家相繼發射載有AIS信號接收設備的衛星[1]。AIS系統采用高斯濾波最小頻移鍵控(Gaussian Filtered Minimum Shift Keying,GMSK)調制,可以通過相干方式或非相干方式解調。相干解調具有較好的抗噪聲性能[2],但是需要準確恢復載波頻率,而載有AIS設備的近地衛星軌道高度一般在500 km左右,多普勒頻移可達±4 kHz,因此精確的載波恢復比較困難;非相干解調主要采用鑒頻器,從接收GMSK信號中提取頻率的變化信息,因此對頻偏不敏感且結構簡單,在很多GMSK移動通信系統中得到了應用[3-4],如GSM。目前,AIS接收機射頻端多采用一級或二級下變頻方案[5-6],這種方案使射頻前端硬件比較復雜,硬件成本高。鑒于AIS信號是窄帶信號,因此本文設計中對接收到的射頻信號直接帶通采樣,以簡化接收機硬件結構。

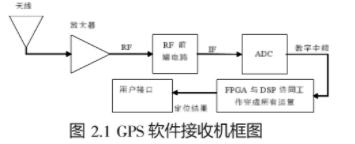

本文主要工作如下:在Xilinx xc4vlx80 FPGA上設計了基于帶通采樣的AIS非相干解調軟件接收機,設計文件通過綜合映射后下載到FPGA中,以實際AIS信號源作為測試信號,通過嵌入式邏輯分析工具Chipscope在PC上觀察FPGA內部信號來驗證設計,并給出了硬件資源消耗。

1 GMSK信號調制和非相干解調原理

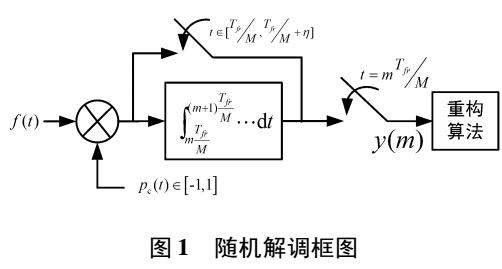

AIS信號是GMSK調制信號,其調制和非相干解調過程如圖1所示。

發射端比特脈沖為:

比特流d(t)通過帶寬時間積(Bandwidth-Time product,BT)為BbTb的高斯濾波器進行脈沖成型。Bb為高斯濾波器的3 dB帶寬,Tb為比特速率。高斯成型濾波器的沖激響應為:

式中*表示卷積運算。最后通過電壓/頻率(V/F)轉換,形成調頻信號并調制到規定頻段發射出去。

對于非相干解調的接收機,首先將接收信號進行正交下變頻,濾除高頻分量和帶外噪聲后得到基帶正交信號I(t)、Q(t),再通過下式進行頻率/電壓(F/V)轉換:

2 AIS接收機的FPGA設計

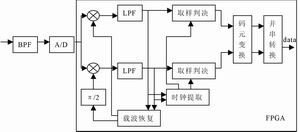

帶通采樣AIS非相干接收機系統結構如圖2所示。

2.1 帶通采樣率

AIS信號有A、B兩個發射頻點,分別為161.975 MHz和162.025 MHz,數據速率Rb為9.6 kb/s,帶寬不超過25 kHz,接收機射頻前端的帶通濾波器(Band Pass Filter,BPF)中心頻率為162 MHz,帶寬為250 kHz,因此可對BPF輸出射頻信號直接采樣。理論上ADC的帶通采樣頻率fS1只要滿足下式即可:

式中,B為BPF的帶寬,fH為采樣信號的最高頻率成分,[]表示取不超過該數的最大整數。采樣頻率越小,對FPGA的處理速度要求就越低。但實際系統中由于BPF過渡帶的緩變特性,一些邊帶噪聲不能被完全抑制,當采樣頻率過小時,采樣得到的信號頻譜周期重疊次數過多,導致更多的噪聲疊加到有用信號上。因此,本系統采用的采樣時鐘頻率為fS1=24 MHz。帶通采樣后AIS信號中心頻率fC1可通過下式計算:

2.2 兩級數字下變頻結構

系統中FPGA和ADC共用時鐘源,FPGA系統主頻為fSYS=24 MHz。天線接收的AIS信號經過低噪放和帶通濾波,再經過14 bit ADC采樣后,輸入FPGA。輸入FPGA的AIS信號中心頻率fC1=6 MHz、采樣率fS1=24 MHz、帶寬為250 kHz。由于信號帶寬遠小于采樣頻率,可以進行下變頻和降采樣處理,以減輕后級處理壓力。首先將采樣信號與FPGA內數控振蕩(NCO)IP核產生的位寬為10 bit、頻率fO1=6 MHz的正弦信號進行混頻,再通過數據位寬為16 bit、截止頻率為100 kHz的51階低通濾波器,濾除高頻成分;再對低通信號進行48倍降采樣,得到的數據速率為500 kHz、中心頻率為±25 kHz(A、B兩個發射頻點)的AIS信號;再將該信號與NCO產生的位寬為10 bit、頻率fO2=25 kHz的正弦信號進行混頻,再通過數據位寬為16 bit、截止頻率為25 kHz的51階低通濾波器來濾除高頻分量,得到包含多普勒頻偏(小于4 kHz)的基帶正交信號。

采用這種兩級下變頻的好處,除了可以降低采樣速率,減輕FPGA處理壓力外,還可以減少邏輯資源消耗。如果對采樣率為fS1=24 MHz的信號直接進行正交數字下變頻,由于混頻后的FIR低通濾波器驅動時鐘頻率(即系統主頻fSYS=24 MHz)和輸入濾波器的混頻信號數據速率(即采樣率為fS1=24 MHz)相同,那么FIR濾波器IP核經過綜合后,需要26個乘法器。而正交下變頻需要兩個低通濾波器,因此共需要26×2=52個乘法器;采用兩級下變頻方案時,一級混頻后的濾波器同樣需要26個乘法器,降采樣后,輸入濾波器的混頻信號數據速率降為fS2=500 kHz,而驅動時鐘不變,仍為fSYS=24 MHz,因此在輸入一個數據的周期內,最多可以復用該乘法器fSYS/fS2=48次,大于51階FIR濾波器所需要的26個乘法器,所以正交下變頻后的濾波器經綜合,僅需1個乘法器即可,如圖3所示。兩級下變頻中需要3個低通濾波器(如圖2所示),然而需要的乘法器個數僅為26+1×2=28個。

2.3數字鑒頻以及后檢測濾波

對正交下變頻得到的基帶正交信號進行式(6)所示的數字鑒頻操作,提取頻率信號。數字鑒頻器的硬件主要由延時模塊、乘法器、除法器、加法器和減法器構成。由于理論上數字鑒頻是非線性操作,對噪聲十分敏感,輸出中會包含高頻的噪聲分量,因此有必要對鑒頻器輸出進行后檢測低通濾波。圖4是在MATLAB中,仿真采用不同截止頻率的低通濾波器時AIS解調的誤碼率曲線,橫坐標為信號功率和噪聲功率比值。由圖中可以看出,低通濾波器的截止頻率Bo為0.4Rb(Rb為AIS比特速率)時,誤碼性能最好。因此,FPGA中后檢測濾波的帶寬設為0.4Rb=0.4×9.6 kb/s=3.84 kHz。

3 AIS信號解調實際測試

在Xilinx開發環境ISE13.2中設計AIS接收機各模塊,將設計好的模塊進行綜合、映射、布局布線,生成下載文件。并調用Chipscope嵌入式邏輯分析儀IP核,通過JTAG仿真器來連接FPGA和PC,以便實時觀察FPGA內部信號。利用實際AIS信號源作為測試信號,用同軸線將AIS信號源輸出連接到模數轉換器AD9246輸入,帶通采樣信號讀入FPGA進行解調。觀察到各級信號如圖5所示。在圖5(d)中可以看到A、B兩個不同頻點AIS信號的24比特位同步序列00110011…0011以及幀起始標志01111110。設計所占用的Slice數為231,僅占總資源數的1%。

4 結束語

本文根據GMSK信號的非相干解調原理,在Xilinx FPGA上設計了帶通采樣的AIS非相干接收機,利用AIS窄帶信號的特點,采用兩級下變頻方案,將數據速率降至合理范圍,減輕FPGA處理壓力,同時也大大減少了低通濾波器對硬件邏輯資源的消耗;在MATLAB中進行了AIS解調的理論仿真,設置了一個最優的數字鑒頻后檢測濾波器截止頻率,以抑制實際環境中的噪聲干擾;最后在硬件系統上對設計的接收機進行了測試,并觀察到解調出的A、B兩個頻點的基帶信號。該設計消耗的邏輯資源不到器件總資源數的1%,可以為AIS接收機小型化、批量化生產提供參考。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605176 -

AIS

+關注

關注

0文章

23瀏覽量

13164

發布評論請先 登錄

相關推薦

如何實現基于多相濾波的數字接收機的FPGA?

中頻采樣多模式數字接收機的設計與實現

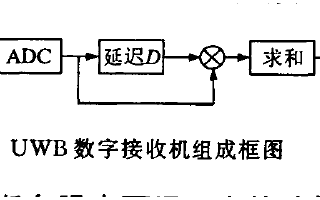

UWB定位系統中標簽接收機的FPGA實現

DS/FH混合擴頻接收機解擴及同步技術的FPGA實現

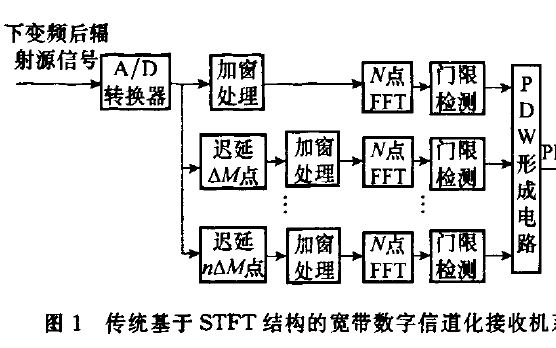

寬帶數字信道化接收機的FPGA實現

高性能、雙通道IF采樣接收機

壓縮采樣接收機抗ADC非線性影響

基于帶通采樣的AIS非相干解調軟件接收機的FPGA實現設計

基于FPGA-DSP平臺實現GPS衛星導航接收機的設計

如何使用FPGA實現ADC的TR UWB數字接收機性能

如何使用FPGA實現高效的寬帶數字接收機

關于帶通采樣星載AIS非相干接收機的FPGA實現

關于帶通采樣星載AIS非相干接收機的FPGA實現

評論