FPGA發(fā)展到今天,SerDes (Serializer - Deserializer) 基本上是標(biāo)配了。從PCI到PCI Express,從ATA到SATA,從并行ADC接口到JESD204,從RIO到Serial RIO,……等等,都是在借助SerDes來(lái)提高性能。SerDes是非常復(fù)雜的數(shù)模混合設(shè)計(jì),用戶(hù)手冊(cè)的內(nèi)容只是描述了森林里面的一棵小樹(shù),并不能夠解釋SerDes是怎么工作的。而本文也主要是基于Lattice ECP3和ECP5 的SerDes UG,來(lái)簡(jiǎn)單地介紹一下Lattice ECP3&ECP5 SerDes的一些基本特性。

廢話(huà)不多說(shuō),進(jìn)入正題。

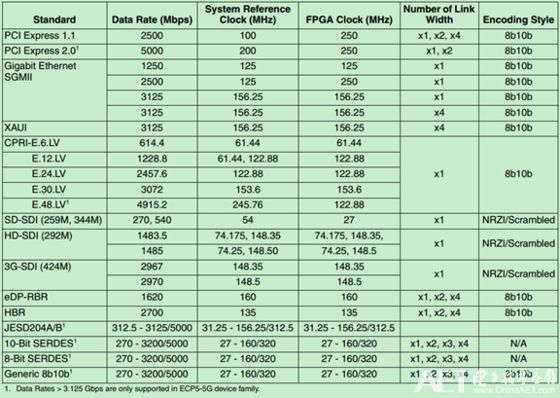

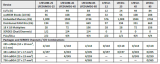

Lattice的ECP3/ECP5系列FPGA內(nèi)部集成了SerDes/PCS的硬核(Hard Core),其速率最高可達(dá)3.2Gbps,而ECP5-5G系列的SerDes最高可達(dá)5Gbps。Lattice的SerDes是基于CML信號(hào)的,借助 PCS(物理編碼子層,Physical Coding Sublayer)可以支持PCI Express、JESD204A/B、SD-SDI、HD-SDI、3G-SDI、GbE、CPRI、Gigabit Ethernet (1GbE and SGMII)和XAUI等多種串行通信協(xié)議,具體如下圖所示。

就PCIe(PCI Express)而言,ECP3/ECP5可支持1.0/1.1版本(2.5Gbps),而ECP5-5G還可支持2.0版本(5Gbps)。借助Lattice提供的PCIe相關(guān)的IP(Endpoint&Root),可以快速的完成基于FPGA的PCIe設(shè)備的開(kāi)發(fā)。

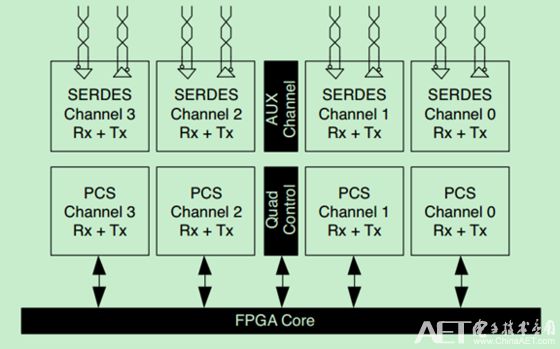

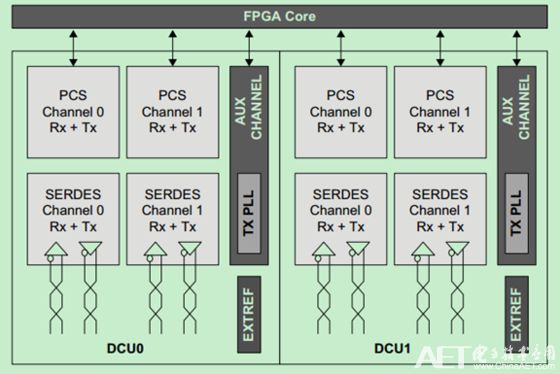

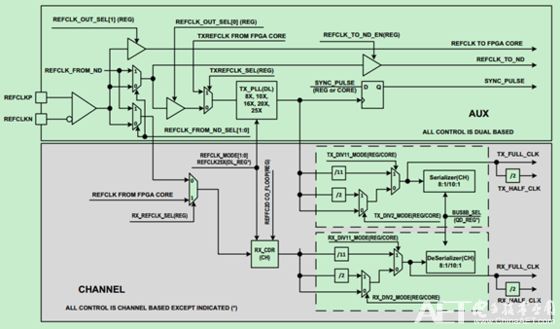

Lattice ECP3,ECP5(ECP5-5G)的SerDes/PCS結(jié)構(gòu)基本相同,區(qū)別主要在于ECP5將兩個(gè)SerDes/PCS通道合并到一個(gè)叫做DCU的模塊中去。ECP5的每一個(gè)DCU均包含一個(gè)AUX通道(以及TxPLL),而ECP3每四個(gè)SerDes/PCS通道才包含一個(gè)AUX通道。ECP3和ECP5的結(jié)構(gòu)圖分別如下圖所示:

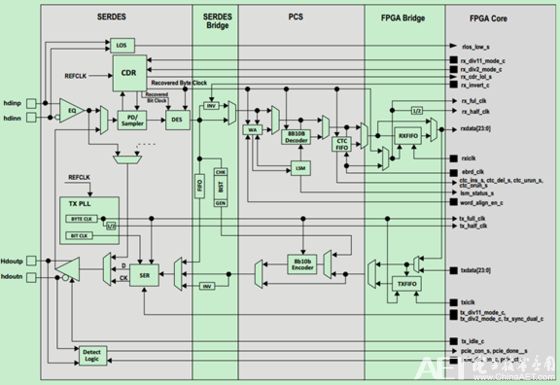

其中,ECP5的SerDes/PCS的單個(gè)通道的詳細(xì)結(jié)構(gòu)圖如下圖所示:

ECP5的SerDes時(shí)鐘結(jié)構(gòu)圖如下:

注:本文只是對(duì)Lattice ECP3/ECP5器件中的SerDes/PCS進(jìn)行了簡(jiǎn)要的介紹,具體還請(qǐng)閱讀參考閱讀中的相關(guān)UG。

-

SerDes

+關(guān)注

關(guān)注

6文章

200瀏覽量

34985 -

Lattice

+關(guān)注

關(guān)注

12文章

82瀏覽量

71400

原文標(biāo)題:【博文連載】PCIe掃盲——Lattice ECP3/ECP5 SerDes簡(jiǎn)介

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

萊迪思ECP5系列FPGA續(xù)寫(xiě)“低功耗”神話(huà)

【技術(shù)求教】Lattice-ECP3如何實(shí)現(xiàn)雙程序動(dòng)態(tài)加載

求指導(dǎo)用ECP3芯片來(lái)驅(qū)動(dòng)液晶顯示的設(shè)計(jì)思路

請(qǐng)問(wèn)誰(shuí)有LATTICE ECP3系列的開(kāi)發(fā)資料嗎?

如何使用ECP5FPGA解決網(wǎng)絡(luò)邊緣應(yīng)用設(shè)計(jì)挑戰(zhàn)

Lattice_EC-ECP_Std_Eval_Board Re

萊迪思發(fā)布適用于寬帶接入和視頻等應(yīng)用的ECP5 FPGA產(chǎn)品系列

Lattice ECP5和ECP5-5G FPGA系列VIP處理器解決方案

Lattice公司的DSP架構(gòu)

ECP5-5G及ECP5-5G Versa開(kāi)發(fā)板主要特性

基于全新ECP5-5G器件的IP和解決方案, 適用于工業(yè)和通信應(yīng)用

Lattice ECP3 FPGA系列AMC評(píng)估開(kāi)發(fā)方案

對(duì)Lattice ECP3/ECP5器件中的SerDes/PCS進(jìn)行了簡(jiǎn)要的介紹

對(duì)Lattice ECP3/ECP5器件中的SerDes/PCS進(jìn)行了簡(jiǎn)要的介紹

評(píng)論