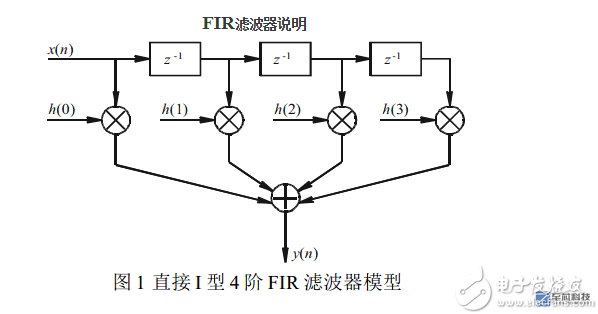

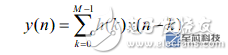

本例程實(shí)現(xiàn)8階濾波器,9個(gè)系數(shù),由于系數(shù)的對(duì)稱性,h(0)=h(8),h1(1)=h(7),h(2)=h(6),h(3)=h(5),h(4)為中間單獨(dú)一個(gè)系數(shù)。根據(jù)公式:

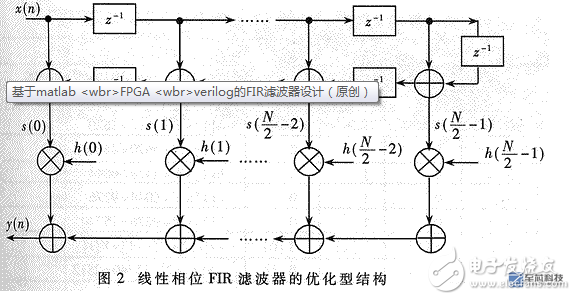

實(shí)現(xiàn)框圖:

推導(dǎo)出當(dāng)系數(shù)N為偶數(shù)時(shí),例如N=4:y(n)=h(0)*{x(0)+x(n-3)}+h(1)*{x(n-1)+x(n-2)}

當(dāng)系數(shù)N為奇數(shù)時(shí),例如N=5:

y(n)=h(0)*{x(0)+x(n-1)}+h(1)*{x(n-1)+x(n-3)}+h(2)*x(n-2)

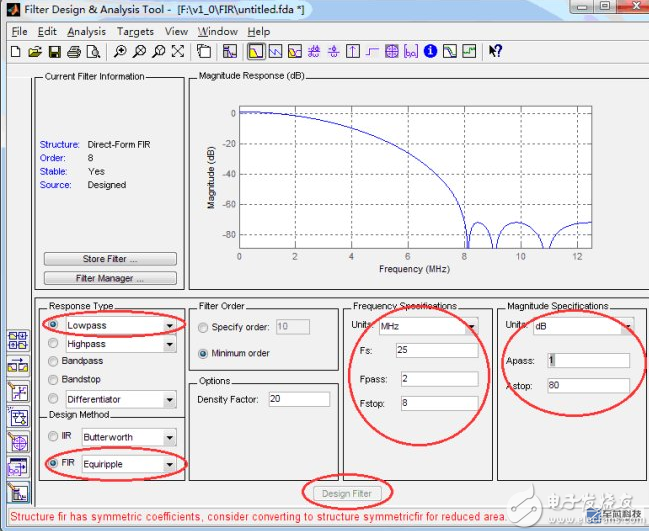

1、用matlab生成和量化濾波器系數(shù)

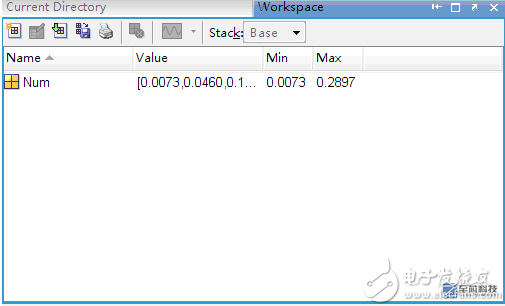

設(shè)置參數(shù)后,點(diǎn)擊“Design Filter”按鈕,“file”—“export”,把濾波器系數(shù)導(dǎo)出到workspace,如下圖:

執(zhí)行命令:Num=Num’ ,把濾波器系數(shù)拷貝到文件COFFICIENT.dat中。

量化系數(shù):在matlab中運(yùn)行quantization.m

2、說明

用matlab程序sin_1MHz_gen.m生成正弦波波形表,改變變量f0 = 1.5e6可以生成不同頻率的波形。把第一個(gè)周期的波形數(shù)據(jù)存入signal_1m.dat文件中,存入的數(shù)據(jù)個(gè)數(shù)為Fs/Fo的最小正整數(shù)之比的分子,比如Fs=25MHz,F(xiàn)o=0.3MHz,Fs/Fo=250/3(Fs=25/24MHz),則存入文件signal_1m.dat的波形數(shù)據(jù)個(gè)數(shù)為開頭的250個(gè)數(shù)據(jù)。相應(yīng)的signal_gen0.v中的語句if(i0<50)相應(yīng)的改為if(i0<250)。仿真時(shí)signal_1m.dat放在仿真目錄下

3、濾波器的multisim仿真

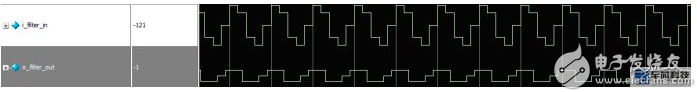

運(yùn)行matlab,用sin_1MHz_gen.m產(chǎn)生5MHz(f0 =5e6)正弦波信號(hào),F(xiàn)s/Fo=5,把數(shù)據(jù)hex_sin_data的前5個(gè)數(shù)據(jù)存入signal_1m.dat文件,相應(yīng)的signal_gen0.v中的語句if(i0<50)相應(yīng)的改為if(i0<5)。

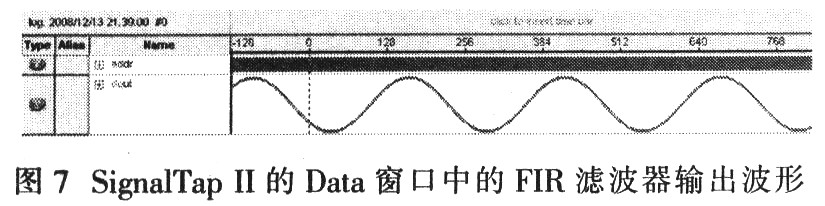

仿真的波形如下圖(fir濾波器的輸入輸出信號(hào)):

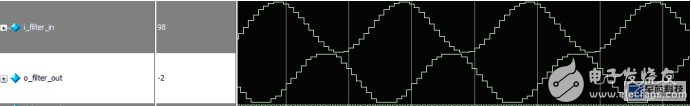

運(yùn)行matlab,用sin_1MHz_gen.m產(chǎn)生1MHz(f0 =1e6)正弦波信號(hào),F(xiàn)s/Fo=25,把數(shù)據(jù)hex_sin_data的前5個(gè)數(shù)據(jù)存入signal_1m.dat文件,相應(yīng)的signal_gen0.v中的語句if(i0<5)相應(yīng)的改為if(i0<25)。

仿真的波形如下圖(fir濾波器的輸入輸出信號(hào)):

由此可見FIR對(duì)帶外信號(hào)起到衰減的作用。

部分代碼:

//Date :2012-5-27

//Description : 8 階FIR濾波器 ,通帶2MH,阻帶8MHz ,帶外衰減80dB,通帶波動(dòng)1dB

//Uesedfor

//Taobao :

//E-mail :2352517093@qq.com

//==========================================================================

`timescale 1 ns / 1 ns

module fir_filter

(

i_fpga_clk ,

i_rst_n ,

i_filter_in,

o_filter_out

);

input i_fpga_clk ; //25MHz

input i_rst_n ;

input signed [7:0] i_filter_in ; //數(shù)據(jù)速率25Mh

output reg signed [7:0] o_filter_out; //濾波輸出

//==============================================================

//8階濾波器系數(shù),共9個(gè)系數(shù),系數(shù)對(duì)稱

//==============================================================

wire signed[15:0] coeff1 = 16'd239 ;

wire signed[15:0] coeff2 = 16'd1507;

wire signed[15:0] coeff3 = 16'd4397;

wire signed[15:0] coeff4 = 16'd7880;

wire signed[15:0] coeff5 = 16'd9493;

//===============================================================

//延時(shí)鏈

//===============================================================

reg signed [7:0] delay_pipeline1 ;

reg signed [7:0] delay_pipeline2 ;

reg signed [7:0] delay_pipeline3 ;

reg signed [7:0] delay_pipeline4 ;

reg signed [7:0] delay_pipeline5 ;

reg signed [7:0] delay_pipeline6 ;

reg signed [7:0] delay_pipeline7 ;

reg signed [7:0] delay_pipeline8 ;

always@(posedge i_fpga_clk or negedge i_rst_n)

if(!i_rst_n)

begin

delay_pipeline1 <= 8'b0 ;

delay_pipeline2 <= 8'b0 ;

delay_pipeline3 <= 8'b0 ;

delay_pipeline4 <= 8'b0 ;

delay_pipeline5 <= 8'b0 ;

delay_pipeline6 <= 8'b0 ;

delay_pipeline7 <= 8'b0 ;

delay_pipeline8 <= 8'b0 ;

end

else

begin

delay_pipeline1 <= i_filter_in ? ? ;

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605315 -

matlab

+關(guān)注

關(guān)注

185文章

2980瀏覽量

230837 -

濾波器

+關(guān)注

關(guān)注

161文章

7859瀏覽量

178726

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

matlab與FPGA數(shù)字信號(hào)處理系列 Verilog 實(shí)現(xiàn)并行 FIR 濾波器

基于matlab FPGA verilog的FIR濾波器設(shè)計(jì)

并行FIR濾波器Verilog設(shè)計(jì)

基于MATLAB和Quartus II 的FIR濾波器設(shè)計(jì)與

基于MATLAB與QUARTUS II的FIR濾波器設(shè)計(jì)與驗(yàn)

用MATLAB設(shè)計(jì)FIR濾波器的方法

基于MATLAB與QUARTUS II的FIR濾波器設(shè)計(jì)與驗(yàn)

基于MATLAB及FPGA的FIR低通濾波器的設(shè)計(jì)

基于MATLAB與FPGA的FIR濾波器設(shè)計(jì)與仿真

基于Matlab/Simulink的FIR數(shù)字濾波器的設(shè)計(jì)與實(shí)現(xiàn)

基于matlab和fpga的FIR濾波器設(shè)計(jì)

基于MATLAB與QUARTUS+II的FIR濾波器設(shè)計(jì)與驗(yàn)證

FIR濾波器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

基于matlab FPGA verilog的FIR濾波器設(shè)計(jì)

基于matlab FPGA verilog的FIR濾波器設(shè)計(jì)

評(píng)論