在做這個(gè)項(xiàng)目的過(guò)程中,IC君一直在反思,工作7年以來(lái),為什么絕大部分的項(xiàng)目都很忙?每到tapeout的時(shí)候總是手忙腳亂?為什么有些項(xiàng)目出來(lái)的結(jié)果會(huì)失敗?

《窮查理寶典》

巴菲特的搭檔查理芒格認(rèn)為凡事要反過(guò)來(lái)想:

“如果要明白人生如何得到幸福,首先是研究人生如何才能變得痛苦;要研究企業(yè)如何做強(qiáng)做大,首先研究企業(yè)是如何衰敗的。”要想做一個(gè)成功的項(xiàng)目,首先是研究如何做一個(gè)“失敗”的IC項(xiàng)目。

這兒定義的失敗,是指項(xiàng)目執(zhí)行的過(guò)程很混亂,大家做得辛苦,但是最后出來(lái)芯片的bug卻很多,甚至完全不能工作。

至于芯片生產(chǎn)出來(lái)之后,市場(chǎng)定位準(zhǔn)不準(zhǔn)確、好不好賣或者賺不賺錢不在我們的討論之列。

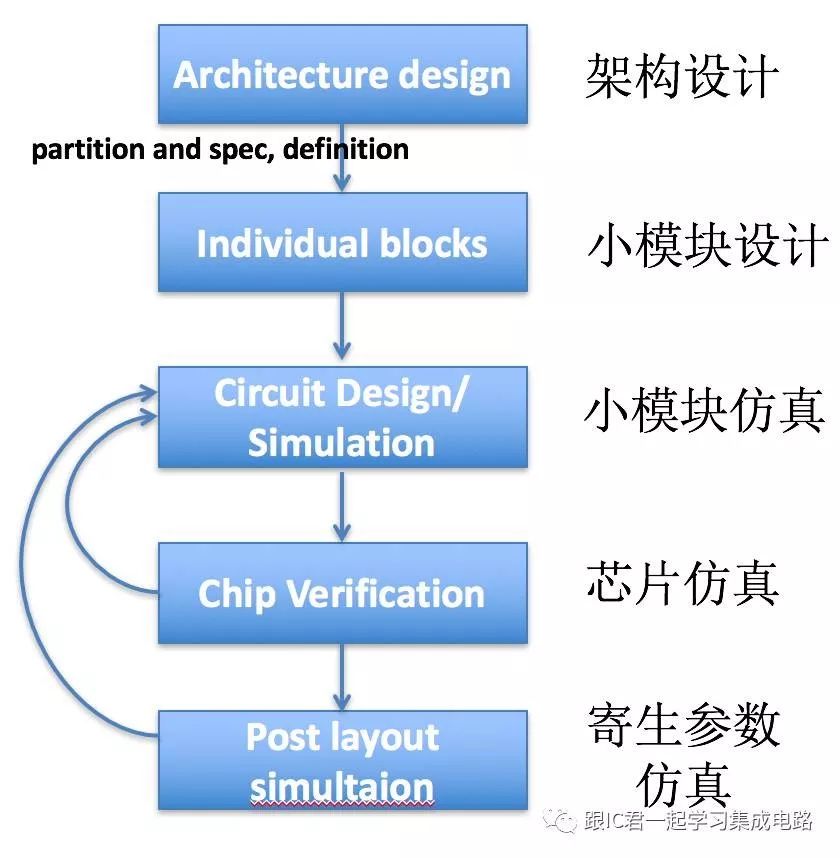

我們IC的項(xiàng)目流程往往如下所示:

這個(gè)圖的步驟分類比較粗獷,具體各部分的功能以前的文章也說(shuō)過(guò)新入職IC工程師必備技能——數(shù)模混合篇。比較細(xì)致的流程可以參考之前的文章一個(gè)前端數(shù)字IC工程師的一天。下面就從這幾個(gè)步驟探討一下如何做一個(gè)“失敗”的項(xiàng)目。

1

架構(gòu)設(shè)計(jì)決定了一個(gè)芯片的功能和設(shè)計(jì)劃分,是最重要的一環(huán),它決定了我們以后的努力方向。如果努力的方向錯(cuò)了,做得越多,錯(cuò)的越多!

想把項(xiàng)目搞失敗,這一步最容易。

比如項(xiàng)目執(zhí)行的過(guò)程中,架構(gòu)不停地變換,但是tapeout的日期沒(méi)變:

-

本來(lái)想做高速芯片,后面突然想把功耗做到最低;

-

起初想做一顆很小的芯片,后面變成一顆很大的芯片,期間添加了無(wú)數(shù)的功能。tapeout前添加的功能最容易出問(wèn)題哦!

-

某個(gè)中等模塊的風(fēng)險(xiǎn)一開(kāi)始沒(méi)有評(píng)估充分,做到后面發(fā)現(xiàn)冒出來(lái)的bug越來(lái)越多。如果徹底解決需要改動(dòng)很多block,最后只能修修補(bǔ)補(bǔ);

-

對(duì)spec的理解發(fā)生錯(cuò)誤,項(xiàng)目執(zhí)行的中后期發(fā)現(xiàn)了這個(gè)問(wèn)題,為了實(shí)現(xiàn)正確的spec需要改動(dòng)很多電路;

-

沒(méi)有正確評(píng)估封裝的可行性,比如做到后面突然發(fā)現(xiàn)8SOP封裝包不進(jìn)去,pad位置需要大改,之前做的很多評(píng)估工作完全白做。

架構(gòu)設(shè)計(jì)主要是在項(xiàng)目leader主導(dǎo)下完成,當(dāng)然有些東西也不完全由leader決定,老板很多時(shí)候也會(huì)參與其中。有時(shí)候架構(gòu)的變化是市場(chǎng)導(dǎo)致的,果斷的改架構(gòu)可能對(duì)公司而言是一個(gè)正確的決定。比如某段時(shí)間穿戴式產(chǎn)品的興起,低功耗突然變成大家迫切需要的特性,對(duì)于speed不太那么care。

架構(gòu)的改變對(duì)于IC工程師而言,只能接受并做出更多仿真來(lái)確保架構(gòu)的改動(dòng)是沒(méi)問(wèn)題的。不管是基于何種原因,頻繁的改動(dòng)架構(gòu)是最容易導(dǎo)致項(xiàng)目失敗的!

2

小模塊的設(shè)計(jì)和仿真驗(yàn)證就是廣大的IC工程師的工作內(nèi)容,做好自己負(fù)責(zé)的部分。對(duì)于一個(gè)失敗的項(xiàng)目而言,這一步的危害性相對(duì)于架構(gòu)設(shè)計(jì)小很多。如果你想把項(xiàng)目做失敗,可以通過(guò)以下方法來(lái)實(shí)現(xiàn):

-

負(fù)責(zé)的模塊經(jīng)過(guò)自己評(píng)估之后,發(fā)現(xiàn)工作量巨大或者難度巨高,但是又希望完全通過(guò)自己的努力去完成它,默默的做了幾個(gè)月而沒(méi)有及時(shí)向leader highlight這些問(wèn)題;

-

在沒(méi)有搞清楚電路功能的情況下,隨意修改繼承項(xiàng)目的電路。以前的項(xiàng)目怎么做得這么笨啊,不行我要改改它,讓它的gate數(shù)目少一點(diǎn),面積更小prefect!

-

實(shí)現(xiàn)功能的時(shí)候沒(méi)有想清楚各種意外case,只是簡(jiǎn)單的實(shí)現(xiàn)spec的功能;

-

時(shí)序檢查的時(shí)候沒(méi)有留下足夠的margin,在post layout仿真的時(shí)候很容易出錯(cuò);

-

有些模塊可能要跑所有的工藝角,實(shí)際做的時(shí)候只跑了一個(gè)TT 工藝,后續(xù)芯片級(jí)驗(yàn)證的時(shí)候也不可能跑所有的工藝,有可能芯片的工藝稍微飄一飄就不能正常工作了。比如你做了一個(gè)RC的delay在TT工藝下是5ns,但是工藝飄一飄就到15ns了,有可能電路就fail了;

-

設(shè)計(jì)沒(méi)有冗余,自認(rèn)為將面積做到了最小。tapeout前期修改電路的時(shí)候根本沒(méi)有g(shù)ate讓你用。這也是IC君容易犯的錯(cuò)誤。

-

不遵守一些既定的設(shè)計(jì)規(guī)則。比如在電路綜合的時(shí)候,不希望出現(xiàn)latch,必須遵守特定的RTL代碼寫法。

3

芯片仿真就是把所有模塊都包含進(jìn)來(lái)的仿真驗(yàn)證。通常整合之后,會(huì)發(fā)現(xiàn)很多小模塊設(shè)計(jì)時(shí)沒(méi)考慮的問(wèn)題。這一步通常會(huì)有多位工程師參與,所以前一步的問(wèn)題很多在這邊能cover掉,項(xiàng)目想要失敗似乎也沒(méi)那么容易。

-

仿真環(huán)境和電路實(shí)際工作環(huán)境不match,不帶dspf沒(méi)有任何寄生效應(yīng),看起來(lái)工作的棒棒的,tapeout出來(lái)之后fail了;

-

行為模型編寫錯(cuò)誤,你看到的仿真行為根本和實(shí)際芯片不一致,驗(yàn)證結(jié)果很完美,實(shí)際結(jié)果沒(méi)法看。這個(gè)危害真的挺大的;

-

由于芯片仿真也是由不同的人負(fù)責(zé)的,所以如果負(fù)責(zé)人沒(méi)有按照既定的flow 驗(yàn)證一些該check的東西,遺漏了很多情況,就加大了失敗的概率;

-

負(fù)責(zé)check的人不夠資深,即使看到錯(cuò)誤的仿真結(jié)果仍然發(fā)現(xiàn)不了問(wèn)題;

-

仿真時(shí)間特別長(zhǎng),沒(méi)有使用提高仿真速度的方法,做一次仿真需要很長(zhǎng)時(shí)間,等你仿真結(jié)果出來(lái)黃花菜都涼了。如何避免這個(gè)問(wèn)題,可以參考我們之前的文章如何減少IC設(shè)計(jì)和驗(yàn)證的仿真時(shí)間。

4

寄生參數(shù)仿真(layout后仿真)就是考慮實(shí)際的layout提取寄生參數(shù)后,進(jìn)行的仿真。

這一步通常跟做第二步的是同一批的人,如果項(xiàng)目要做失敗,可能是以下原因?qū)е碌模?/p>

-

根本就沒(méi)有做寄生參數(shù)的仿真,前仿的時(shí)候電路的節(jié)點(diǎn)根本沒(méi)有寄生的RC,仿真結(jié)果看起來(lái)特別好,但是layout有可能走了很長(zhǎng)的金屬線,有可能setup時(shí)間就違例了;

-

對(duì)抽取寄生參數(shù)的工具使用不當(dāng):比如使用calibre的工具去抽寄生參數(shù),有很多option需要設(shè)置。有可能寄生結(jié)果的提取比實(shí)際layout過(guò)重或者過(guò)輕,導(dǎo)致仿真結(jié)果的不正確;

-

沒(méi)有做layout檢查,有些模塊需要特殊的layout比如電流鏡、bandgap、放大器等等;還有一些特殊的走線(特殊線寬),也需要做layout檢查,以確保tapeout的版本跟你仿真的版本一致。

5

其它原因主要是指一些跟工廠相關(guān)的問(wèn)題,以前的文章也提到過(guò)一部分聊一聊tapeout失敗的事。這些問(wèn)題通常都很嚴(yán)重,一招致命的類型:

-

mask給你出錯(cuò)了,少出了一層或者拿成前一版的;

-

某些器件用得好好的,突然建議你不要用了;

-

工廠產(chǎn)能不夠,需要換工藝或者換工廠。

-

和PAD直接連接的電路不考慮ESD的問(wèn)題

-

每家公司可能都有tapeout的checklist,tapeout前沒(méi)有check這些規(guī)則,很可能就會(huì)fail。

我只想知道將來(lái)我會(huì)死在什么地方,這樣我就不去那兒了。

由于個(gè)人知識(shí)有限,上面列舉了一些項(xiàng)目失敗的原因,大家還可以在微信文章或者知乎文章留言,IC君會(huì)對(duì)文章進(jìn)行修改和補(bǔ)充。

最后希望大家在項(xiàng)目執(zhí)行過(guò)程中不要犯這些錯(cuò)誤,輕松愉快地流片成功!

-

集成電路

+關(guān)注

關(guān)注

5391文章

11617瀏覽量

362847

原文標(biāo)題:如何做一個(gè)”失敗”的IC項(xiàng)目

文章出處:【微信號(hào):icstudy,微信公眾號(hào):跟IC君一起學(xué)習(xí)集成電路】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

探究為什么有些項(xiàng)目出來(lái)結(jié)果會(huì)失敗?

探究為什么有些項(xiàng)目出來(lái)結(jié)果會(huì)失敗?

評(píng)論