概述

LTC 6957-1 / LTC6957-2 / LTC6957-3 / LTC6957-4 是一個非常低相位噪聲、雙輸出 AC 信號緩沖器 / 驅(qū)動器 / 邏輯電平轉(zhuǎn)換器系列。輸入信號可以是一個正弦波或任何邏輯電平 (≤ 2V P-P )。該系列包括以下 4 個具有不同輸出邏輯信號類型的成員:

LTC6957-1:LVPECL 邏輯輸出

LTC6957-2:LVDS 邏輯輸出

LTC6957-3:CMOS 邏輯,同相輸出

LTC6957-4:CMOS 邏輯,互補(bǔ)型輸出

數(shù)據(jù)表:*附件:LTC6957低相位噪聲、雙輸出緩沖器 驅(qū)動器 邏輯轉(zhuǎn)換器技術(shù)手冊.pdf

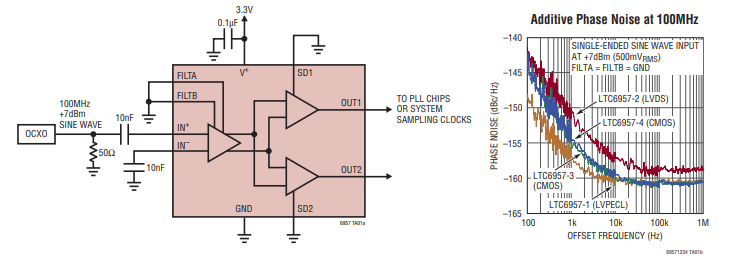

LTC6957 將以極低的附加噪聲進(jìn)行任何邏輯信號的緩沖和分配,不過,在把正弦波信號轉(zhuǎn)換為邏輯電平方面,該器件相比于同類產(chǎn)品確實更勝一籌。初始放大級具有可選的低通濾波,以較大限度地抑制噪聲,同時仍然對信號實施放大以增加其擺率。當(dāng)采用緩慢擺率的輸入信號 (例如:一個典型的 10MHz 正弦波系統(tǒng)基準(zhǔn)) 時,該輸入級濾波 / 噪聲限制特別有助于提供相位噪聲盡可能低的信號。

應(yīng)用

- 系統(tǒng)基準(zhǔn)頻率分配

- 高速 ADC、DAC、DDS 時鐘驅(qū)動器

- 軍事和安全無線電

- 低噪聲定時觸發(fā)器

- 寬帶無線收發(fā)器

- 高速數(shù)據(jù)采集

- 醫(yī)學(xué)成像

- 測試和測量

特性

- 低相位噪聲緩沖器 / 驅(qū)動器

- 正弦波信號至邏輯電平的優(yōu)化轉(zhuǎn)換

- 可提供 3 種邏輯輸出類型

- LVPECL

- LVDS

- CMOS

- 附加的抖動:45fs

RMS(LTC6957-1) - 頻率范圍高達(dá) 300MHz

- 3.15V 至 3.45V 電源操作

- 低擺率 3ps (典型值)

- 全面規(guī)格在 –40°C 至 125°C

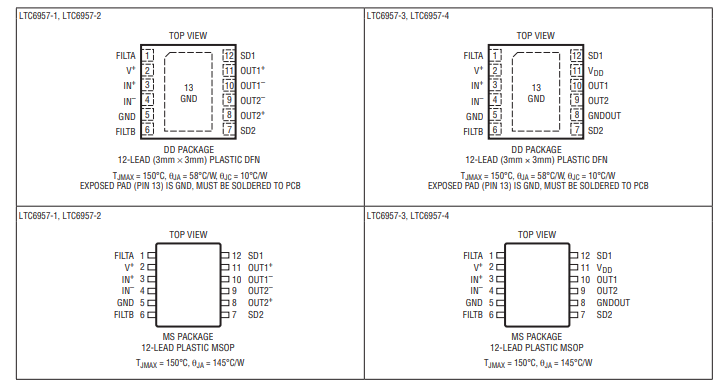

- 12 引腳 MSOP 封裝和 3mm x 3mm DFN 封裝

典型應(yīng)用

引腳配置

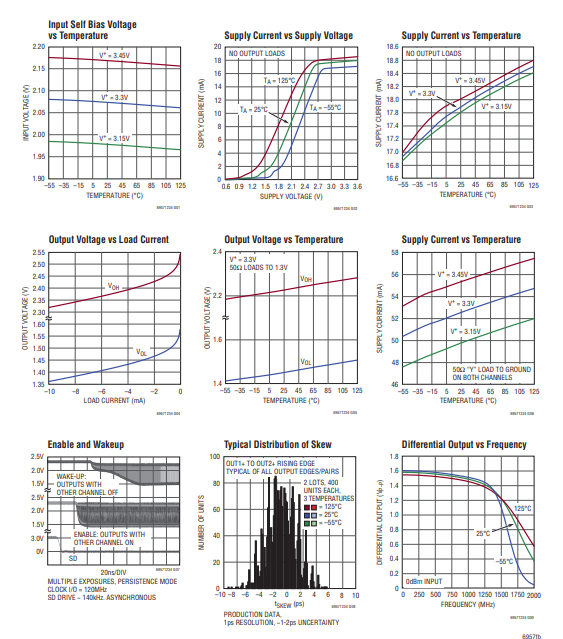

典型性能特征

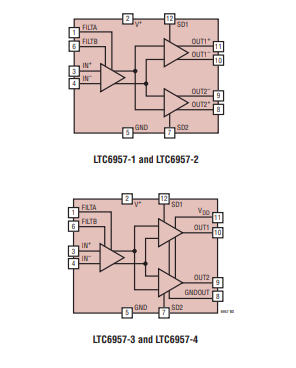

框圖

應(yīng)用信息

一般注意事項

LTC6957 - 1/LTC6957 - 2/LTC6957 - 3/LTC6957 - 4 是低噪聲雙輸出時鐘緩沖器,專為要求嚴(yán)苛的低相位噪聲應(yīng)用而設(shè)計。正確使用時,它們可以在其他解決方案會顯著降低相位噪聲的情況下保持相位噪聲性能。它們也可用作邏輯轉(zhuǎn)換器。

然而,沒有緩沖器設(shè)備能夠消除或減少輸入信號中存在的相位噪聲。與大多數(shù)低相位噪聲電路一樣,LTC6957 - 1/LTC6957 - 2/LTC6957 - 3/LTC6957 - 4 的不當(dāng)應(yīng)用可能會由于多種機(jī)制導(dǎo)致相位噪聲性能下降。以下信息有望幫助設(shè)計人員避免出現(xiàn)這種情況。

LTC6957 旨在與用于驅(qū)動模數(shù)轉(zhuǎn)換器 (ADC) 或混頻器輸入的高性能時鐘信號配合使用。此類時鐘信號不應(yīng)被視為數(shù)字信號。理想數(shù)字邏輯的優(yōu)勢在于,在出現(xiàn)任何有害影響之前,其電壓和定時方面都存在噪聲裕量。相比之下,高性能時鐘信號沒有誤差噪聲裕量。在系統(tǒng)性能下降之前的定時方面也是如此。建議用戶在設(shè)計LTC6957之前、期間和之后的整個時鐘信號鏈時牢記這一區(qū)別。

輸入接口

LTC6957的所有版本的輸入級都是相同的,其設(shè)計目的是實現(xiàn)低噪聲,并便于與正弦波和小幅度信號接口。其他邏輯類型可以輕松接口,因為它們對噪聲抑制的挑戰(zhàn)較小。

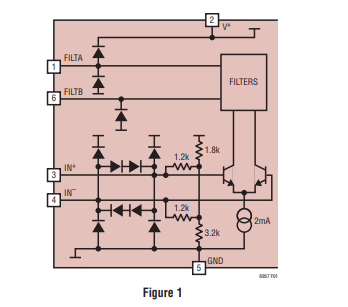

圖1顯示了LTC6957輸入級的簡化示意圖。這些二極管用于在靜電放電(ESD)事件期間提供保護(hù),并防止低噪聲NPN器件因輸入過壓而損壞。

偏置電阻將輸入級偏置在最佳直流電平,但如果不增加噪聲,它們不能懸空。因此,為實現(xiàn)低噪聲,務(wù)必在未使用的輸入上連接一個交流阻抗的接地回路。

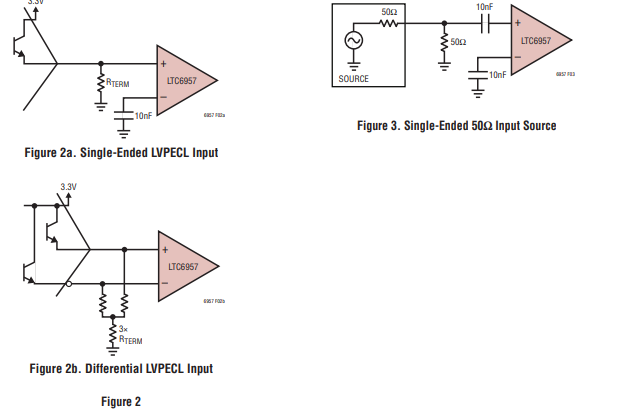

圖2a展示了單端LVPECL邏輯與LTC6957的接口方式,而圖2b則展示了如何用差分LVPECL信號驅(qū)動LTC6957。圖中所示的電容為10nF,且價格可能較高,最好采用小型表面貼裝(SMT)封裝。對于100MHz以上的應(yīng)用,可能需要使用較低容值的電容,以避免在圖2a中出現(xiàn)諧振,因為即使電容僅連接在直流輸入上,也可能會增加噪聲。此說明適用于整個數(shù)據(jù)手冊中連接到輸入端的所有電容。

在圖2a中,R_{TERM}的實現(xiàn)方式由用戶決定,目的是對傳輸線進(jìn)行端接。如果將其連接到V_T電壓,并通過大電容旁路接地,那么在反相LTC6957輸入端所示的10nF接地電容就是合適的連接方式。然而,如果端接方式是主動產(chǎn)生V_T電壓,那么將反相輸入端的電容連接到V_T而非接地,可能會實現(xiàn)更低的噪聲。

在圖2b中,LTC6957的兩個輸入端都被驅(qū)動,這樣增大了差分輸入信號幅度,并且將來自任何共模源(如V_T)的噪聲影響降至最低,從而改善了相位噪聲。

可以使用多種端接技術(shù),只要兩端采用相同的端接方式,配置就不會有太大差異。在圖2b中,電阻端接采用Y形配置,在公共點產(chǎn)生一個無源V_T。大多數(shù)3.3V LVPECL器件具有差分輸出,可以用三個50Ω電阻進(jìn)行端接,如圖所示。

圖3展示了一個50Ω射頻信號源與LTC6957的接口。對于純正弦波輸入,圖3中的配置可處理高達(dá)10dBm(最大值)的輸入信號。一個寬帶50Ω匹配網(wǎng)絡(luò)對于大多數(shù)應(yīng)用來說應(yīng)該就足夠了,不過對于小幅度輸入信號,窄帶電抗匹配網(wǎng)絡(luò)可能會在性能上帶來一些提升。

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8859瀏覽量

149777 -

驅(qū)動器

+關(guān)注

關(guān)注

54文章

8460瀏覽量

148338 -

緩沖器

+關(guān)注

關(guān)注

6文章

2023瀏覽量

46214

發(fā)布評論請先 登錄

相關(guān)推薦

凌力爾特推出DC至300MHz的雙輸出緩沖器/驅(qū)動器/邏輯轉(zhuǎn)換器LTC6957

采用LTC6954-4低相位噪聲三路輸出時鐘分配器/驅(qū)動器的演示電路DC1954A-D

LTC6957的典型應(yīng)用是一系列極低相位噪聲

LTC6957 低相位噪聲、雙輸出緩沖器 / 驅(qū)動器 / 邏輯轉(zhuǎn)換器

LTC6957-1/LTC6957-2/LTC6957-3/LTC6957-4:低相位噪聲、雙輸出緩沖器/驅(qū)動器/邏輯轉(zhuǎn)換器數(shù)據(jù)表

LTC6954:低相位噪聲、三輸出時鐘分布分頻器/驅(qū)動器數(shù)據(jù)表

LTC6417:1.6 GHz低噪聲高線性度差分緩沖器/16位ADC驅(qū)動器,帶快速鉗位數(shù)據(jù)表

低相位噪聲、雙輸出AC信號緩沖器/驅(qū)動器/邏輯電平轉(zhuǎn)換器系列

具有開漏輸出的雙緩沖器/驅(qū)動器數(shù)據(jù)表

CDC3RL02低相位噪聲雙通道時鐘扇出緩沖器數(shù)據(jù)表

評論