在電子元件領域,上拉電阻與下拉電阻并非獨立的物理實體,而是依據(jù)電阻在不同電路場景中的功能定義。它們的本質仍是普通電阻,但在電路設計中扮演著關鍵角色。

上拉電阻和下拉電阻

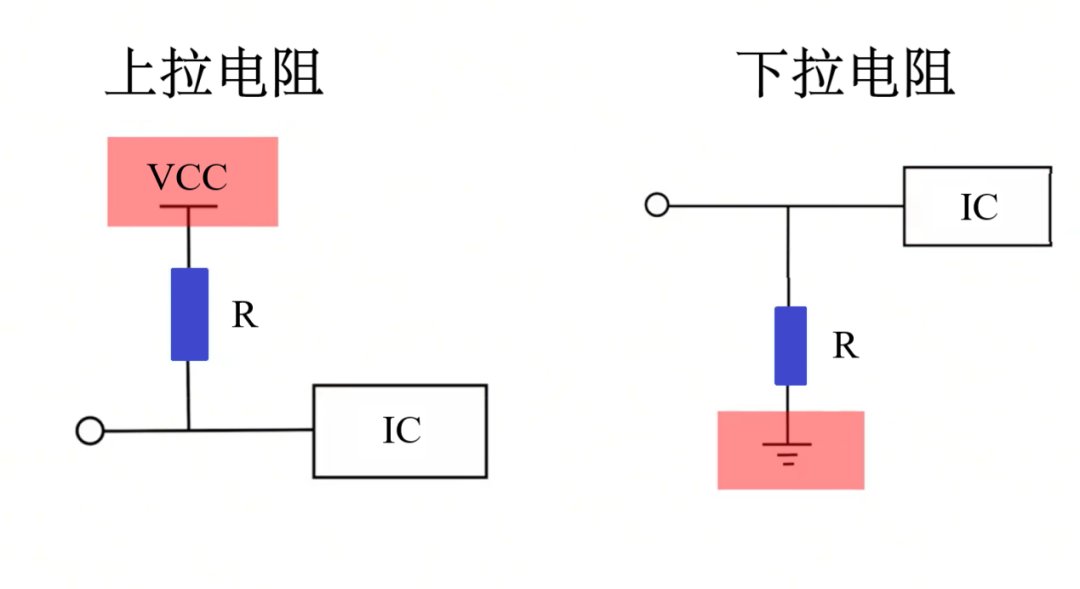

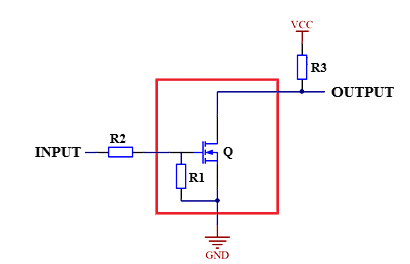

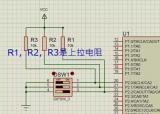

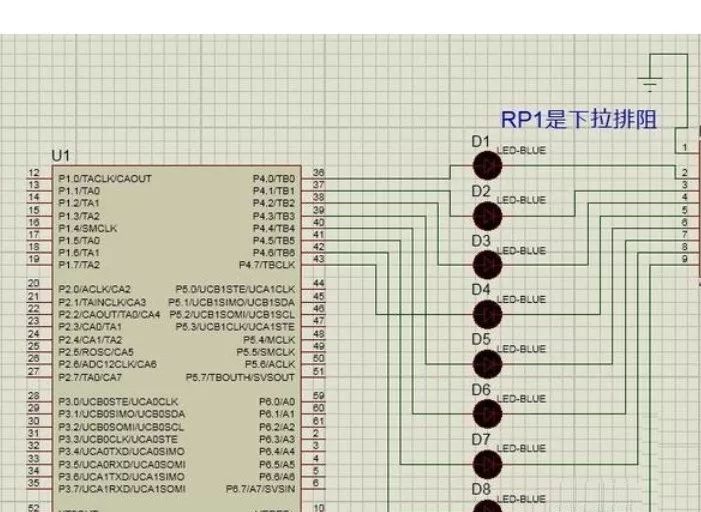

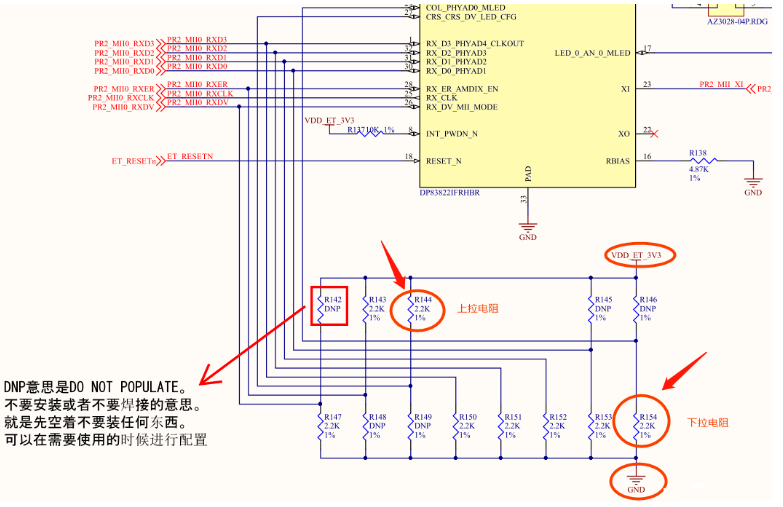

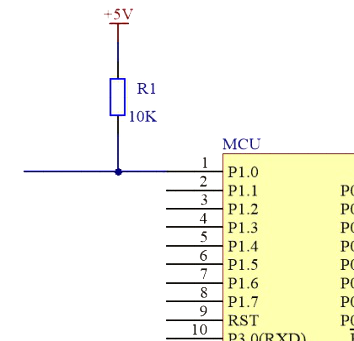

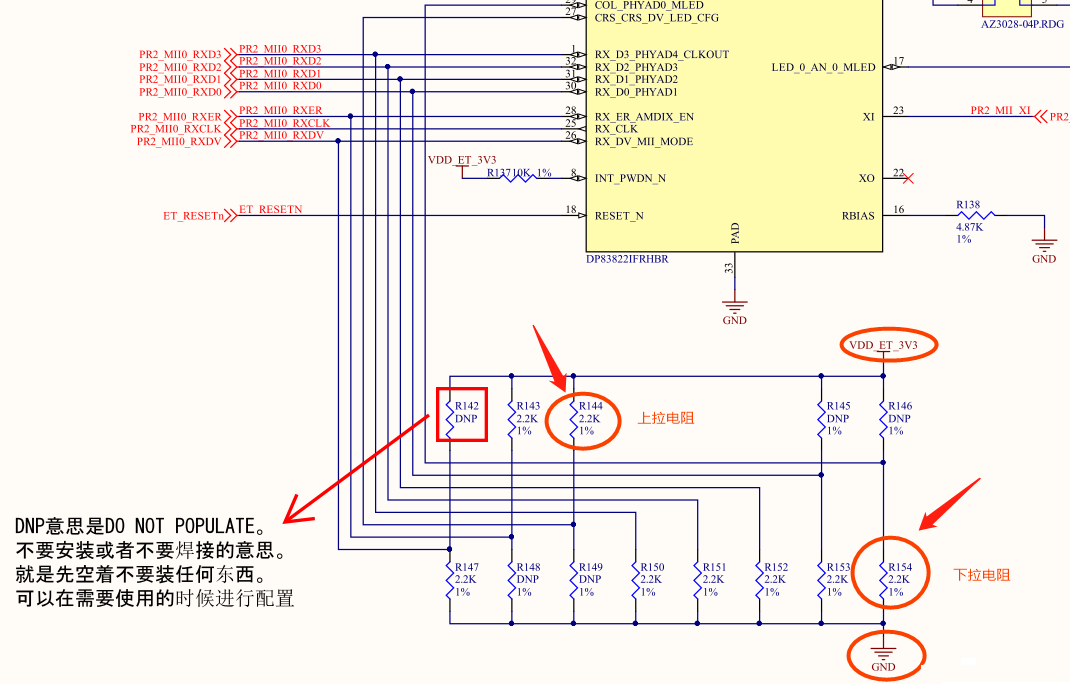

上拉電阻和下拉電阻常用于偏置數(shù)字門的輸入,用以防止它們在沒有輸入時隨機浮動。當你使用它們時,你會得到一個穩(wěn)定的“高”或“低”狀態(tài)。相反,如果沒有發(fā)生這種情況,則引腳上沒有連接,程序讀取高阻抗的“浮動”狀態(tài)。上拉電阻:通過電阻將不確定的信號連接到VCC電源,并將其固定在高電平。功能:向上拉動將電流注入器件;灌電流;當帶有上拉電阻器的IO端口設置為輸入狀態(tài)時,其正常狀態(tài)為高電平。下拉電阻:通過電阻將某個信號線連接到固定的低電平GND,以將其空閑狀態(tài)保持在低電平。功能:下拉是從器件輸出電源;拉電流。當帶有下拉電阻的IO端口設置為輸入狀態(tài)時,其正常狀態(tài)為低,如下圖。

上拉電阻和下拉電阻二者共同的作用是:避免電壓的“懸浮”,造成電路的不穩(wěn)定。

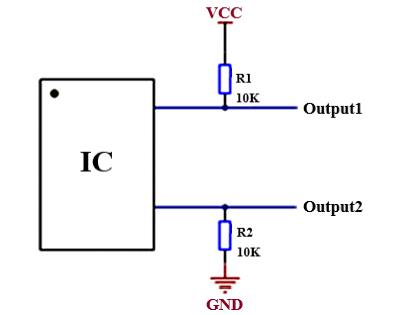

如下圖所示,R1為上拉電阻,R2為下拉電阻。當R1的電阻在數(shù)百K時,它可以向信號線提供非常小的負載電流,負載電容器的充電相對較慢。在這一點上,電阻被稱為弱上拉。

同樣,如果下拉電阻很大,下拉速度相對較慢,此時的電阻稱為弱下拉。如果上拉和下拉電平可以為芯片提供大電流,則此時的電阻稱為強上拉或強下拉。

上拉電阻的作用

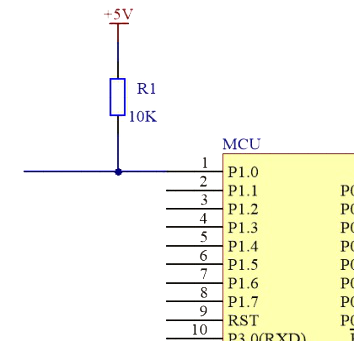

1. 提高輸出的高電平:當TTL電路驅動COMS電路時,當TTL電路的輸出電平低于COMS電路的最低高電平(通常為3.5V)時,必須在TTL的輸出端連接上拉電阻,以提高輸出值的輸出電平。2. OC(集電極開路,TTL)門電路必須加上拉電阻,才能使用,因為管子沒有電源就不能輸出高電平。3. 為了提高輸出引腳的驅動能力,一些MCU通常在引腳上使用上拉電阻。4. 在COMS芯片上,為了避免靜電造成的損壞,不用的管腳不能懸空,通常,連接上拉電阻以降低輸入阻抗并提供放電路徑。同時,當引腳懸空時,相對容易接受外部電磁干擾(MOS器件具有高輸入阻抗,非常容易受到外部干擾)。5. 芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6. 提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。7. 長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效抑制反射波干擾。

上拉電阻和下拉電阻在OC/OD門的應用

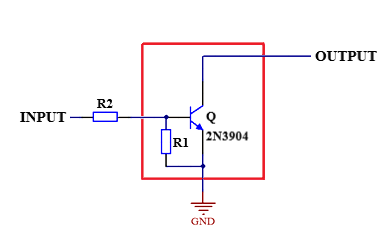

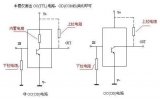

所謂OC門就是Open Collector,集電極開路,如下圖所示:

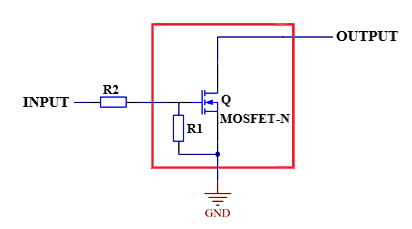

所謂OD門就是Open Drain,漏極開路,如下圖所示:

因此,OC門是針對三極管來設計的,而OD門是為MOS管設計的。從OC門和OD電路可以看出,如果輸入電平為H,則輸出電平為L。如果輸入電平為L,則輸出電平處于不穩(wěn)定狀態(tài),即處于易受外部干擾影響的高阻抗狀態(tài)。OC門和OD門不具備輸出高電平的能力。此時,如果在集電極或漏極上增加上拉電阻,如下圖所示:

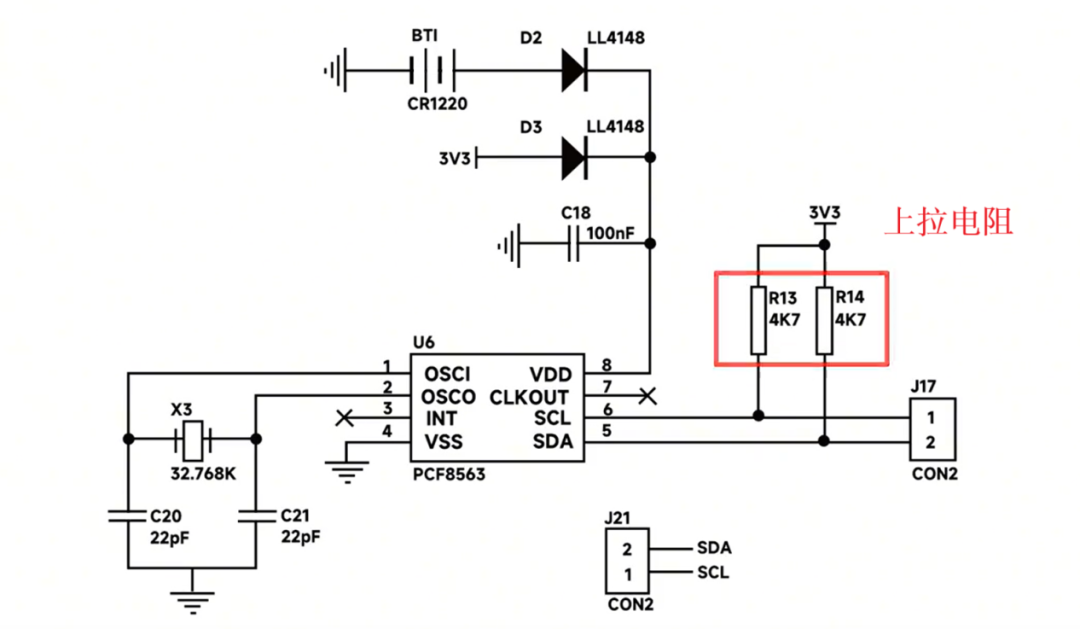

如果輸入處于高電平,則輸出保持低電平;如果輸出低,則輸出電平為VCC。此時,OC門和OD門具有輸出高電平和低電平的功能,這些電平被固定的鉗位到VCC或GND。上拉電阻阻值選擇原則:1. 從節(jié)約功耗及芯片的灌電流能力考慮,電阻應當足夠大;電阻大,電流小。2. 從確保足夠的驅動電流考慮,電阻應當足夠小;電阻小,電流大。3. 對于高速電路,過大的上拉電阻可能邊沿變平緩。綜合考慮以上三點,通常在1k到10k之間選取。對下拉電阻也有類似道理。4. 低功耗狀態(tài)上拉下拉使用注意;帶上拉或者下拉的IO口,在低功耗狀態(tài),或者配置使用的常態(tài)時,應根據(jù)IO口的狀態(tài)進行相關的設置。如果IO端口處理不當,功耗就會被偷偷竊取。通常,IO內(nèi)部或外部都有上拉和下拉電阻。例如,如果IO端口有一個10KΩ的上拉電阻,將引腳拉到3.3V,但當MCU切換到低功耗模式時,該IO端口被設置為低電平。根據(jù)歐姆定律,該引腳消耗3.3V÷10K=0.33mA電流。如果有四個或五個這樣的IO端口,則會損失幾毫安。因此,在實現(xiàn)低功耗之前,有必要逐一檢查每個IO端口的狀態(tài):? 如果此IO口帶上拉,請設置為高電平輸出或者高阻態(tài)輸入;? 如果此IO口帶下拉,請設置為低電平輸出或者高阻態(tài)輸入;? 總而言之,不要把電流浪費在產(chǎn)生熱量的功能上。IO口上拉與下拉電平與IC間的連接造成的相應功耗的損失。IO端口上下拉電阻的功耗相對明顯。不太明顯的因素:IO端口連接到外部IC時的功耗。如果IO端口具有內(nèi)置上拉,但連接到IO的IC引腳具有內(nèi)置下拉,則無論該引腳的輸出電平如何,都不可避免地會產(chǎn)生一定量的功耗。所以,如果你遇到這樣的情況,第一步是閱讀外圍IC的手冊,確定這個引腳的狀態(tài)并有一個清晰的認識;在使MCU進入睡眠狀態(tài)之前,請設置MCU IO端口的上/下模式和I/O狀態(tài),以確保不消耗電源。

上拉電阻和下拉電阻的選型

1. 從功耗消耗的角度

上拉電阻連接到電源,下拉電阻連接到GND。在選擇電阻時,有必要考慮電阻本身造成的損耗。例如,在按鈕電路中,10K的電阻可以滿足條件,20K的電阻也可以滿足條件。然而,當電阻設置為20k時,電阻消耗的能量較低。在需要待機的電路中,有必要嚴格控制上拉和下拉電阻的值。

2. 從驅動能力的角度

驅動能力的大小和提供的電流有關系。例如,在OC和OD門電路中,如果上拉電阻太大,當輸出為高時,它將無法為下一級提供大電流。

3. 從信號速率的角度

在I2C的總線上需要增加上拉電阻,如果上拉電阻太大,則會減慢信號從低電平轉換到高電平的時間,減慢上升沿并影響信號上升速率。

總結

根據(jù)上文,對于上拉電阻,需要使用至少比輸入引腳阻抗值小十倍的電阻器。對于工作電壓為5V的邏輯器件,典型的上拉電阻值應在1~5kΩ之間。另一方面,開關和電阻傳感器的典型上拉電阻值應在1~10kΩ之間。對于下拉電阻器,其電阻應始終大于邏輯電路的阻抗。否則,過大的電流將導致電壓下降太多,引腳上的輸入電壓將保持在恒定的邏輯低值(無論開關是打開還是關閉)。

-

上拉電阻

+關注

關注

5文章

365瀏覽量

30974 -

下拉電阻

+關注

關注

4文章

149瀏覽量

20754 -

GND

+關注

關注

2文章

541瀏覽量

39314

發(fā)布評論請先 登錄

相關推薦

評論