定義

SerDes是一種功能塊,用于對高速芯片間通信中使用的數字化數據進行序列化和反序列化。用于高性能計算(HPC)、人工智能(AI)、汽車、移動和物聯網(IoT)應用的現代片上系統(SoC)都實現了SerDes,這種SerDes能夠支持多種數據速率以及諸多標準,比如PCIExpress(PCIe)、MIPI、以太網、USB、USR/XSR。

SerDes的實現包括并行到串行(串行到并行)數據轉換、阻抗匹配電路和時鐘數據恢復功能。SerDes的主要作用是盡量減少I/O互連的數量。

為什么需要SerDes?

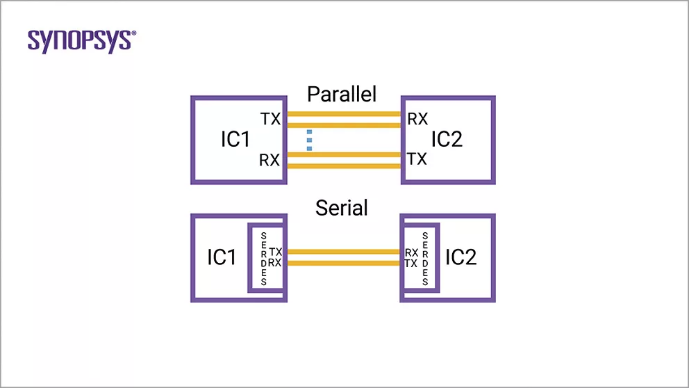

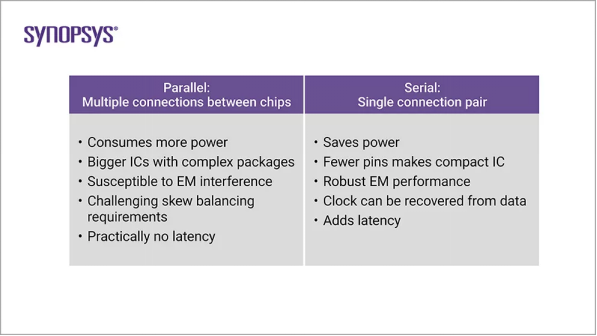

在多個IC中進行分布式數據處理,需要IC之間實現高速數據傳輸。并行和串行是芯片之間傳輸數據的兩種方式。并行數據傳輸需要IC之間建立多個連接,而串行數據傳輸僅需一對連接。

如上表所示,串行數據傳輸具有低功耗、強大的EMI性能和簡單的封裝設計等優點而成為理想的選擇。

SerDes應用

SerDes是芯片間互連系統物理層的最基本構建塊:

SerDes+物理編碼子層(PCS)=PHY(即物理層)

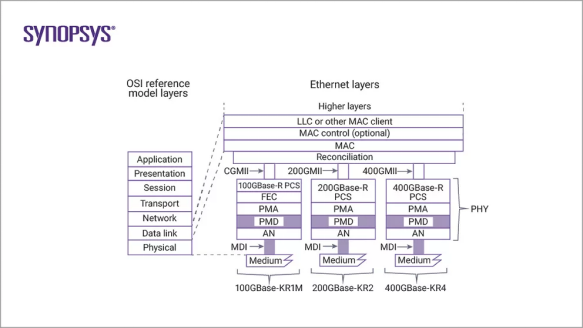

開放系統互連(OSI)模型將物理層(PHY)定義為負責數據傳輸和數據接收的抽象層。它是OSI模型中的最底層,其中還包括:

應用層

表示層

會話層

傳輸層

網絡層

數據鏈路層

不同的協議對PHY提出了不同的抽象劃分。例如,IEEE 802.3定義的100G PHY具有以下抽象層:

在這個模型中,SerDes將實現PMA/PMD子層,該子層是負責接口初始化、編碼解碼和時鐘校準的邏輯子塊。

新思科技提供哪些PHY IP解決方案?

新思科技是SoC設計領域中高質量、經過硅驗證的IP解決方案的領先供應商,其SoC設計目前被廣泛應用于眾多市場中的常見設備和系統,這些市場包括:

移動通訊

汽車

高性能計算(HPC)

人工智能(AI)

物聯網(IoT)

新思科技全面的高速SerDes IP產品組合在功率、性能和面積方面都具有領先優勢,使開發者能夠滿足超大規模數據中心、網絡和存儲應用的高性能計算SoC的高效連接要求。

224G以太網PHY IP和112G以太網PHY IP為高達800G/1.6T的高性能計算SoC實現真正的長距離信道

UALink PHY IP支持將AI加速器鏈路擴展至高達200Gbps

56G以太網PHY IP可滿足高達400G以太網應用的覆蓋范圍和性能要求

Die-to-Die PHY IP適用于UCIe和112G XSR

多協議PHY支持以太網、PCI Express、CCIX、CXL和更多的協議

PCI Express PHY IP可在先進的鰭式場效應晶體管(FinFET)制程工藝下,為高達128GT/s的片上系統(SoC)實現高性能、低功耗的連接

-

芯片

+關注

關注

459文章

51730瀏覽量

430996 -

以太網

+關注

關注

40文章

5508瀏覽量

173586 -

新思科技

+關注

關注

5文章

834瀏覽量

50694 -

SerDes

+關注

關注

6文章

205瀏覽量

35347

原文標題:【IC Glossary】什么是SerDes?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

GMII、SGMII和SerDes的差異總結

請問6678中的srio的serdes和以太網的serdes是共用還是各自有自己的serdes?

FPGA SERDES接口電路怎么實現?

請問7系列中的SERDES是否有最小延遲規范?

SerDes是怎么工作的

參考時鐘對SERDES性能的影響

SERDES的優勢 SERDES演變的看法

SerDes是怎么設計的?(一)

為什么我們需要SERDES?SERDES的優點有哪些?

評論