Zynq-7000配置

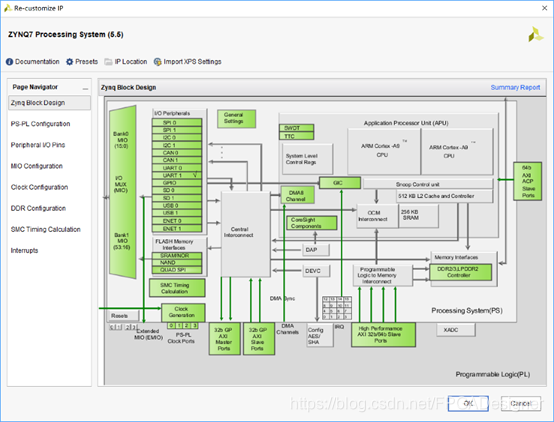

添加好ZYNQ7 Processing System IP核后,需要對(duì)其進(jìn)行配置,雙擊彈出如下窗口。綠色部分表示ZYNQ PS部分中可配置的項(xiàng)目,可以雙擊轉(zhuǎn)向相應(yīng)的設(shè)置界面,也可以直接在左邊的導(dǎo)航列表中選擇。

頂部有4個(gè)按鈕,Documentation查找與Zynq相關(guān)的文檔;Presets保存或?qū)胍恍╊A(yù)設(shè)配置;IP Location顯示了該IP所在路徑;Import XPS Settings導(dǎo)入由XPS工程產(chǎn)生的XML文件,該文件包含對(duì)Zynq處理器的配置。XPS是老版ISE使用的嵌入式開(kāi)發(fā)工具。

1. MIO與EMIO配置

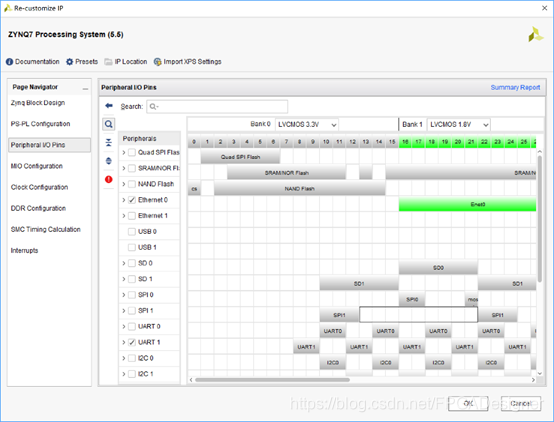

在Peripheral I/O Pins(如下圖)或MIO Configuration中可以查看和配置I/O管腳。Zynq-7000器件的PS部分有超過(guò)20種可選的外設(shè),設(shè)計(jì)者可以將這些外設(shè)直接與專(zhuān)用的復(fù)用I/O相連,通常稱(chēng)為MIO;也可以使用擴(kuò)展的復(fù)用I/O,通常稱(chēng)為EMIO。

設(shè)計(jì)者可以配置MIO的電平標(biāo)準(zhǔn),如果要使用某個(gè)外設(shè),選中復(fù)選框即可(會(huì)感覺(jué)和STM32 CubeMX軟件的使用有些相似)。PS的MIO劃分在Bank0(pin0-15)和Bank1(pin16-53)兩個(gè)電壓域內(nèi),每個(gè)bank內(nèi)的MIO可以獨(dú)立編程,支持1.8、2.5、3.3V的CMOS單端模式,1.8V的HSTL差分模式。我們都知道每個(gè)bank的電壓必須相同,但是不同管腳可以有不同的I/O標(biāo)準(zhǔn)。

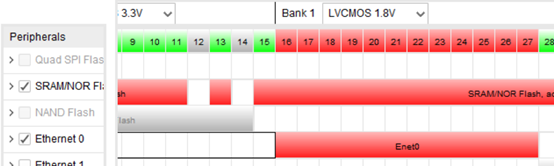

2. 閃存接口

Zynq-7000支持Quad-SPI Flash、SRAM/NOR Flash和NAND Flash三種閃存,配置時(shí)只能選擇其中一個(gè)。注意外設(shè)之間如果發(fā)生管腳沖突,會(huì)用紅色提示。如下圖SRAM和Enet0之間發(fā)生了沖突:

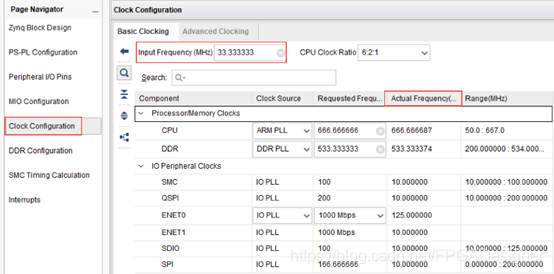

3. 時(shí)鐘配置

Clock Configuration中進(jìn)行Zynq-7000器件的時(shí)鐘配置。這里可以設(shè)置外設(shè)的時(shí)鐘,PS上外設(shè)的時(shí)鐘源可以由內(nèi)部PLL生成,也可以來(lái)自外部時(shí)鐘源。同一個(gè)PLL可能要產(chǎn)生多個(gè)頻率,導(dǎo)致得到的頻率不是完全準(zhǔn)確,在Actual Frequency列中查看能夠?qū)崿F(xiàn)的實(shí)際頻率。PS的輸入頻率范圍限制在30~60MHz之間,通常都會(huì)選擇33.33MHz,便于產(chǎn)生內(nèi)部所需的時(shí)鐘頻率。

4. DDR配置

Zynq-7000的內(nèi)存控制器支持DDR2、DDR3、DDR3L和LPDDR2,主要由三部分組成:

DDRI:DDR接口,AXI內(nèi)存端口接口。DDRI有4個(gè)64位同步AXI接口,可以同時(shí)為多個(gè)AXI主機(jī)提供服務(wù)。每個(gè)AXI接口都有一個(gè)專(zhuān)用FIFO。一個(gè)AXI端口專(zhuān)用于CPU和ACP的L2緩存;兩個(gè)端口專(zhuān)用于AXI_HP接口;AXI互聯(lián)網(wǎng)絡(luò)上的其它主機(jī)共享第四個(gè)端口。

DDRC:帶有事務(wù)調(diào)動(dòng)程序的核控制器,包含兩個(gè)內(nèi)容尋址存儲(chǔ)器(CAMs),用于執(zhí)行DDR數(shù)據(jù)服務(wù)調(diào)度,最大化DDR內(nèi)存的效率。同時(shí)包含一個(gè)低延遲的“fly-by”通道,允許在不通過(guò)CAM的情況下訪問(wèn)DDR內(nèi)存。

DDRP:帶有數(shù)字PHY(物理層)的控制器。PHY處理來(lái)自控制器的讀、寫(xiě)請(qǐng)求,在目標(biāo)DDR內(nèi)存的時(shí)序約束下轉(zhuǎn)換為特定信號(hào)。PHY利用來(lái)自控制器的信號(hào)產(chǎn)生內(nèi)部信號(hào),通過(guò)數(shù)字PHY連接到引腳。Zynq的DDR管腳在PCB上直接與DDR器件相連。

PS中DDR的大致工作流程為:根據(jù)請(qǐng)求等待時(shí)間、請(qǐng)求的緊急性、請(qǐng)求是否與前一個(gè)請(qǐng)求在同一頁(yè)內(nèi),DDRI對(duì)來(lái)自8個(gè)端口(4個(gè)讀、4個(gè)寫(xiě))的請(qǐng)求進(jìn)行仲裁,選擇一個(gè)請(qǐng)求通過(guò)一個(gè)讀寫(xiě)流接口傳遞到DDRC中,同時(shí)DDRP驅(qū)動(dòng)DDR的事務(wù)。

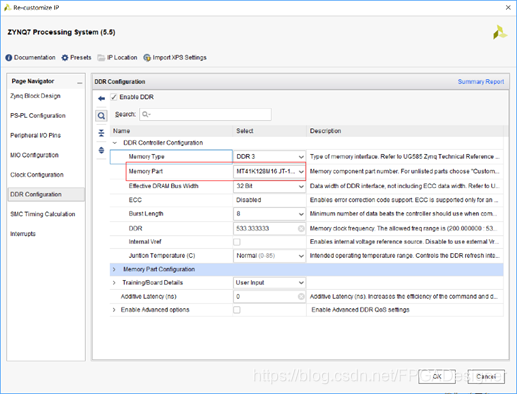

在DDR Configuration中完成DDR控制器的配置,DDR型號(hào)要與開(kāi)發(fā)板相符:

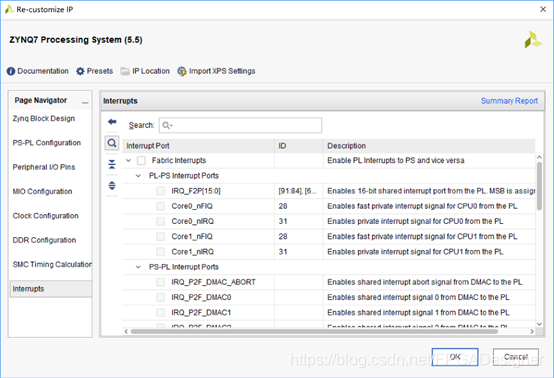

5. GIC中斷控制器

在Interrupts中對(duì)通用中斷控制器GIC(Generic Interrupt Controller)進(jìn)行配置。GIC用于管理從PS和PL發(fā)送到CPU中的終端。當(dāng)CPU接口接收一個(gè)新中斷時(shí),GIC以編程的方式啟用、禁用、屏蔽與優(yōu)先處理中斷源,并將其發(fā)送到選定的CPU。此外,GIC還支持安全擴(kuò)展,以實(shí)現(xiàn)安全感知系統(tǒng)。

目前,控制器基于ARMGIC架構(gòu)版本1.0。獨(dú)立總線通過(guò)避免互聯(lián)網(wǎng)絡(luò)中出現(xiàn)臨時(shí)阻塞訪問(wèn)寄存器,以實(shí)現(xiàn)快速讀、寫(xiě)響應(yīng)。中斷分配器集中所有中斷源,再將最高優(yōu)先級(jí)的中斷源分配到CPU。

當(dāng)把一個(gè)中斷定向到多個(gè)CPU時(shí),GIC可以確保每次只有一個(gè)CPU接收中斷。所有中斷源包含一個(gè)獨(dú)一無(wú)二的中斷ID號(hào),都有自己的可配置的優(yōu)先級(jí)和目標(biāo)CPU列表。

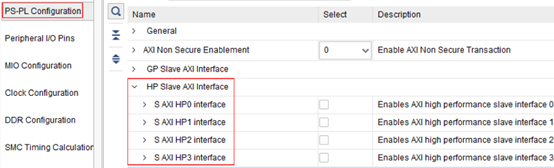

6. AXI_HP接口

4個(gè)AXI_HP接口為PL總線主程序提供了到DDR和OCM內(nèi)存的高帶寬數(shù)據(jù)通道,每個(gè)接口有兩個(gè)用于讀寫(xiě)通信的FIFO緩沖區(qū)。內(nèi)存互連的PL將高速AXI_HP端口布線到兩個(gè)DDR內(nèi)存端口或OCM。AXI_HP接口也可以用作AXI_FIFO接口,利用其緩沖能力。

在PS-PL Configuration中的HP Slave AXI Interface中可以啟用這些接口:

簡(jiǎn)而言之,這種接口為PL主機(jī)和PS內(nèi)存(DDR或OCM)之間提供了一種高吞吐量數(shù)據(jù)通道。

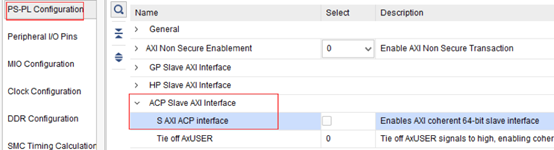

7. AXI ACP接口

ACP接口允許對(duì)PL主機(jī)進(jìn)行低延遲訪問(wèn),帶有可選的coherency和L1、L2緩存。從系統(tǒng)角度來(lái)看,ACP接口具有與APU CPU類(lèi)似的連通性,因此ACP可以直接在APU塊爭(zhēng)取資源。在PS-PL Configuration中的ACP Slave AXI Interface中可以啟用該接口:

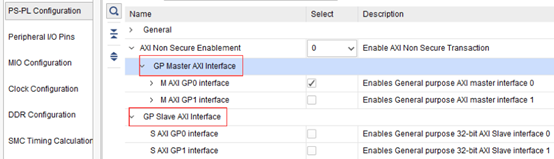

8. AXI GP接口

這種接口將主機(jī)與從機(jī)端口直接相連,不需要額外的FIFO緩沖。AXI_HP接口帶有精心設(shè)計(jì)的FIFO緩沖,以提高性能和吞吐量。與其不同,由于沒(méi)有FIFO,AXI_GP接口的性能受到主機(jī)和從機(jī)端口的限制。這種接口用于往往不會(huì)太關(guān)注性能的一般用途。在PS-PL Configuration中的GP Master/Slave AXI Interface中可以啟用該接口:

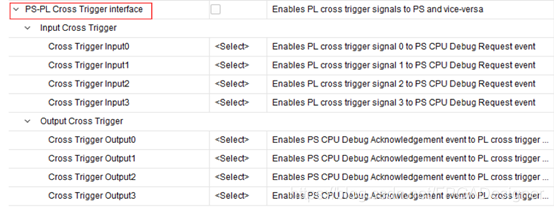

9. PS-PL交叉觸發(fā)接口

Zynq內(nèi)部有個(gè)基于交叉觸發(fā)機(jī)制的嵌入式交叉觸發(fā)器ECT。該組件基于CoreSight技術(shù),通過(guò)發(fā)送觸發(fā)器和接收觸發(fā)器來(lái)和其它組件交互。ECT主要由交叉觸發(fā)矩陣(CTM)和交叉觸發(fā)接口(CTI)組成。

一個(gè)或多個(gè)CTM組成一個(gè)具有多個(gè)頻道的廣播網(wǎng)絡(luò),一個(gè)CTI在一個(gè)或多個(gè)通道上監(jiān)聽(tīng)某一事件,將接收到的事件映射到觸發(fā)器,然后將觸發(fā)器發(fā)送到一個(gè)或多個(gè)與CTI相連的CoreSight組件中。CTI也可以組合和映射來(lái)自多個(gè)CoreSight組件的觸發(fā)器,并將其作為事件在一個(gè)或多個(gè)頻道中廣播。

在PS-PL Configuration中的PS-PL Cross Trigger Interface中可以啟用該功能:

Zynq中的PL部分

我相信不少人在沒(méi)接觸Zynq前會(huì)產(chǎn)生這樣的疑問(wèn):Zynq能否當(dāng)作一個(gè)純FPGA來(lái)使用?答案當(dāng)然是可以的。如果不用Zynq中的ARM處理器,則開(kāi)發(fā)流程與7系列FPGA完全相同。但Zynq的閃存接口是與PS部分相連的,因此我們不能將“純FPGA”程序固化到板子上,必須由處理器來(lái)引導(dǎo)。

Zynq中的可編程邏輯部分(PL)采用的也是與7系列相同的架構(gòu),下面還是給出其中包含的資源種類(lèi):

可配置邏輯塊(CLB),包含帶有存儲(chǔ)功能的6輸入查找表(LUT)、寄存器與移位寄存器功能、可級(jí)聯(lián)的加法器。

36Kb的塊RAM,雙端口,最高支持72bits位寬,可配置為雙18Kb,帶有可編程的FIFO邏輯電路和內(nèi)部錯(cuò)誤糾正電路

數(shù)字信號(hào)處理DSP48E1 Slice單元,12×18的2進(jìn)制補(bǔ)碼乘法器、累加器,高分辨率(48bit)的信號(hào)處理器,帶有25-bit的預(yù)加器以優(yōu)化對(duì)稱(chēng)結(jié)構(gòu)濾波器應(yīng)用。此外還包括可選的流水線、ALU和專(zhuān)用級(jí)聯(lián)總線等高級(jí)特性。

時(shí)鐘管理單元,超高速緩沖器與低斜率時(shí)鐘分布的布線,實(shí)現(xiàn)頻率綜合和相移功能,產(chǎn)生低抖動(dòng)時(shí)鐘,還帶有抖動(dòng)濾波。

可配置I/O,基于高性能SelectIOTM技術(shù),封裝內(nèi)有高頻去耦電容,以增強(qiáng)信號(hào)完整性;數(shù)控阻抗,可配置為三態(tài)以實(shí)現(xiàn)最低功耗,或滿足高速I(mǎi)/O操作;HR(大范圍) I/O支持1.2V到3.3V;HP(高性能)I/O支持1.2V到1.8V,如7z030、7z045、7z100系列。

模數(shù)轉(zhuǎn)換器XADC,雙12-bit、1MSPS,多達(dá)17個(gè)靈活的、用戶可配置的模擬輸入,可用于片內(nèi)或片外測(cè)量。帶有片內(nèi)溫度傳感器(±4℃)和電源供應(yīng)傳感器(±1%)。通過(guò)JTAG可獲取ADC測(cè)量結(jié)果。

除了這些基本單元,7z030、7z045、7z100等高端器件內(nèi)部還集成了低功率的Gbit收發(fā)器、PCI-E接口。

根據(jù)上文的實(shí)驗(yàn),我們知道在用SDK進(jìn)行軟件設(shè)計(jì)前先要在IP Integrator中完成硬件設(shè)計(jì)。設(shè)計(jì)者可以使用IP Packager工具將自己的設(shè)計(jì)封裝為IP,導(dǎo)入到IP Catalog中,之后便可以在設(shè)計(jì)中調(diào)用該IP。

原文鏈接:https://blog.csdn.net/FPGADesigner/article/details/88379785

-

處理器

+關(guān)注

關(guān)注

68文章

19586瀏覽量

232141 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1764瀏覽量

132365 -

中斷

+關(guān)注

關(guān)注

5文章

901瀏覽量

42129 -

IP核

+關(guān)注

關(guān)注

4文章

333瀏覽量

50022 -

Zynq7000

+關(guān)注

關(guān)注

0文章

16瀏覽量

7138

原文標(biāo)題:Zynq-7000處理器的配置詳解

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

評(píng)論