以下文章來源于學習那些事,作者小陳婆婆

晶圓級可靠性評價技術

隨著半導體工藝復雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術通過直接在未封裝晶圓上施加加速應力,實現快速、低成本的可靠性評估,成為工藝開發的關鍵工具,本文分述如下:

晶圓級可靠性(WLR)技術概述

晶圓級電遷移評價技術

自加熱恒溫電遷移試驗步驟詳述

1晶圓級可靠性(WLR)技術概述

WLR技術核心優勢

無需封裝:熱阻低,允許施加更高溫度和大電流密度而不引入新失效機理;

實時反饋:與工藝開發流程深度融合,工藝調整后可立即通過測試反饋評估可靠性影響;

行業標準化:主流廠商均發布WLR技術報告,推動其成為工藝驗證的通用方法。

WLR技術的核心目標與應用場景

本質目標:評估工藝穩健性,削弱本征磨損機理(如電遷移、氧化層擊穿),降低量產風險,并為工藝優化提供早期預警。

應用場景:新工藝或新技術開發階段,快速識別潛在可靠性問題;與傳統封裝級測試結合,實現全周期可靠性評估與壽命預測。

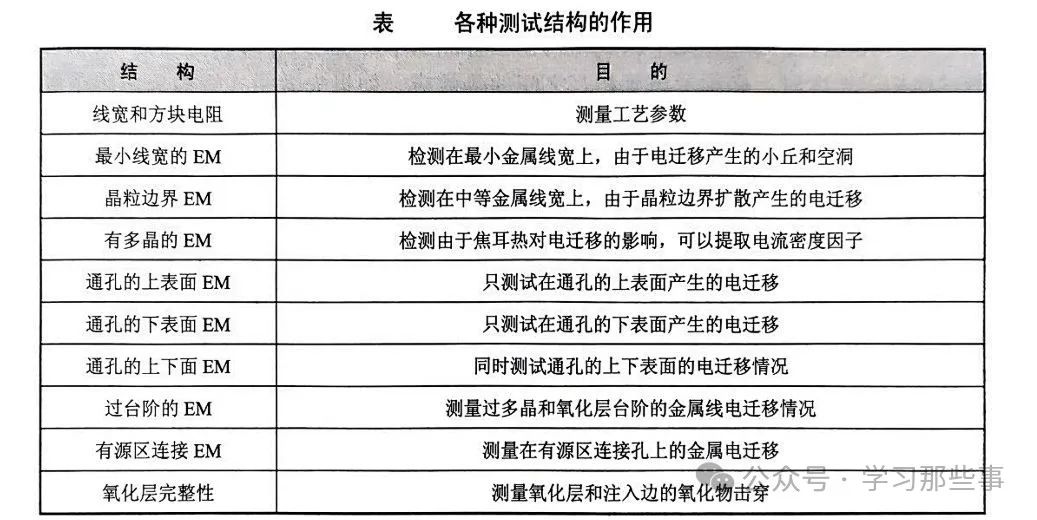

關鍵測試領域與失效機理

WLR技術聚焦半導體器件的本征可靠性,覆蓋以下核心領域:

金屬化可靠性——電遷移:互連測試結構監測通孔和有源區連接孔在電流應力下的失效。

氧化層完整性:測試結構檢測氧化層因缺陷或高電場導致的擊穿。

熱載流子注入:評估MOS管和雙極晶體管絕緣層因載流子注入導致的閾值電壓漂移、漏電流增大。

連接可靠性——鍵合完整性:檢測金屬層與硅界面在高溫或機械應力下的剝離或腐蝕。

其他失效機理:等離子損傷(天線效應),濺射工藝中電荷積累對柵氧化層的損傷;可動離子沾污,離子污染導致閾值電壓下降;層間介質完整性,低介電常數(low-k)材料在應力下的擊穿風險。

典型測試方法與結構

針對不同失效機理,WLR需設計專用測試結構并施加特定應力:

1.金屬化完整性測試

測試結構:蛇形金屬線或通孔鏈;

應力條件:高溫(>150℃)與大電流密度(>1×10? A/cm2);

監測參數:電阻變化率或開路/短路故障。

2.氧化層完整性測試

測試結構:電容結構(MOS電容或MIM電容);

應力條件:恒定電壓(如5V)或電場(>5 MV/cm);

監測參數:漏電流激增或擊穿時間(Time-to-Breakdown, TTB)。

3.熱載流子注入測試

測試結構:NMOS/PMOS晶體管;

應力條件:高溫(125℃)與高柵壓(如1.5×工作電壓);

監測參數:閾值電壓偏)、亞閾值斜率退化。

4.可動離子沾污測試

測試結構:晶體管陣列;

應力條件:高溫烘焙(如175℃)或反向偏壓;

監測參數:閾值電壓瞬時漂移。

5.濺射損傷測試

測試結構:柵氧化層直接連接金屬互連線;

應力條件:模擬濺射過程中的電荷積累;

監測參數:氧化層擊穿電壓或漏電流。

WLR技術的科學性與優勢

加速試驗設計:通過提高應力強度(溫度、電壓、電流)縮短失效時間,建立失效模型外推至實際工作條件。

統計工藝控制(SPC):基于大量晶圓數據,量化工藝波動對可靠性的影響,實現早期缺陷篩查。

與傳統測試對比:

速度:無需封裝,測試周期從數周縮短至數小時;

成本:避免封裝成本與測試設備損耗;

靈敏度:直接暴露工藝本征缺陷,避免封裝材料干擾。

晶圓級可靠性技術通過實時、高效的在線監測,將可靠性評估深度融入工藝開發流程,顯著加速了技術迭代并降低了量產風險。其科學化的測試設計與行業標準化趨勢,使其成為半導體制造中不可或缺的可靠性保障手段。

2晶圓級電遷移評價技術

電遷移是半導體器件中金屬互連和通孔失效的主要機理之一。為評估其可靠性,傳統方法依賴封裝級測試,但存在效率低、成本高的問題。晶圓級技術的發展為電遷移評價提供了更高效、精準的解決方案。以下是關鍵技術的分述:

傳統封裝法

原理:將封裝后的樣品置于高溫爐中,通入恒定電流,監測電阻變化。當電阻變化超過閾值時判定為失效,失效時間即為加速條件下的電遷移壽命。

缺點:耗時長,封裝過程復雜,測試周期長達數周;電流限制,為避免焦耳熱干擾爐溫測量,電流密度需控制在較低水平(如<1×10? A/cm2),進一步延長測試時間;溫度不確定性,金屬線自熱導致實際溫度高于爐溫,影響結果準確性。

自加熱法(晶圓級)

原理:利用金屬線自身的焦耳熱升溫,通過電阻溫度系數(TCR)實時計算金屬線溫度。通過調節電流控制溫度,無需封裝即可在晶圓級進行測試。

優勢:高效性,省去封裝步驟,測試周期縮短至小時級;精準控溫,直接關聯電流與溫度,避免外部加熱源干擾。

局限性——通孔測試失效:通孔與金屬線界面因電流集中導致局部過熱,無法準確測定整體結構溫度。

多晶硅加熱法

原理:在測試結構中集成多晶硅電阻作為加熱元件,通過多晶硅通電流產生熱量,間接加熱電遷移測試區域(如通孔)。多晶硅充當“片上爐子”,通過優化版圖設計(如多晶硅寬度、通孔數量)實現均勻加熱。

優勢:解決通孔測試難題,避免電流直接通過通孔,消除界面過熱問題;靈活控溫,通過多晶硅電阻設計調節加熱功率。

挑戰:版圖設計復雜,需精確控制多晶硅尺寸與通孔布局以確保溫度均勻性;工藝敏感性,多晶硅電阻值受工藝波動影響,需嚴格工藝控制。

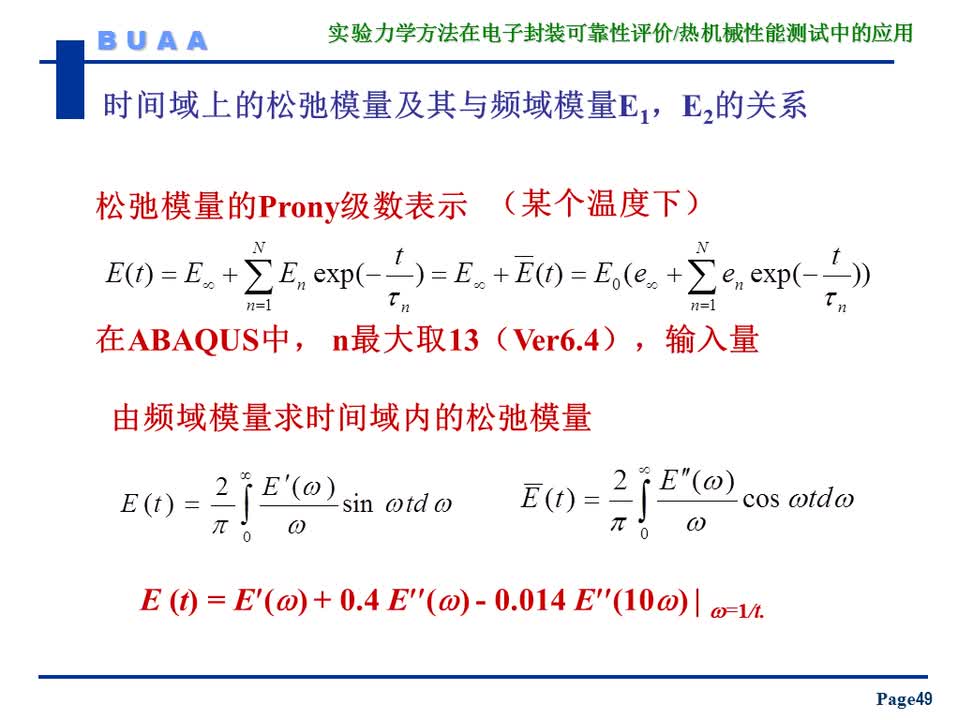

Black方程與壽命外推

上述方法均在加速應力條件下測試,需通過物理模型外推至實際工作條件。

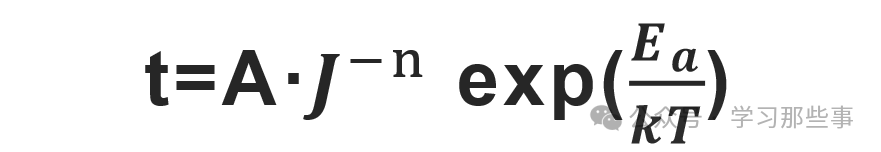

Black方程(上式),描述了電遷移壽命(t)與溫度(T)、電流密度(J)的關系。其中,Ea為激活能,n為電流密度因子(通常取2),k為玻爾茲曼常數。

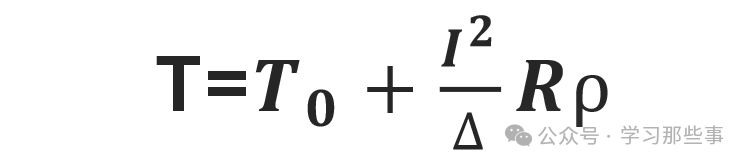

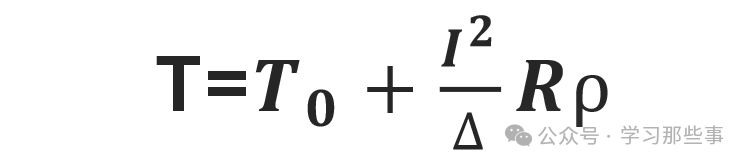

焦耳熱修正:晶圓級測試中,大電流導致金屬線溫升

其中,T0為初始溫度,R為電阻,ρ為電阻率,Δ為熱阻。將修正溫度代入Black方程,可更精準預測實際工作條件下的電遷移壽命。

意義:加速因子分離,明確溫度(主導)與電流(次要)對壽命的影響;設計規則優化,通過外推結果,指導金屬線寬度、通孔尺寸等工藝參數設計。

技術對比與演進

晶圓級電遷移評價技術通過自加熱和多晶硅加熱法克服了傳統封裝法的效率瓶頸,結合Black方程實現了從加速測試到實際壽命的精準預測,為半導體工藝可靠性優化提供了科學支撐。

3自加熱恒溫電遷移試驗步驟詳述

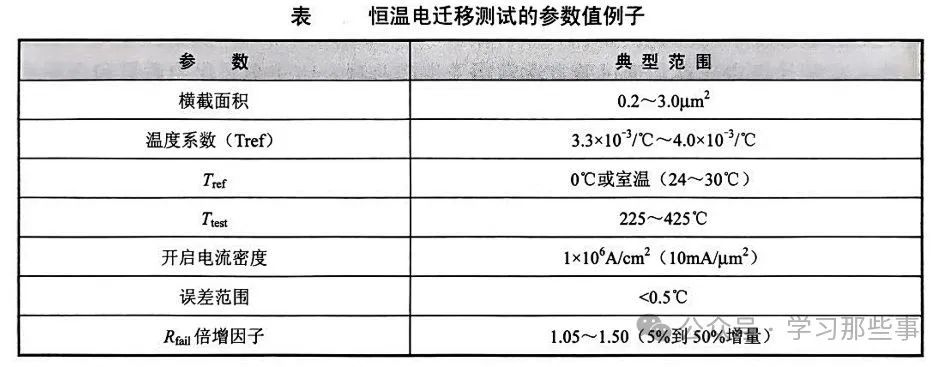

自加熱恒溫電遷移試驗基于JEDEC JESD61標準設計,通過一維熱流模型模擬金屬線溫度分布,核心目標是加速電遷移失效并量化壽命。

具體實驗步驟

試驗分為四階段,結合動態電流調節與溫度反饋控制。

初始測試階段

目的:確定金屬線初始電阻值(R0)及電阻溫度系數(TCR),為后續溫度計算提供基準。

操作:電阻測量,在恒溫條件下(如室溫)施加小電流(避免自熱),測量金屬線初始電阻R0;TCR標定:通過溫度掃描實驗(如變溫箱控制),建立電阻隨溫度變化的線性關系

電流上升測試階段

目的:逐步增加電流,計算熱阻并監測有效溫度,確保溫度趨近目標值。

操作:電流斜坡施加,以恒定速率(如10 mA/s)提升電流,每步平臺處測量電阻R。

熱阻計算:利用公式估算局部溫度。

終止條件:當有效溫度達目標溫度的80%時,結束該階段。

溫度收斂階段

目的:通過算法優化電流調節,使金屬線溫度精準收斂至目標值。

操作:收斂級數算法,采用動態電流增幅控制(如逐步減小電流調整步長),替代傳統差分熱阻法,避免溫度過沖。

實時反饋:基于電阻測量值(R(T))與TCR模型,動態調整電流以逼近目標溫度Ttarget。

恒定功率維持階段

目的:在目標溫度下持續監測電阻變化,直至失效發生。

操作:功率控制:根據初始目標溫度下的電阻值Rtarget,調節電流使輸入功率(P=I2R)恒定。

失效判據:電阻閾值:電阻值超過初始值的120%(R ~ fail~ ≥1.2?R ~ initial~ )。

實時終止:若電阻突增或開路,立即停止測試并記錄時間。

關鍵參數與注意事項

電流密度范圍:典型值1×10? ~ 3×10? A/cm2(對應10~300 mA/μm2),需根據金屬線寬度調整。

反饋控制頻率:控制周期≤500 ms(平衡精度與響應速度),最小周期≥50 ms(匹配熱時間常數)。

失效時間定義:斜坡/收斂階段失效:記為0時間失效(因未達目標溫度)。

恒定階段失效:記錄實際時間,未失效樣品需結合對數正態分布統計處理。

試驗后分析

失效模式觀察:去除鈍化層后,用掃描電鏡(SEM)檢查金屬線空洞、擠出等電遷移特征。

壽命外推:結合Black方程,將加速條件下的失效時間外推至實際工作條件。

通過上述步驟,恒溫電遷移試驗實現了對金屬互連可靠性的高效評估,為工藝優化提供數據支持。

-

半導體

+關注

關注

335文章

28121瀏覽量

226861 -

晶圓

+關注

關注

52文章

5042瀏覽量

128742 -

封裝

+關注

關注

127文章

8200瀏覽量

144026 -

工藝

+關注

關注

4文章

632瀏覽量

29061

原文標題:晶圓級可靠性評價技術

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

輸變電設施可靠性評價規程

晶圓級可靠性測試:器件開發的關鍵步驟

晶圓級多層堆疊技術的可靠性管理

廣立微推出晶圓級可靠性測試設備

評論