一、Verilog HDL 概述

1、Verilog HDL 是什么

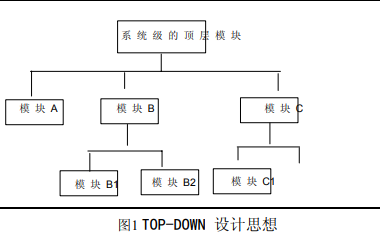

Verilog HDL(Hardware Description Language)是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。現實生活中多用于專用集成電路(Application Specific Integrated Circuit,ASIC)和現場可編程門陣列(Field Programmabl Gate Array,FPGA)的實現。

2、Verilog HDL產生的背景

第一只晶體管出現后,數字集成電路設計密度越來越大、電路越來越復雜,傳統的畫圖或連線的設計方法已不再適用。

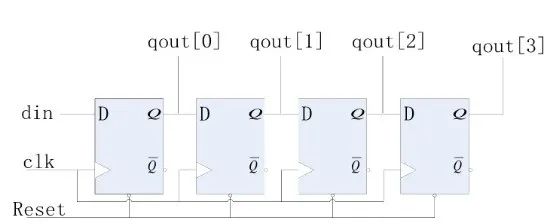

例如:設計4位移位寄存器,僅需簡短幾行代碼完成。

module register_four(

input clk,

input Reset,

input din,

output reg [3:0] qout

);

always @(posedge clk or posedge Reset)begin

if(Reset)

qout <= 4'b0;

else

qout <= {qout[2:0],din};

end

endmodule

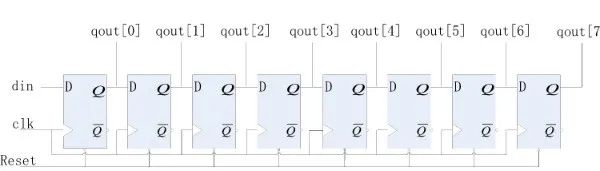

若要將4位移位寄存器改為8位移位寄存器,僅需修改少量代碼。

module register_eight(

input clk,

input Reset,

input din,

output reg [7:0] qout

);

always @(posedge clk or posedge Reset)begin

if(Reset)

qout <= 8'b0000_0000;

else

qout <= {qout[6:0],din};

end

endmodule

由上例可直觀發現,Verilog HDL可用較少的語句描述較為復雜的電路和靈活的可擴展性,為數字集成電路設計帶來了極大的便捷。

3、Verilog HDL 和 VHDL的區別

目前,Verilog HDL 和 VHDL(VHSIC Hardware Description Language,VHSIC 為 Very High Speed Integrated Circuit)是最為常用的硬件描述語音。

Verilog HDL:

語法靈活、寬松,多被思維活躍的美國人采用。因Verilog HDL 語法寬松,其不適合對系統要求層次嚴格的大規模設計。

VHDL:

語法結構緊湊、嚴謹,多被思維歐洲人采用。VHDL在大規模數字集成電路設計中具有一定優勢。

注:

Verilog基于C語言發展而來,語法靈活、寬松,且國內開發人員多采用Verilog,對初學者較為友好。

二、Verilog HDL 基礎知識

1、Verilog HDL 語言要素

1.1、命名規則

在Verilog HDL 中,標識符背用來命名信號、模塊、參數等,它可以是任意一組字母、數字、$符號和_(下劃線)符號的組合。

注:標識符中字母區分大小寫,且第一個字必須是字母或下劃線。

1.2、注釋符

單行注釋:單行注釋以“//”開始,Verilog HDL忽略此處到行尾的內容。

多行注釋:多行注釋采用“/**/”,從“/”開始,到“/”結束,Verilog HDL忽略其中注釋的內容。

注:多行注釋不允許嵌套,但單行注釋可以嵌套在多行注釋中。

例如:

非法多行注釋:

/*注釋內容/*多行注釋嵌套多行注釋*/注釋內容*/

合法多行注釋:

/*注釋內容//多行注釋嵌套單行注釋*/

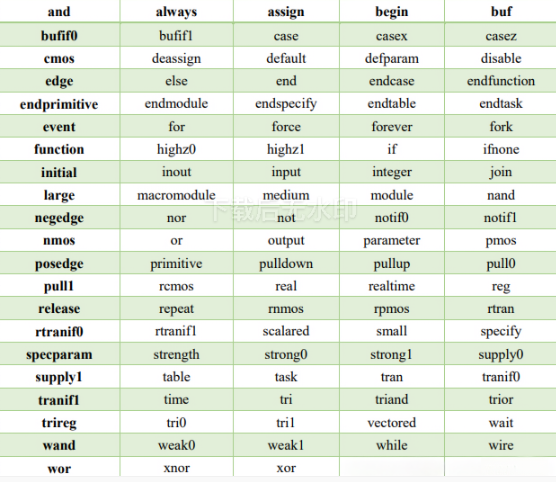

1.3、關鍵字

Verilog HDL 內部已經使用的詞成為關鍵字或保留字,是事先定義好的確認符,用來組織語言結構。

注:Verilog HDL中所有的關鍵字都是小寫的。

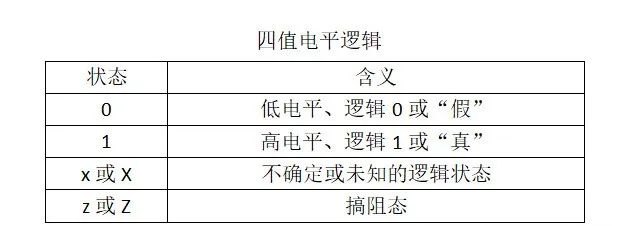

1.4、數值

Verilog HDL 有四種基本的電平邏輯數值狀態,用數字或字符表達數字電路中傳送的邏輯狀態和存儲信息。Verilog HDL邏輯數值中,“x”和“z”都不區分大小寫,即0x1z與0X1Z等價。

在數值中,下劃線符號“_”除不能放于首位外,可隨意用在整數與實數中,對數值的大小無影響,僅為提高可讀性。

例如:

8’b00110010 與8’b0011_0010的數值大小相等。

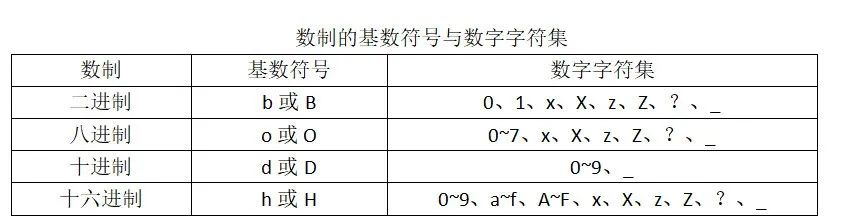

1.4.1、整數及其表示

整數的表示形式:

+/-

(1)“+/-”:正數和負數的標識。

(2)size:換算過后二進制的寬度。

(3)“ ’ ”:為基數格式表示固有字符,該字符不能缺省,否則為非法表示形式。

(4)base_format:基數符號。

(5)number:可使用的數字字符集。

例如:

4'b0011

7'd32

8'hfd

1.4.2、實數及其表示

(1)十進制表示法。

(2)科學計數發。例如:758.4e2 的值為75840.0,3e-3的值為0.003。

1.4.3、字符串及其表示

注:字符串必須包含在同一行中,不能分行書寫。

字符串在Verilog HDL中看做8位的ASCII值序列,即一個字符對應8位的ASCII值。

2、數據類型

按抽象程度 Verilog HDL數據類型可分為:物理數據類型(主要包括線網型及寄存器型)和抽象數據類型(主要包括整數型、時間型、實數型及參數型)。抽象數據類型主要用于輔助設計和驗證。

2.1、線網型(wire)

wire 類型表示硬件單元之間的物理連線,由其連接的器件輸出端連續驅動。如果沒有驅動元件連接到 wire 型變量,缺省值一般為 “Z”。對wire 類型賦值用“assign”。

例如:

wire data_out ;

wire flag ;

assign data_out = data_in ;

assign flag = 1'b1 ;

2.2、寄存器型(reg)

reg 用來表示存儲單元,它的數據會保持最后一次賦值,直到被改寫。reg 默認初始值為不定值“x”,缺省是數據位寬為1位。reg 一般為無符號數,若將一個負數賦值給 reg 型變量,則制動轉換其二進制補碼形式。

例如:

reg data0;

reg data1;

reg [4:0] data2;

2.3、存儲器型(memory)

存儲器型本質上還是寄存器型變量陣列,可以描述RAM型、ROM型存儲器以及reg文件。存儲器中的每一個單元通過索引進行尋址。

聲明格式:

reg

(1) range1:存儲器中寄存器的位寬,缺省,時為1,格式為[msb:lsb]。

(2)range2:寄存器的個數,缺省時為1,格式為[msb:lsb]。

(3)name_of_register:變量名稱列表,一次可以定義多個名稱,之間用逗號分開。

例如:

reg [7:0] mem1[255:0];//定義了一個有256個8位的存儲器

reg [15:0] mem2[127:0],reg1,reg2;//定義了一個具有128個16位的寄存器mem2

//2個16位的寄存器reg1和reg2

mem1[2] = 0; //給mem1存儲器中的第三個存儲單元賦值為0

2.4、整數型(integer)

整數類型用關鍵字 integer 來聲明。聲明時不用指明位寬,位寬和編譯器有關,一般為32 bit。reg 型變量為無符號數,而 integer 型變量為有符號數。

例如:

reg [31:0] data1 ;

reg [3:0] byte1 [7:0]; //數組變量,后續介紹

integer j ; //整型變量,用來輔助生成數字電路

always@* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8]; //把data1[7:0]…data1[31:24]依次賦值給byte1[0][7:0]…byte[3][7:0]

end

end

2.5、時間型(time)

Verilog 使用特殊的時間寄存器 time 型變量,對仿真時間進行保存。其寬度一般為 64 bit,通過調用系統函數 $time 獲取當前仿真時間。

例如

time current_time ;

initial begin

#100 ;

current_time = $time ; //current_time 的大小為 100

end

2.6、實數型(real)

實數用關鍵字 real 來聲明,可用十進制或科學計數法來表示。實數聲明不能帶有范圍,默認值為 0。如果將一個實數賦值給一個整數,則只有實數的整數部分會賦值給整數。

例如:

real data1 ;

integer temp ;

initial begin

data1 = 2e3 ;

data1 = 3.75 ;

end

initial begin

temp = data1 ; //temp 值的大小為3

end

2.7、參數型

參數用來表示常量,用關鍵字parameter聲明,只能賦值一次,但可通過實例化的方式更改參數在模塊中的值。局部參數用localparam聲明,其作用和用法與parameter相同,區別在于它的值不能改變。所以當參數在本模塊中調用時,可以用localparam來說明。

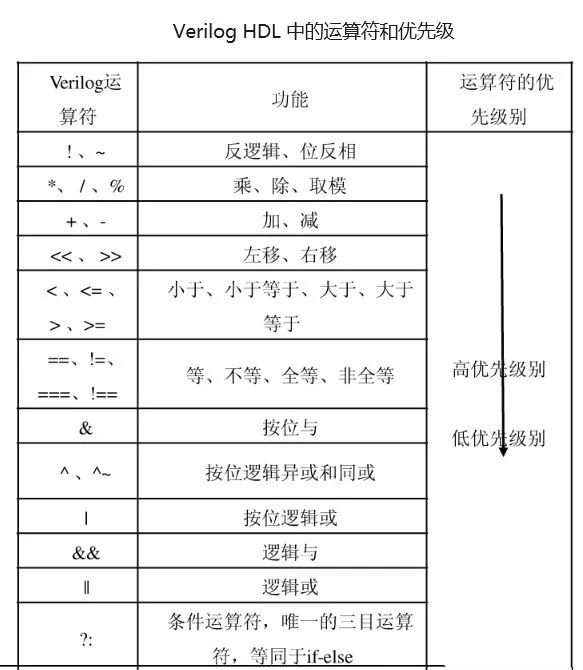

3、運算符

3.1、算術運算符

Verilog HDL中常用的算術運算符主要有五種,分別是加法(+)、減法(-)、乘法(*)、除法(/)和取模(%)。

注:

算術表達式結果的長度由最長的操作數決定。在賦值語句下,算術結果的長度由等號操作符左端的目標長度決定。

3.2、關系運算符

關系運算符也是雙目運算符,是對兩個操作數的大小進行比較。關系運算符有大于(>)、小于(<)、大于等于(>=)和小于等于(<=)幾種。

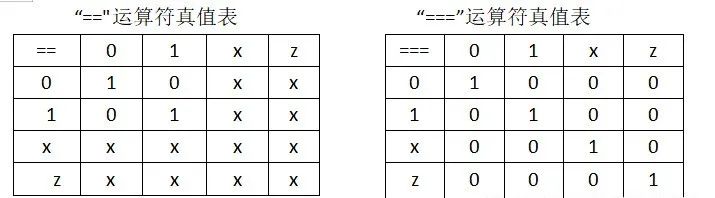

3.3、相等關系運算符

相等關系運算符是對兩個操作數進行比較,比較結果有三種,即真(1)、假(0)和不定值(x)。Verilog HDL 中有四種相等關系運算符:等于(==)、不等于(!=)、全等(===)、非全等(!==)。

3.4、邏輯運算符

邏輯運算符有三種,分別為邏輯與(&&)、邏輯或(||)、邏輯非(!)。其中邏輯與、邏輯或是雙目運算符,邏輯非為單目運算符。

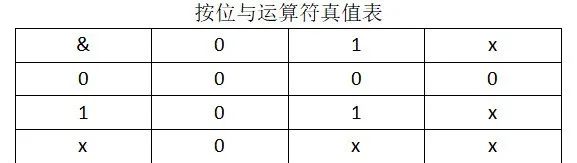

3.5、按位運算符

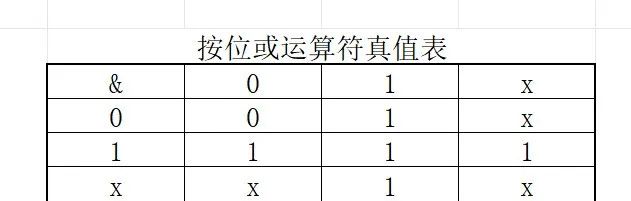

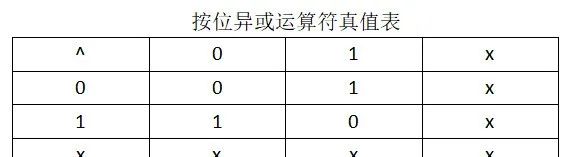

Verilog HDL 提供了五種類型位運算符:按位取反(~)、按位與(&)、按位或(|)、按位異或(^ )、按位同或(^~),按位運算符對其自變量的每一位進行操作。

3.6、歸約運算符

歸約操作符包括:歸約與(&),歸約與非(~&),歸約或(|),歸約或非(~|),歸約異或(^),歸約同或(~^)。歸約操作符只有一個操作數,它對這個向量操作數逐位進行操作,最終產生一個 1bit 結果。邏輯操作符、按位操作符和歸約操作符都使用相同的符號表示,因此有時候容易混淆。區分這些操作符的關鍵是分清操作數的數目,和計算結果的規則。

例如:

A = 4'b1010 ;

&A ; //結果為 1 & 0 & 1 & 0 = 1'b0,可用來判斷變量A是否全1

~|A ; //結果為 ~(1 | 0 | 1 | 0) = 1'b0, 可用來判斷變量A是否為全0

^A ; //結果為 1 ^ 0 ^ 1 ^ 0 = 1'b0

3.7、移位運算符

移位操作符包括左移(<<),右移(>>),算術左移(<<<),算術右移(>>>)。移位操作符是雙目操作符,兩個操作數分別表示要進行移位的向量信號(操作符左側)與移動的位數(操作符右側)。算術左移和邏輯左移時,右邊低位會補 0。邏輯右移時,左邊高位會補 0;而算術右移時,左邊高位會補充符號位,以保證數據縮小后值的正確性。

A = 4'b1100 ;

B = 4'b0010 ;

A = A >> 2 ; //結果為 4'b0011

A = A << 1; ? ? ? ? //結果為 4'b1000

A = A <<< 1 ; ? ? ? //結果為 4'b1000

C = B + (A>>>2); //結果為 2 + (-4/4) = 1, 4'b0001

3.8、連接運算符

拼接操作符用大括號 {,} 來表示,用于將多個操作數(向量)拼接成新的操作數(向量),信號間用逗號隔開。拼接符操作數必須指定位寬,常數的話也需要指定位寬。

例如:

A = 4'b1010 ;

B = 1'b1 ;

Y1 = {B, A[3:2], A[0], 4'h3 }; //結果為Y1='b1100_0011

Y2 = {4{B}, 3'd4}; //結果為 Y2=7'b111_1100

Y3 = {32{1'b0}}; //結果為 Y3=32h0,常用作寄存器初始化時匹配位寬的賦初值

-

FPGA

+關注

關注

1637文章

21848瀏覽量

608777 -

寄存器

+關注

關注

31文章

5393瀏覽量

121990 -

Verilog

+關注

關注

28文章

1356瀏覽量

110911 -

晶體管

+關注

關注

77文章

9854瀏覽量

139579 -

HDL

+關注

關注

8文章

329瀏覽量

47574

原文標題:Verilog HDL 入門教程

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog-HDL實踐與應用系統設計

Verilog HDL華為入門教程

什么是Verilog HDL?

Verilog_HDL的基本語法詳解(夏宇聞版)

詳解Verilog HDL數字設計與綜合 夏宇聞譯(第二版)

Verilog HDL入門教程

Verilog HDL入門教程之Verilog HDL數字系統設計教程

Verilog HDL入門教程

評論