HZ-CORE-RK3588J_K7是合眾恒躍推出的一款ARM+FPGA異構融合的工業級核心板,集成了瑞芯微RK3588J處理器和Xilinx Kintex-7 FPGA,旨在滿足工業控制、人工智能等領域對高性能和高可靠數據處理的需求。這款核心板將ARM處理器的強大通用計算能力與FPGA的高度并行可編程能力相結合,實現了低延遲、高帶寬的高速數據處理。

在本文中,我們將深入分析HZ-CORE-RK3588J_K7所采用的FPGA技術架構及其在高性能數據處理中的應用。

01

高速數據處理能力

FPGA最大的優勢在于高度并行計算能力。與CPU的順序計算不同,FPGA內部擁有大量邏輯單元和DSP單元,能同時執行多項計算任務,如FFT、數字濾波、矩陣運算等算法,顯著提升數據處理效率。此外,HZ-CORE-RK3588J_K7集成的Kintex-7 GTX高速收發器,能夠實現FPGA與外設之間直接的高速數據交換,例如PCIe接口、多路10G以太網以及高速ADC接口,減少數據拷貝和中間緩沖環節,有效降低延遲并提高數據吞吐率。

值得一提的是,在高速串行鏈路中,為了確保信號完整性和可靠傳輸,GTX收發器還提供了一系列可調節參數和功能,例如預加重、均衡、時鐘數據恢復(CDR)等。工程師可以根據高速信號的傳輸距離和介質,優化GTX收發器的設置以降低誤碼率。在高速通信應用中,充分發揮FPGA GTX收發器的性能并進行合理的協議定制,可以實現低延遲、高可靠的數據鏈路,這是軟件實現難以企及的。總體而言,FPGA的高度并行計算加上GTX高速通信,使其在需要海量數據實時處理的場景中表現卓越。

02

PCIe 3.0數據加速機制

在HZ-CORE-RK3588J_K7架構中,FPGA與ARM處理器之間通過PCI Express高速總線相連。PCIe 3.0提供每通道8 GT/s的速率,可實現GB/s級別的數據吞吐。FPGA利用PCIe 3.0接口作為與處理器交換數據的橋梁,構建起低延遲的高速數據通道。Kintex-7 FPGA內部集成了PCIe硬核模塊,支持實現PCIe Gen3 x4甚至x8的端點設計。通過PCIe接口,FPGA可以被映射為處理器系統中的一款高速外設,支持DMA(直接內存訪問)等機制高效地與系統內存交換數據。

為了充分發揮PCIe 3.0的數據加速作用,工程師在設計時需要關注以下幾點優化措施:

增大數據吞吐粒度

盡量使用較大的PCIe傳輸payload和批量DMA傳輸,以減少總線握手開銷。例如,將數據打包成幾百KB甚至更大的塊再通過DMA發送,比頻繁發送小數據包效率更高。

異步并行傳輸

使用FPGA內部多DMA通道或多隊列機制,實現讀寫并行或多流并行傳輸。這樣可以充分利用PCIe多條通道的帶寬,防止單一事務阻塞影響整體吞吐。

流水線設計

在FPGA中設計好數據緩沖和流水線,使得數據在采集->處理->傳輸各階段能夠重疊執行。例如采用Ping-Pong雙緩沖,FPGA在DMA傳輸當前緩沖區數據的同時,下一塊數據采集或計算不間斷進行,從而實現數據流的連續高速輸出。

通過以上策略,FPGA可以將PCIe 3.0鏈路的帶寬利用率最大化,實現與ARM內存之間近似實時的大容量數據交換。在數據采集(如高速ADC數據傳輸)、視頻處理(如4K/8K超高清視頻幀傳輸)等場景下,這種基于PCIe的FPGA加速機制能夠顯著提高系統的數據吞吐量和響應速度。

03

FPGA DDR3L高速緩存使用

HZ-CORE-RK3588J_K7核心板在FPGA旁配備DDR3L高速內存,作為FPGA的大容量緩存。相比Block RAM,DDR3L容量更大(數百MB至數GB),位寬更高、頻率更快,數據存取速率更高。FPGA通過內置的控制器(如Xilinx MIG IP)管理DDR3L,通常速率可達1600 MT/s以上,32位接口理論帶寬約6.4 GB/s。

FPGA可將DDR3L用作幀緩沖、FIFO隊列或臨時數據池。例如多路高清視頻處理中可緩存視頻幀進行并行編解碼;高速數據采集中可作環形緩沖區,平衡數據流處理的不均衡性,解決外設與處理單元之間的速率差異。

為了充分發揮DDR3L在FPGA中的作用,架構設計上通常會考慮多通道數據處理和多端口存儲訪問:

多通道數據處理

針對多路并發數據,FPGA可在DDR3L中為每路數據設獨立緩沖區,各通道讀寫邏輯獨立、互不干擾。通過時間分片或多端口并行方式實現數據訪問,有效保證并發數據流的高效存取。DDR3L的大帶寬和容量可避免峰值流量下的數據丟失與延遲。

多端口存儲架構

高性能FPGA設計中,多個模塊常需同時訪問DDR存儲,如數據采集模塊寫入、處理模塊讀取計算。為避免訪問沖突,可采用存儲調度機制或雙端口RAM架構。Kintex-7通過AXI總線矩陣和仲裁器,實現多主設備共享DDR3控制器。邏輯設計上,可利用雙緩沖(Ping-Pong Buffer):當一個緩沖區寫滿時切換至另一緩沖區,讀寫并行交替進行,提高DDR利用率。HZ-CORE-RK3588J_K7板載DDR3L高速存儲和靈活時鐘管理,確保數據精準同步。在雷達信號處理、圖像識別等高實時性場景下,FPGA借助DDR3L緩存實現實時處理與批處理的高效平衡。通過優化緩存架構和訪問策略,DDR3L成為系統高速數據處理的核心緩沖區,保障數據高效流動。

04

FPGA與ARM的協同計算

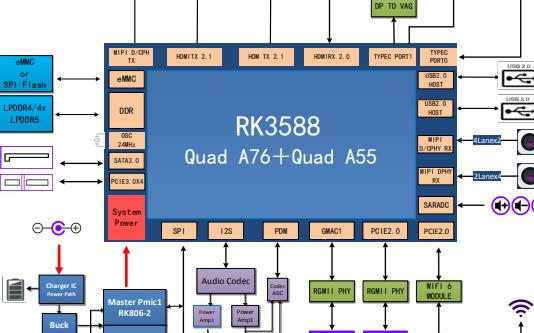

ARM端采用八核RK3588J(4核Cortex-A76+4核Cortex-A55,主頻2.0GHz),內置6.0 TOPS算力NPU,適合AI推理、多媒體編解碼等任務;FPGA端提供靈活可編程邏輯和強大并行計算能力,擅長定制算法加速與實時控制。兩者通過高速接口共享數據和同步協作,ARM負責通用任務處理和調度,FPGA作為硬件加速器處理高實時性、高吞吐任務,形成高效的異構計算平臺。具體協同方式包括:

AI推理

雖然RK3588J內置了強大的NPU,但FPGA在AI任務中仍有獨特價值。FPGA可實現NPU不擅長的運算(如非標準精度處理、特殊模型加速),并可用于數據預處理(圖像去噪、校正)或后處理,減輕ARM負載、優化整體性能。在特定場景中,FPGA還能實現完整的定制AI推理邏輯。ARM通過驅動程序向FPGA下發模型或部分計算任務,完成加速后再回傳結果,從而同時利用NPU的高效與FPGA的靈活,實現更快、更靈活的AI推理。

視頻編解碼與多媒體處理

RK3588J處理器具備4K/8K視頻編解碼能力,可處理常見視頻格式。但在特殊任務中,FPGA可提供輔助,例如在工業視覺場景下,對多路視頻進行拼接、縮放和顏色轉換后再交由ARM或GPU編碼。FPGA還能實現定制濾波或圖像增強,降低處理延遲、提高吞吐性能。FPGA與ARM通過共享緩沖區和中斷機制協作,完成圖像處理后通知ARM進行編碼。此外,FPGA也可支持新興或專有的視頻編解碼標準,擴展系統的多媒體能力。

工業自動化與實時控制

在工業控制系統中,FPGA憑借確定時序和高并行IO能力,實現高實時控制算法和高速接口協議,例如高速PID運算和伺服控制。ARM則負責路徑規劃、參數調節和人機交互等高層軟件任務。當發生緊急情況時,FPGA能迅速執行保護措施并通知ARM處理。在工業通信領域,FPGA可硬件實現EtherCAT、PROFINET等實時協議,保證微秒級通信精度,ARM則運行協議棧與高層邏輯。

整體上,系統采用ARM主控、FPGA加速的協同模式:ARM處理復雜決策、通信和交互任務,FPGA執行實時性強、計算密集的任務,兩者通過PCIe或片上總線協同工作,實現軟硬件優勢互補,達到“1+1>2”的效果。

05

實際應用案例

得益于以上所述的架構優勢,HZ-CORE-RK3588J_K7在眾多高性能數據處理場景中都有用武之地。下面結合幾個實際案例,闡述FPGA在提升性能方面的作用,并給出相應的設計建議。

案例1:多通道工業數據采集與實時分析

實際應用中,工業物聯網系統需要實時采集和分析多路高速傳感器數據(如高頻振動信號)。采用FPGA直接連接ADC前端,可完成多通道數據采集和數字濾波、FFT頻譜分析等預處理,再通過PCIe接口將處理結果高速傳輸給ARM。ARM則負責故障診斷、數據上報并通過以太網上傳至云端。

FPGA保證每個傳感器通道數據實時、穩定采集,避免CPU負載過高造成數據丟失;ARM專注高層分析與通信任務。這種架構相比純CPU方案,延遲更低、擴展性更佳,增加傳感器通道僅需擴展FPGA邏輯單元,無需大量修改ARM軟件。整體而言,FPGA協處理模式有效實現了工業數據采集系統的實時、高可靠監測和分析。

案例2:軟件無線電(SDR)高速信號處理

軟件無線電(SDR)需要對射頻信號進行數字下變頻、濾波和調制解調等高速處理。據此,FPGA通過與高速ADC/DAC配合,實現射頻與基帶間的實時轉換與信號處理。在LTE/5G小基站設計中,FPGA完成PHY層高速FFT/IFFT、信道編碼、數字上下變頻,ARM則負責MAC層及以上協議處理和網絡通信。

此外,通過FMC接口可擴展射頻子卡,可直接連接FPGA的GTX收發器和高速IO,支持MIMO多通道并行處理。FPGA解調后的數據交由ARM組幀和網絡處理,ARM發送的數據再由FPGA編碼調制并發射。實際應用表明,這種ARM+FPGA協同架構實現了傳統DSP難以達到的高吞吐與低延遲,充分體現了FPGA在SDR領域的性能優勢與協作價值。

案例3:多攝像頭圖像處理與智能分析

在智能視覺系統中,經常需要同時處理多路高清攝像頭視頻,并運行AI算法進行目標檢測或識別。FPGA可通過板載擴展接口并行采集多路MIPI攝像頭圖像數據,進行實時的縮放、同步、預處理等操作,再經PCIe傳輸至ARM處理器。ARM結合NPU完成AI推理,實現目標識別和分類。FPGA有效保證多攝像頭數據的實時同步與低延遲預處理,顯著降低整體分析延遲,提高系統吞吐量,滿足工業與安防場景對實時性的嚴格要求。

綜上所述,HZ-CORE-RK3588J_K7核心板通過其Kintex-7 FPGA的靈活可編程架構,在高性能數據處理領域展現出了強大的加速能力。

從工業傳感、無線通信到視覺AI,各類應用都可以從ARM+FPGA的協同計算中受益。在設計這些系統時,我們建議工程師充分利用FPGA的并行硬件特性和高速通信接口,將關鍵的性能瓶頸部分卸載到FPGA中執行。同時注重ARM與FPGA之間的高效協作,通過硬件架構和軟件架構的協調優化,工程師能夠構建出性能卓越且靈活可靠的高性能數據處理系統,充分發揮HZ-CORE-RK3588J_K7這樣的ARM+FPGA異構平臺的價值。

-

FPGA

+關注

關注

1641文章

21910瀏覽量

611647 -

ARM

+關注

關注

134文章

9265瀏覽量

373254 -

核心板

+關注

關注

5文章

1082瀏覽量

30491

發布評論請先 登錄

相關推薦

瑞芯微RK3588開發板RK3588 EVB和RK3588S EVB解讀

重磅!基于瑞芯微RK3588旗艦芯片打造的MinipcRK3588面世

RK3588是什么元件 RK3588的功耗如何

ITX 3588J源代碼RK356X/RK3588 RKNN SDK

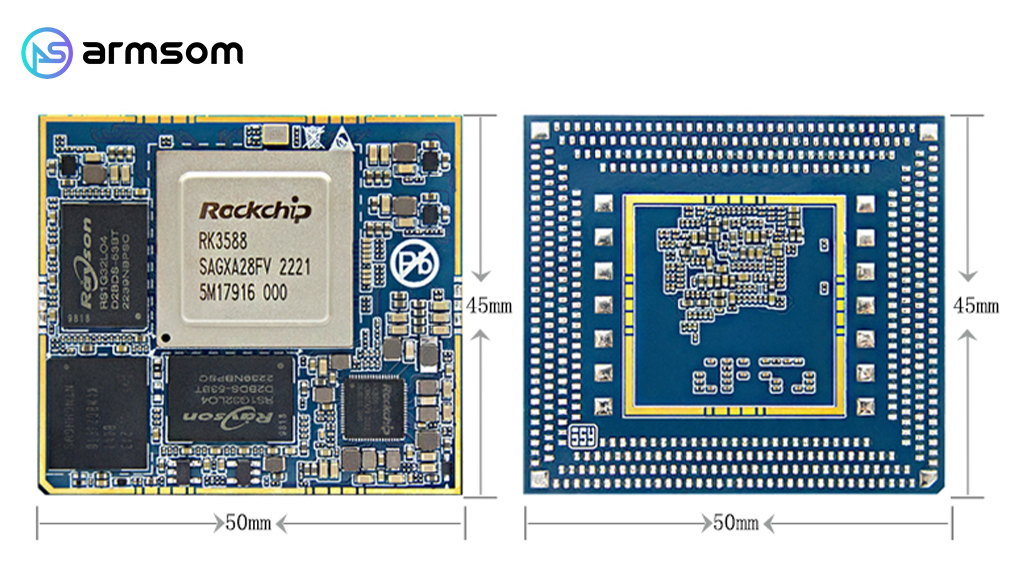

【LGA封裝RK3588核心板】基于RK3588,小而強大的ArmSom-W3 CORE BOARD

rk3588和rk3588s的區別

rk3588是armv8嗎?rk3588硬件資料

新品發布 ▏性能猛獸登場!瑞芯微RK3588J_K7 ARM+FPGA雙核異構核心板重磅發布!

破界而生,智領未來——瑞芯微RK3588J_K7的“悟空之力”

PET_RK3588_CORE核心板

評論