本文介紹了應(yīng)用GaN Systems器件的PCB布局設(shè)計原則, 包含以下四種電路:

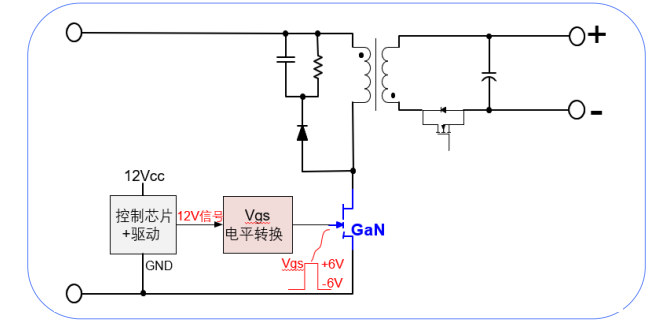

- 單管GaN E-HEMTs 的隔離驅(qū)動電路

- 并聯(lián)GaN E-HEMTs 的隔離驅(qū)動電路

- 半橋自舉門極驅(qū)動電路

- EZDriveSM 電路

? 優(yōu)化的電路板布局和極低的封裝電感是優(yōu)化氮化鎵器件開關(guān)性能的關(guān)鍵

** 為什么我們需要優(yōu)化PCB layout?**

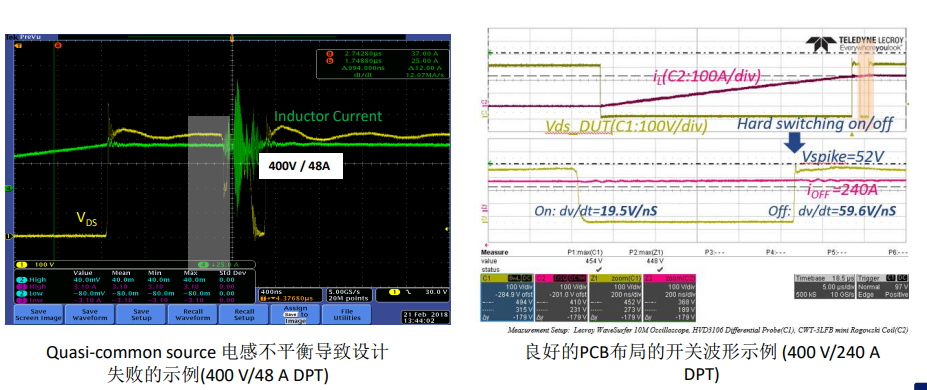

GaN 增強型器件開關(guān)速度遠(yuǎn)快于Si MOSFETs, 所以需要恰當(dāng)?shù)腜CB 布局設(shè)計以減小寄生電感

寄生電感會導(dǎo)致較高的過沖電壓, 振蕩, 和EMI問題, 使得GaN器件承受過大的電氣應(yīng)力

GaN E-HEMT的PCB布線考慮

GaN E-HEMTs的PCB布局總結(jié)

一、總述

- ?內(nèi)容?:本文件介紹了應(yīng)用GaN Systems器件的PCB布局設(shè)計原則,涵蓋單管GaN E-HEMTs的隔離驅(qū)動電路、并聯(lián)GaN E-HEMTs的隔離驅(qū)動電路、半橋自舉門極驅(qū)動電路以及EZDrive SM電路。

- ?關(guān)鍵點?:優(yōu)化的電路板布局和極低的封裝電感是優(yōu)化氮化鎵器件開關(guān)性能的關(guān)鍵。

二、PCB布局的重要性

- ?開關(guān)速度?:GaN增強型器件的開關(guān)速度遠(yuǎn)快于Si MOSFETs,需要恰當(dāng)?shù)腜CB布局設(shè)計以減小寄生電感。

- ?寄生電感影響?:寄生電感會導(dǎo)致較高的過沖電壓、振蕩和EMI問題,增加GaN器件承受的電氣應(yīng)力。

三、PCB布局步驟

步驟1:確定原理圖

- 確定每個關(guān)鍵電路的構(gòu)成,包括單管GaN器件的隔離驅(qū)動電路、并聯(lián)GaN器件的隔離驅(qū)動電路、半橋自舉門極驅(qū)動電路和EZDrive SM電路。

步驟2:放置組件

- ?原則?:將組件盡可能靠近放置,根據(jù)當(dāng)前電流方向依次設(shè)置組件。

- ?優(yōu)先級?:根據(jù)設(shè)計優(yōu)先級最小化所有回路,具體優(yōu)先級根據(jù)電路類型(如功率換流回路、門極驅(qū)動回路等)確定。

步驟3:連接組件

- ?技術(shù)?:通過磁通消除技術(shù)降低寄生電感,即調(diào)整layout使高頻電流在兩個相鄰的PCB層上以相反的方向流動,從而抵消磁通量。

四、具體電路設(shè)計原則

1. 單管GaN器件的隔離驅(qū)動電路

- ?功率換流回路?:Q1, Q2, C_BUS應(yīng)盡可能小。

- ?門極驅(qū)動回路?:開通和關(guān)斷回路中的組件(如C5, U1, R_gon, Q2等)應(yīng)靠近放置。

2. 并聯(lián)GaN器件的隔離驅(qū)動電路

- ?功率換流回路?:Q1, Q2, C_BUS應(yīng)盡可能小,并聯(lián)器件應(yīng)盡可能對稱。

- ?門極驅(qū)動回路?:每個器件的開通和關(guān)斷回路應(yīng)獨立設(shè)計,確保電流平衡。

3. 半橋自舉門極驅(qū)動電路

- ?功率換流回路?:Q1, Q2, C_BUS應(yīng)盡可能小。

- ?門極驅(qū)動回路?:上管和下管的開通和關(guān)斷回路應(yīng)獨立設(shè)計,使用自舉電容和二極管提供上管門極驅(qū)動電壓。

4. EZDrive SM電路

五、磁通消除技術(shù)應(yīng)用

- ?原理?:當(dāng)兩個相鄰的導(dǎo)體以相反的電流方向靠近放置時,兩個電流產(chǎn)生的磁通量將相互抵消,從而降低寄生電感。

- ?實施?:在PCB設(shè)計中,通過調(diào)整走線布局,使高頻電流在兩個相鄰層上以相反方向流動,實現(xiàn)磁通抵消。

六、總結(jié)

- ?優(yōu)化布局?:良好的PCB布局對于充分發(fā)揮GaN器件的性能至關(guān)重要,可以顯著減小寄生電感,降低過沖電壓和振蕩。

- ?設(shè)計原則?:遵循關(guān)鍵電路設(shè)計原則,如最小化功率換流回路和門極驅(qū)動回路的電感,確保組件的適當(dāng)放置和連接。

- ?磁通消除?:利用磁通消除技術(shù)進一步降低寄生電感,提高電路的穩(wěn)定性和效率。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

GaN

+關(guān)注

關(guān)注

19文章

2085瀏覽量

75075 -

PCB布局

+關(guān)注

關(guān)注

9文章

185瀏覽量

27980 -

Pcb layout

+關(guān)注

關(guān)注

6文章

99瀏覽量

29260 -

PCB

+關(guān)注

關(guān)注

1文章

1866瀏覽量

13204

發(fā)布評論請先 登錄

相關(guān)推薦

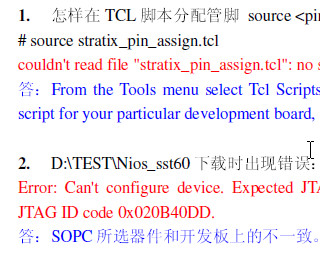

SOPC Builder/Nios 學(xué)習(xí)經(jīng)驗總結(jié)

SOPC Builder/Nios 學(xué)習(xí)經(jīng)驗總結(jié)

發(fā)表于 07-22 15:32

?0次下載

PCB板繪制經(jīng)驗總結(jié)

PCB板的繪制經(jīng)驗總結(jié):(1):畫原理圖的時候管腳的標(biāo)注一定要用網(wǎng)絡(luò) NET不要用文本TEXT否則導(dǎo)PCB設(shè)計的時候會出問題(2):畫完原理圖的時候一

發(fā)表于 09-19 23:52

?3821次閱讀

做四軸飛行器的經(jīng)驗總結(jié)

做四軸飛行器的經(jīng)驗總結(jié),請各位大神共同學(xué)習(xí),里面是一位大神做四軸飛行器的經(jīng)驗總結(jié)

發(fā)表于 11-11 16:52

?0次下載

麥斯艾姆的資深工程師PCB電路板設(shè)計經(jīng)驗總結(jié)

資深工程師pcb電路板設(shè)計經(jīng)驗總結(jié),涉及原理圖設(shè)計的前期準(zhǔn)備和設(shè)計的注意事項

發(fā)表于 03-24 14:49

?0次下載

模擬電路設(shè)計經(jīng)驗總結(jié)

模擬電子的相關(guān)知識學(xué)習(xí)教材資料——模擬電路設(shè)計經(jīng)驗總結(jié)

發(fā)表于 09-27 15:19

?0次下載

評論