FPGA 通常按照邏輯容量進行分類,這種方式固然簡單,但未能充分體現現代 FPGA 作為可更改的片上系統所能提供的豐富功能和資源。

現代中端FPGA的主要亮點

- 高性能邏輯結構,可支持嚴苛的邏輯需求;

- 部分重配置,無需停機即可調整;

- 集成處理器,可提高能效和速度。

高性能邏輯結構

事實上,邏輯容量僅僅是 FPGA 邏輯結構的其中一個指標。大多數需要中端設備密度的應用,還需要邏輯以足夠快的速度運行,從而跟上高速收發器和現代內存接口的速度。

由于復雜邏輯所需層數過多,使用基礎的 4 輸入查找表(LUT) 無法達到這種性能水平,還會限制運行頻率。要達到中端性能水平,至少需要 6 輸入 LUT,而Altera 提供的更先進的 8 輸入自適應邏輯模塊 (ALM)則更為理想。

硬核 IP/內存控制器

中端 FPGA 的另一個重要組成部分是硬核 IP,尤其是內存控制器。許多應用都需要外存,利用現代內存接口,以可管理的引腳數實現設備的數據輸入和輸出,這一點非常重要。

而在可編程設備中,要實現這類接口的高速數據傳輸并非易事。鑒于這一 IP 在應用中非常常見,并且內存接口已經實現標準化,因此采用硬核模塊來實現這些功能是更佳的選擇。與邏輯結構中的實現方式相比,硬核模塊可確保滿足時序要求,還能顯著減小占用的芯片面積,這對于 PCIe 或以太網控制器等其他常見 IP 模塊也同樣適用。

高速收發器

由于向邏輯模塊和內存進行數據傳輸需要高速通道,因此與內存接口一樣,高速收發器也是中端 FPGA 的關鍵特性之一。FPGA 用途廣泛,適用于許多應用,而收發器也需要具有同樣的靈活性。

用戶需要選擇配備靈活收發器的設備和擁有龐大 IP 庫的公司,以便滿足所需標準。隨著收發器速度的提高,信號完整性問題愈發凸顯,Quartus Prime 收發器工具包等先進工具在開發過程中顯得尤為重要。綜上所述,在評估中端 FPGA 時,務必要把收發器工具和 IP 庫納入考量范圍。

部分重配置

FPGA 的一大優勢在于能夠根據需要即時改變行為,這種能力可用于修復錯誤、適應不斷變化的標準、增加新功能并加速產品上市。

在某些情況下,必須在不關閉系統的情況下應用更新,這可能要依靠 FPGA 內部的某些邏輯結構,而部分重配置則讓無中斷更新成為可能。此外,由于用戶可以通過動態更換邏輯來實現邏輯資源分時共享,部分重配置還有助于在更小的設備中實現功能(或在不增加設備面積的情況下增加功能)。

硬核處理器子系統 (HPS)

如今,幾乎所有電子設備都采用了某種形式的處理器。每個可編程邏輯設備內部或旁邊可能都有一個處理器。出色的 FPGA 供應商會提供軟核和硬核處理器等一系列嵌入式處理器供用戶選擇。在處理器和邏輯模塊之間傳輸數據時,FPGA 中的集成處理器具有顯著優勢,可以節省功耗和引腳。

與常見的 IP 模塊一樣,硬核處理器較邏輯內部的處理器速度更快,能效和芯片面積效率更高。過去,與獨立嵌入式處理器相比,集成處理器的性能有限,但Agilex 5等新型中端設備中的集成處理器可與許多工業嵌入式處理器相媲美。在選擇中端 FPGA 時,需確保有集成硬核處理器可供選擇。

Altera中端FPGA設備系列

Altera 推出了專門針對中端市場的設備系列。Arria 設備家族自問世以來,始終追求在性能、功耗和成本效益之間找到理想的平衡點,提供介于成本優化型設備(如Cyclone)和高性能設備(如Stratix)之間的理想選擇。要實現這一平衡,關鍵在于提供高性能和先進功能,同時采用大小適中的邏輯結構和合適的外設,以實現更為經濟的解決方案。Agilex 5等新型中端設備更是針對需要高性能、低功耗和較小尺寸的應用進行了優化。

中端 FPGA 的評判標準不應局限于邏輯容量。一款真正的中端 FPGA 經過精心優化,融合了高性能邏輯結構、硬核內存控制器、高速收發器、部分重配置和硬核處理器子系統,能夠以更高的成本效益提供出色性能。

需要注意的是,并非所有應用都需要中端設備。請務必選擇能提供全系列 FPGA 設備(由低端到高端)的公司進行合作,從而有效避免在應用復雜度降低,或需求超出中端 FPGA 時更換工具或生態系統。

-

FPGA

+關注

關注

1630文章

21794瀏覽量

605130 -

收發器

+關注

關注

10文章

3453瀏覽量

106166 -

英特爾

+關注

關注

61文章

10006瀏覽量

172136 -

控制器

+關注

關注

112文章

16442瀏覽量

179018

原文標題:現代中端 FPGA 核心要素大揭秘

文章出處:【微信號:英特爾FPGA,微信公眾號:英特爾FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

盤點Arm在CES 2025上的主要亮點

大多數FPGA的程序存儲器(FLASH)為什么都放在外面呢?FPGA的主要應用

差分轉單端電路中,同相端與反相端負載相同嗎?

FPGA技術的主要應用

中科億海微FPGA+ARM核心板在自動噴漆設備中的應用

服務端的測試主要是測什么內容

FPGA學習筆記-電源電壓

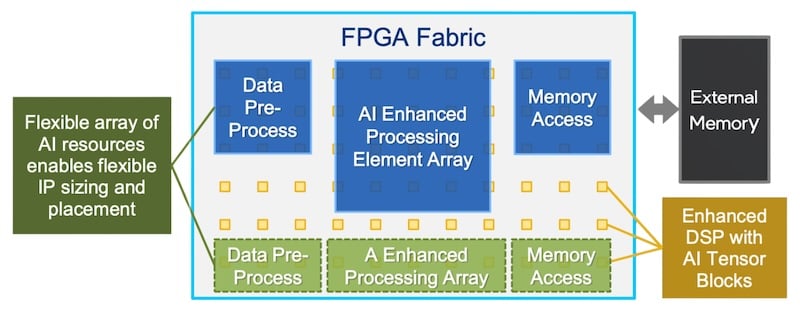

Altera將AI注入新的中端FPGA

fpga芯片工作原理 fpga芯片有哪些型號

fpga芯片的主要特點包括 fpga芯片上市公司

中端FPGA成為主戰場,Altera獨立后的市場格局

現代中端FPGA的主要亮點

現代中端FPGA的主要亮點

評論