本文要點

什么是 EMC 外殼?

選擇 EMC 外殼材料時需要考量的事項。

EMC 外殼設計要點。

如果設備具有電磁兼容標志,則表明它帶來的電磁干擾符合 EMC 標準規定。符合 EMC 標準的設備可在電磁環境中安全運行,并且不會對附近設備的運行產生干擾。為了達到必需的電磁兼容性水平,以便在電磁污染環境中正常運行,EMI 濾波器或設備屏蔽通常會被使用。在本文中,我們將探討什么是 EMC 外殼,并將提供 EMC 外殼設計中需要考量的一些要點。

EMC 外殼基礎知識

電磁波由電場和磁場組成。電場和磁場的場強決定了電磁波的阻抗。電場由高阻抗電壓源電路產生,磁場由低阻抗電流源電路產生。要實現電磁兼容,必須減弱電磁場的強度。

EMC 外殼設計可降低干擾強度

EMI 屏蔽

為了降低干擾強度,會使用 EMI 屏蔽。EMI 屏蔽是一種 EMC 外殼,用在發射器和感受器之間,以減弱電磁場強度。可以將它們視為 EMI 源和敏感設備之間的一道隔斷,通過電磁場衰減來減輕輻射干擾的影響。

屏蔽效能

衡量 EMI 屏蔽是否能很好地減弱電磁場的品質因數為屏蔽效能。屏蔽效能的數學定義是放置 EMI 屏蔽之前和之后的電磁場強度比率,用分貝 (dB) 表示。

電磁場衰減

使用 EMI 屏蔽后,電磁場強度衰減(損耗)取決于屏蔽材料的厚度、磁導率、電導率、干擾頻率等材料特性以及 EMI 源和屏蔽之間的距離。EMI 屏蔽通過吸收、反射和再反射來實現電磁場衰減。

吸收損耗取決于屏蔽厚度和屏蔽材料的吸收系數。反射損耗受電磁波阻抗的影響,與 EMI 屏蔽的固有阻抗成反比。反射發生在空氣到金屬屏蔽的邊界處。再反射損耗很大程度上取決于吸收損耗。再反射發生在金屬屏蔽到空氣的邊界處。

EMC 外殼設計

在任何電氣或電子系統設計中,EMC 設計都是一個重要參數。如果能夠適當過濾設備干擾并且實現完美接地,那么 EMC 外殼設計的重要性會降低。但考慮到 EMI 的不可預測性,最好還是在設計中加入 EMI 屏蔽或 EMC 外殼。

選擇 EMI 屏蔽材料

EMI 屏蔽材料的選擇至關重要,因為材料的物理特性和電氣特性將影響屏蔽效能。目前可供選擇的外殼材料有金屬和非金屬。非金屬材料用于 EMI 屏蔽時,通常需要經過金屬化工藝處理。非金屬材料金屬化技術包括化學鍍、真空沉積、導電噴漆、電弧噴涂等。

任何 EMC 外殼設計都會涉及到一些用于布線的開口、通風或是連接上下游器件的介面。這些開口或孔為電磁耦合提供了通路,因此最好避免 EMI 屏蔽表面出現不連續性。如果外殼上必須存在孔或接縫,那么必須仔細確定這些孔或接縫的尺寸,因為電磁耦合效率取決于孔徑大小和電磁波的波長 ()。一般規則為,微波系列產品的開口不得大于 /50,商用產品的開口不得大于 /20。除開口尺寸外,設計 EMC 外殼時,還需要遵循另外一些準則:

盡量減少不連續性。

外殼接縫處和不連續處需充分粘合。

使用相似的金屬進行粘合,以避免電化學腐蝕。

若為非永久粘合,應確保采用壓力足夠大的緊固方法,保證粘合處嚴絲合縫。

表面不平坦時,使用 EMI 屏蔽墊片。

墊片的厚度為能提供所需強度的最小厚度。

確保外殼的接觸面清潔、無油污、無灰塵、無銹跡、無濕氣。

在 EMC 外殼設計中,要提高屏蔽效能,需要考慮許多細枝末節。如果在材料選擇、孔徑尺寸或墊片尺寸方面疏忽大意,可能會導致電磁耦合的發生,失去電磁屏蔽作用。Cadence 的設計和分析工具套件可以幫助用戶設計和驗證 EMI 屏蔽和外殼。

Cadence Clarity 3D Solver 電磁(EM)仿真器用于設計關鍵的互連、IC 模塊、PCB、封裝的聲學濾波器和系統整合單晶片(SoIC),通過利用 Cadence 分布式多處理技術,克服了傳統 EM 分析軟件的限制,提供幾乎無限的容量和 10 倍的仿真速度提升。

這款強大的 3D EM 仿真器通過支持優化、調整和良率分析的 3DEM 參數化研究,解決未預見的共振和結構件耦合帶來的設計問題。

-

濾波器

+關注

關注

161文章

7859瀏覽量

178703 -

emc

+關注

關注

170文章

3947瀏覽量

183578 -

電磁干擾

+關注

關注

36文章

2330瀏覽量

105581

發布評論請先 登錄

相關推薦

良好的EMC性能的PCB布線設計要點

汽車EMC試驗發展趨勢和新能源電動車EMC試驗

車載電子產品各種需要EMC測試的項目和設計要點的詳細概述

EMC是什么?EMC中的產品架構淺析

汽車DCDC電源芯片EMC設計要點的詳細資料說明

醫療機械電磁兼容EMC整改的要點有哪些

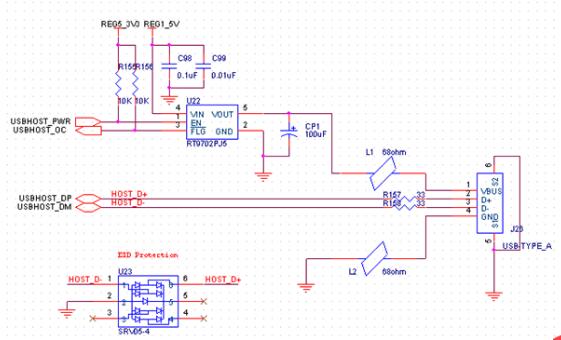

USB硬件EMC設計要點分享

靈活多元的EMC學習方案

EMC外殼設計要點

EMC外殼設計要點

評論