如今,有大量應(yīng)用都依賴于數(shù)模轉(zhuǎn)換器(DAC)和模數(shù)轉(zhuǎn)換器(ADC)。它們?cè)?a target="_blank">信號(hào)處理中非常重要,因?yàn)樗鼈儤?gòu)建了數(shù)字系統(tǒng)和模擬系統(tǒng)之間的橋梁。通過使數(shù)字電路能夠與模擬組件交互,ADC和DAC在音頻處理、電信、數(shù)據(jù)采集系統(tǒng)等領(lǐng)域發(fā)揮著關(guān)鍵作用。

DAC與ADC的作用

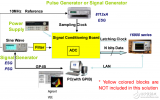

模數(shù)轉(zhuǎn)換器是現(xiàn)代數(shù)據(jù)采集系統(tǒng)(DAQ或DAS系統(tǒng))中的基本構(gòu)建模塊。它們將調(diào)節(jié)后的模擬信號(hào)轉(zhuǎn)換為數(shù)字?jǐn)?shù)據(jù)流,使數(shù)據(jù)采集系統(tǒng)能夠處理、顯示、存儲(chǔ)和分析這些信息。該轉(zhuǎn)換過程中的高精度非常重要,因?yàn)榧词故羌?xì)微的誤差也可能影響下游的分析和處理。

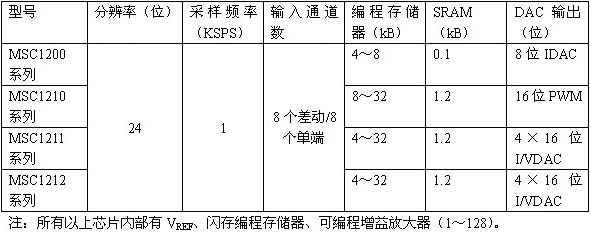

另一方面,數(shù)模轉(zhuǎn)換器是數(shù)字音頻存儲(chǔ)、流媒體傳輸和傳輸?shù)葢?yīng)用不可缺少的部分。DAC將數(shù)字?jǐn)?shù)據(jù)轉(zhuǎn)換為模擬信號(hào),確保音頻再現(xiàn)和其他模擬輸出應(yīng)用中的高保真度。ADC和DAC都需要進(jìn)行測(cè)試以確保最佳性能,特別關(guān)注最大采樣率、位分辨率、總諧波失真(THD)、噪聲、信噪比(SNR)、積分非線性(INL)、微分非線性(DNL)、有效位數(shù)(ENOB)和抖動(dòng)等參數(shù)。

ADC的關(guān)鍵測(cè)試方法

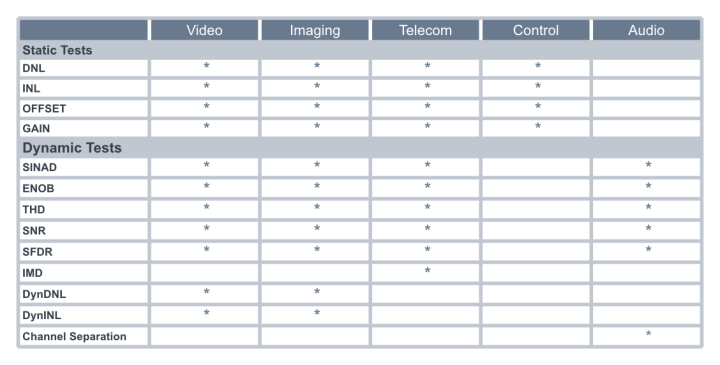

測(cè)試ADC和DAC設(shè)備涉及多種技術(shù),具體方法針是對(duì)每個(gè)轉(zhuǎn)換器的獨(dú)特功能進(jìn)行定制。主要的測(cè)試根據(jù)目標(biāo)應(yīng)用的不同而有所變化,無論是視頻處理、成像、電信、控制系統(tǒng)還是音頻處理。下表匯總了不同應(yīng)用最常見的測(cè)試:

ADC靜態(tài)測(cè)試

積分非線性INL及微分非線性DNL

ADC測(cè)試通常涉及測(cè)量關(guān)鍵性能指標(biāo),通常包括:

偏移誤差

增益誤差

微分非線性

積分非線性

失碼

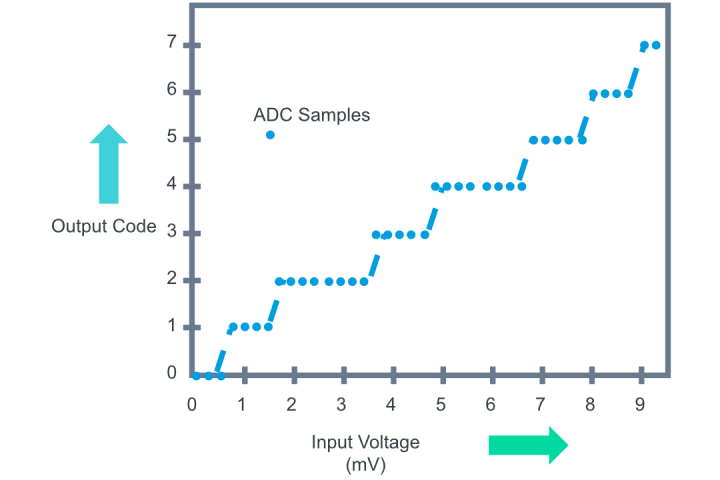

為了測(cè)試DNL和INL,向ADC的輸入端施加一個(gè)信號(hào),并分析輸出碼的出現(xiàn)情況。與DAC測(cè)試不同,在DAC測(cè)試中,數(shù)字碼被施加,并且使用精密電壓表測(cè)量相應(yīng)的模擬輸出;而在ADC測(cè)試中,需要確認(rèn)“決策層”——即碼邊界處的精確輸入電壓。

線性斜坡的直方圖測(cè)試

在這種情況下,施加一個(gè)線性斜坡信號(hào),并分析每個(gè)輸出碼的出現(xiàn)次數(shù)(或命中數(shù))。理想情況下,每個(gè)碼應(yīng)該出現(xiàn)得同樣頻繁。如果一個(gè)碼出現(xiàn)得比其他碼更頻繁,則表示該步長(zhǎng)更寬,DNL為正。相反,如果一個(gè)碼出現(xiàn)得較少,則表示該步長(zhǎng)較小,DNL為負(fù)。一旦 DNL 被確定,INL 就由 DNL 值的累積和得出。

線性斜坡直方圖測(cè)試也稱為碼密度測(cè)試,是測(cè)試ADC靜態(tài)參數(shù)最常用的方法。

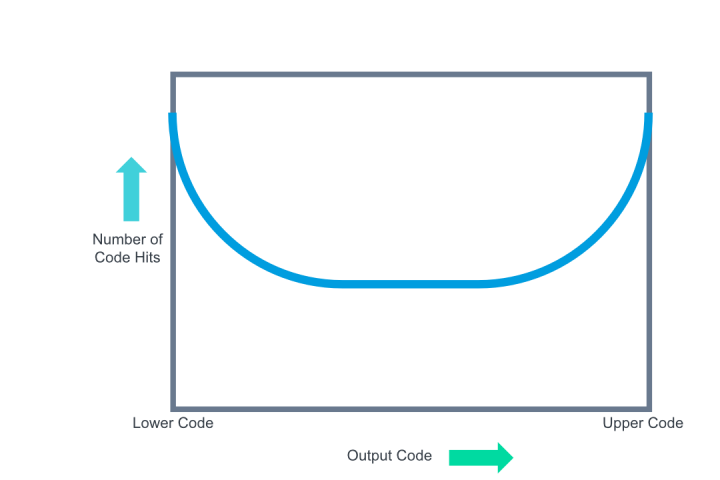

正弦波輸入直方圖測(cè)試

直方圖方法使用正弦波信號(hào)作為ADC的輸入。與其他信號(hào)形式(如線性斜坡)相比,生成純正弦波通常更簡(jiǎn)單。然而,正弦波的電壓分布不均勻,更多的電壓階躍集中在較低和較高的電壓范圍內(nèi)。

在此方法中,分析 ADC 的輸出以評(píng)估轉(zhuǎn)換器在不同電壓下的性能。對(duì)于 DAC,高精度數(shù)字通道與低噪聲正弦波發(fā)生器相結(jié)合,可評(píng)估這些電壓范圍內(nèi)的性能,從而確保最小的失真和噪聲。

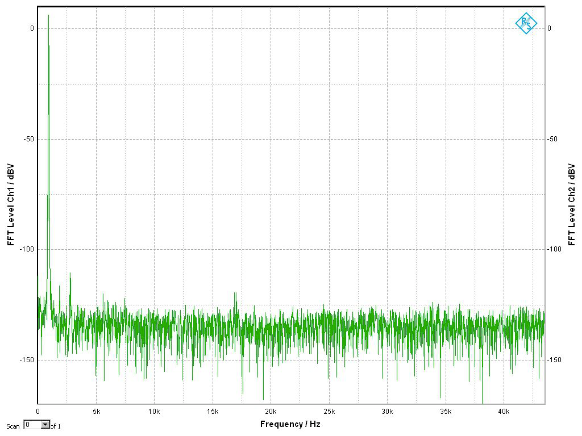

ADC動(dòng)態(tài)測(cè)試ADC測(cè)試中的噪聲源

準(zhǔn)確的ADC測(cè)試必須考慮各種噪聲源,因?yàn)樵肼晻?huì)顯著降低數(shù)據(jù)轉(zhuǎn)換器的性能。三個(gè)主要的噪聲源包括:

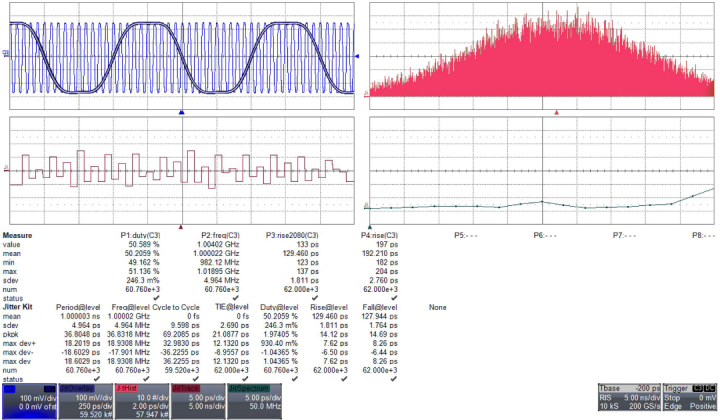

數(shù)字信號(hào)上的抖動(dòng):抖動(dòng)會(huì)在采集瞬間引入誤差,導(dǎo)致采集信號(hào)不準(zhǔn)確。減小抖動(dòng)可以改善信噪比(SNR)。

波形發(fā)生器噪聲:用于測(cè)試目的的信號(hào)質(zhì)量直接影響測(cè)試結(jié)果。測(cè)試設(shè)備的SNR必須高于被測(cè)設(shè)備(DUT),以確保可靠的結(jié)果。

- 電壓基準(zhǔn)和電源中的噪聲:ADC的電壓基準(zhǔn)(Vref)或電源中的噪聲會(huì)轉(zhuǎn)化為輸出噪聲以及偏移和增益誤差。為了更準(zhǔn)確的測(cè)試,建議使用外部電壓基準(zhǔn),并且必須通過參數(shù)(如電源抑制比(PSRR))精準(zhǔn)控制電源噪聲。

DAC測(cè)試相對(duì)簡(jiǎn)單,但仍需精確

與ADC測(cè)試相比,DAC測(cè)試通常要求較低。該過程涉及向DAC施加一系列數(shù)字碼,并使用高精度數(shù)字電壓表(DVM)測(cè)量相應(yīng)的模擬輸出。這可以直接進(jìn)行DNL(微分非線性)和INL(積分非線性)測(cè)量。雖然DAC測(cè)試不那么復(fù)雜,但仍然需要高精度數(shù)字化儀以確保準(zhǔn)確結(jié)果。

在數(shù)字化儀精度不足的情況下,可以采用額外的測(cè)試策略來提高測(cè)量精度:

基座測(cè)試:這種方法涉及從DAC輸出中減去一個(gè)已知的基座電壓,以提高小信號(hào)測(cè)量的準(zhǔn)確性。

補(bǔ)償源差分放大器:此技術(shù)使用差分放大器來抵消噪聲或不需要的信號(hào)分量,進(jìn)一步提高DNL和INL測(cè)量的準(zhǔn)確性。

這些方法允許進(jìn)行更精確的測(cè)量,確保檢測(cè)到并校正DAC性能中的最小不準(zhǔn)確之處。

基座測(cè)試

當(dāng)需要更高精度時(shí),基座測(cè)試可以增強(qiáng)DAC測(cè)試的精度。數(shù)字處理儀器的斜坡發(fā)生器可以通過內(nèi)部連接用作數(shù)字化儀的基座,而不是僅僅依賴數(shù)字化儀。首先使用高精度系統(tǒng)電壓表對(duì)斜坡進(jìn)行預(yù)表征,確保充分了解其特性。這種方法允許數(shù)字化儀在較小的范圍內(nèi)工作,顯著提高其測(cè)量分辨率,并能夠更精確地測(cè)試DAC輸出。

補(bǔ)償源差分放大器

對(duì)于基座配置也無法提供所需精度的情況,可以采用補(bǔ)償源差分放大器技術(shù)。在這種方法中,一個(gè)高穩(wěn)定性電壓源作為“補(bǔ)償”電壓施加到被測(cè)DAC上。補(bǔ)償源的輸出點(diǎn)由高精度系統(tǒng)電壓表(如HP3458A)進(jìn)行預(yù)表征,以確保獲得精確的參考值。

補(bǔ)償源和DAC形成差分輸入給高穩(wěn)定性、低漂移的可編程增益放大器(PGA)。PGA放大DAC輸出與補(bǔ)償源之間的差值。這種方法隔離了預(yù)期輸出和實(shí)際輸出之間的小差異,從而能夠高度準(zhǔn)確地測(cè)量DAC的性能。通過逐點(diǎn)差異測(cè)量最小有效位(LSB)步長(zhǎng)來計(jì)算DNL(微分非線性),然后對(duì)這些結(jié)果進(jìn)行積分以確定INL(積分非線性)。

SPEA 的 ADC 和 DAC 測(cè)試解決方案

測(cè)試ADC和DAC設(shè)備需要能夠提供高質(zhì)量數(shù)字信號(hào)和精確模擬源的復(fù)雜設(shè)備。SPEA的DOT 系列測(cè)試儀提供了準(zhǔn)確性和性能的完美結(jié)合。SPEA設(shè)備的高精度數(shù)字通道、高信噪比和低總諧波失真使其成為ADC和DAC全面測(cè)試的理想選擇。

對(duì)于DAC測(cè)試,SPEA儀器提供高精度的模擬測(cè)量,從而實(shí)現(xiàn)精確的性能評(píng)估。對(duì)于ADC測(cè)試,SPEA的測(cè)試儀提供低抖動(dòng)的高質(zhì)量數(shù)字信號(hào),以及具有高光譜純度和信噪比的模擬源,這對(duì)于進(jìn)行線性測(cè)試和噪聲分析至關(guān)重要。

-

adc

+關(guān)注

關(guān)注

99文章

6533瀏覽量

545452 -

dac

+關(guān)注

關(guān)注

43文章

2309瀏覽量

191378 -

采集系統(tǒng)

+關(guān)注

關(guān)注

0文章

171瀏覽量

20663

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速 ADC/DAC 測(cè)試原理及測(cè)試方法

如何實(shí)現(xiàn)對(duì)ADC/DAC的靜態(tài)和動(dòng)態(tài)特性的測(cè)試?

STM32 DAC簡(jiǎn)介

STM32上的DAC簡(jiǎn)介

ADC及DAC的歷史進(jìn)程概況

ADC/DAC,ADC/DAC的原理是什么?

高精度、高速ADC/DAC測(cè)試原理及測(cè)試方法的介紹

高速ADC、DAC測(cè)試原理及測(cè)試方法

blog高速ADC、DAC測(cè)試原理及測(cè)試方法

SPEA自動(dòng)化測(cè)試助力電子設(shè)備升級(jí)

并行接口的ADC、DAC的測(cè)試方法

新加坡裕廊西中學(xué)到訪SPEA蘇州

Rinaldi代表團(tuán)到訪SPEA總部:探索全球頂尖自動(dòng)化測(cè)試技術(shù)

SPEA—ADC與DAC測(cè)試簡(jiǎn)介

SPEA—ADC與DAC測(cè)試簡(jiǎn)介

評(píng)論