Verilog例化說(shuō)明

1.什么是模塊例化?為什么要例化?

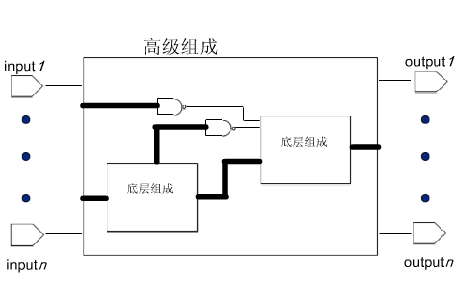

模塊例化可以理解成模塊調(diào)用。對(duì)于一個(gè)FPGA工程,通常是由一個(gè)頂層模塊與多個(gè)功能子模塊組成,為了實(shí)現(xiàn)頂層模塊與子模塊的連接,需要進(jìn)行模塊間的例化(或說(shuō)是調(diào)用)。在一個(gè)FPGA項(xiàng)目工程中,其輸入、輸出端口命名通常在設(shè)計(jì)前期就已確定下來(lái),但會(huì)存在一些中間變量,一個(gè)工程可能會(huì)讓不同的工程師在不同的時(shí)間段內(nèi)共同完成,不同的人對(duì)于這些變量的命名會(huì)有所不同,故例化很有必要。

2.實(shí)例說(shuō)明例化方法

實(shí)例:靜態(tài)數(shù)碼管顯示

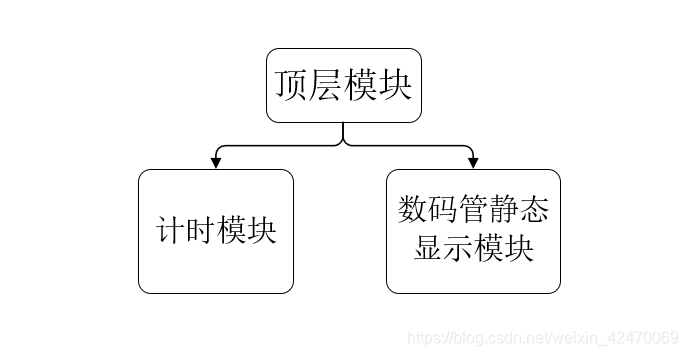

根據(jù)功能將 FPGA 頂層例化了以下兩個(gè)功能子模塊:計(jì)時(shí)模(time_count)和數(shù)碼管靜態(tài)顯示模塊(seg_led_static),如下圖所示:

1.計(jì)時(shí)模塊(僅顯示端口及參數(shù))

module time_count( inputclk , // 時(shí)鐘信號(hào) inputrst_n , // 復(fù)位信號(hào) output reg flag // 一個(gè)時(shí)鐘周期的脈沖信號(hào) ); //parameter define parameter MAX_NUM = 25000_000; // 計(jì)數(shù)器最大計(jì)數(shù)值 ......(省略功能代碼) endmodule

2.數(shù)碼管靜態(tài)顯示模塊(僅顯示端口及參數(shù))

module seg_led_static ( input clk , // 時(shí)鐘信號(hào) input rst_n , // 復(fù)位信號(hào)(低有效) input add_flag, // 數(shù)碼管變化的通知信號(hào) output reg [5:0] sel , // 數(shù)碼管位選 output reg [7:0] seg_led // 數(shù)碼管段選 ); ......(省略功能代碼) endmodule

3.頂層模塊(著重看下面“例化計(jì)時(shí)模塊”、“例化數(shù)碼管靜態(tài)顯示模塊”)

module seg_led_static_top ( input sys_clk , // 系統(tǒng)時(shí)鐘 input sys_rst_n, // 系統(tǒng)復(fù)位信號(hào)(低有效) output [5:0] sel , // 數(shù)碼管位選 output [7:0] seg_led // 數(shù)碼管段選 ); //parameter define parameter TIME_SHOW = 25'd25000_000; // 數(shù)碼管變化的時(shí)間間隔0.5s //wire define wire add_flag; // 數(shù)碼管變化的通知信號(hào) //例化計(jì)時(shí)模塊 time_count #( //參數(shù)例化使用’#‘ .MAX_NUM (TIME_SHOW) ) u_time_count( .clk (sys_clk ), .rst_n (sys_rst_n), .flag (add_flag ) ); //例化數(shù)碼管靜態(tài)顯示模塊 seg_led_static u_seg_led_static ( .clk (sys_clk ), .rst_n (sys_rst_n), .add_flag (add_flag ), .sel (sel ), .seg_led (seg_led ) ); endmodule

上面給出了頂層模塊的完整代碼,子模塊只有模塊的端口和參數(shù)定義的代碼。這是因?yàn)轫攲幽K對(duì)子模塊做例化時(shí),只需要知道子模塊的端口信號(hào)名,而不用關(guān)心子模塊內(nèi)部具體是如何實(shí)現(xiàn)的。

如果子模塊內(nèi)部使用parameter 定義了一些參數(shù),Verilog 也支持對(duì)參數(shù)的例化(也叫參數(shù)的傳遞),即頂層模塊可以通過(guò)例化參數(shù)來(lái)修改子模塊內(nèi)定義的參數(shù)。

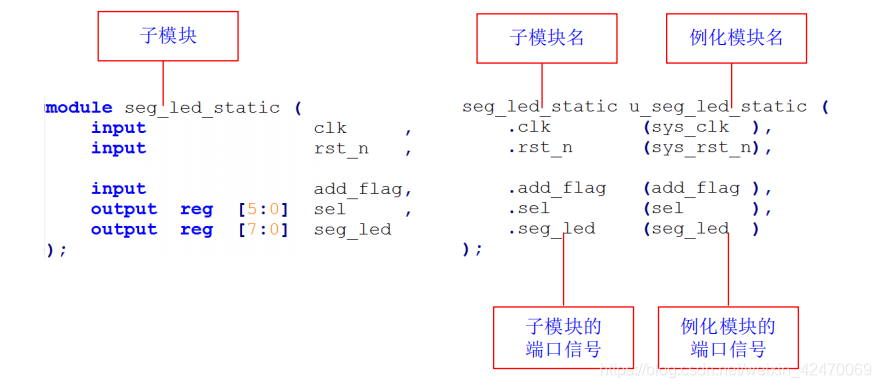

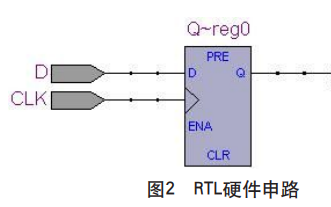

下圖為模塊例化。

上圖右側(cè)是例化的數(shù)碼管靜態(tài)顯示模塊,子模塊名是指被例化模塊的模塊名,而例化模塊名相當(dāng)于標(biāo)識(shí),當(dāng)例化多個(gè)相同模塊時(shí),可以通過(guò)例化名來(lái)識(shí)別哪一個(gè)例化,我們一般命名為“u_”+“子模塊名”。信號(hào)列表中“.”之后的信號(hào)是數(shù)碼管靜態(tài)顯示模塊定義的端口信號(hào),括號(hào)內(nèi)的信號(hào)則是頂層模塊聲明的信號(hào),這樣就將頂層模塊的信號(hào)與子模塊的信號(hào)一一對(duì)應(yīng)起來(lái),同時(shí)需要注意信號(hào)的位寬要保持一致。

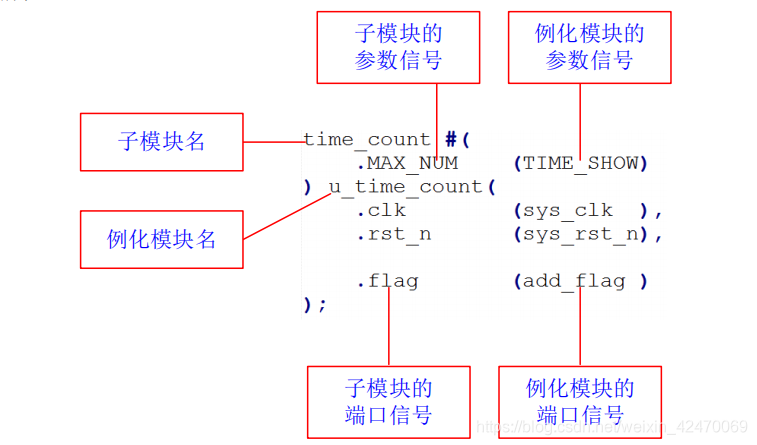

接下來(lái)再來(lái)介紹一下參數(shù)的例化,參數(shù)的例化是在模塊例化的基礎(chǔ)上,增加了對(duì)參數(shù)的信號(hào)定義。

下圖為參數(shù)例化:

在對(duì)參數(shù)進(jìn)行例化時(shí),在模塊名的后面加上“#”,表示后面跟著的是參數(shù)列表。計(jì)時(shí)模塊定義的MAX_NUM 和頂層模塊的 TIME_SHOW 都是等于25000_000,當(dāng)在頂層模塊定義 TIME_SHOW=12500_000時(shí),那么子模塊的 MAX_NUM 的值實(shí)際上是也等于 12500_000。當(dāng)然即使子模塊包含參數(shù),在做模塊的例化時(shí)也可以不添加對(duì)參數(shù)的例化,這樣的話,子模塊的參數(shù)值等于該模塊內(nèi)部實(shí)際定義的值。

值得一提的是,Verilog 語(yǔ)法中的localparam 代表的意思同樣是參數(shù)定義,用法和 parameter 基本一致,區(qū)別在于 parameter 定義的參數(shù)可以做例化,而 localparam 定義的參數(shù)是指本地參數(shù),上層模塊不可以對(duì)localparam 定義的參數(shù)做例化。

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110234 -

數(shù)碼管顯示

+關(guān)注

關(guān)注

0文章

63瀏覽量

13843 -

顯示模塊

+關(guān)注

關(guān)注

1文章

50瀏覽量

23583

原文標(biāo)題:Verilog例化說(shuō)明

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

例說(shuō)Verilog HDL和VHDL區(qū)別

例說(shuō)FPGA連載62:電子點(diǎn)菜單之FIFO例化說(shuō)明

在verilog中調(diào)用VHDL模塊

在verilog中調(diào)用VHDL模塊

Verilog教程之Verilog的命令格式資料說(shuō)明

FPGA視頻教程之Verilog基礎(chǔ)的詳細(xì)資料說(shuō)明

實(shí)現(xiàn)Verilog HDL模塊化程序設(shè)計(jì)的詳細(xì)資料說(shuō)明

Verilog HDL教程135例免費(fèi)下載

Verilog例化說(shuō)明

Verilog例化說(shuō)明

評(píng)論