產(chǎn)品簡(jiǎn)述

MS8923/MS8923S 是一款差分輸入、高速、低功耗比較器,

具有互補(bǔ) TTL 輸出。其傳輸延時(shí)在 10ns 左右,輸入共模范圍可

以到負(fù)軌。MS8923/MS8923S 可以在線性區(qū)保持輸出穩(wěn)定特性,

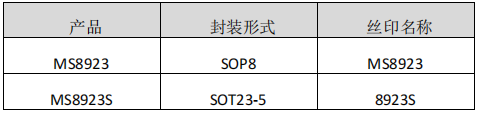

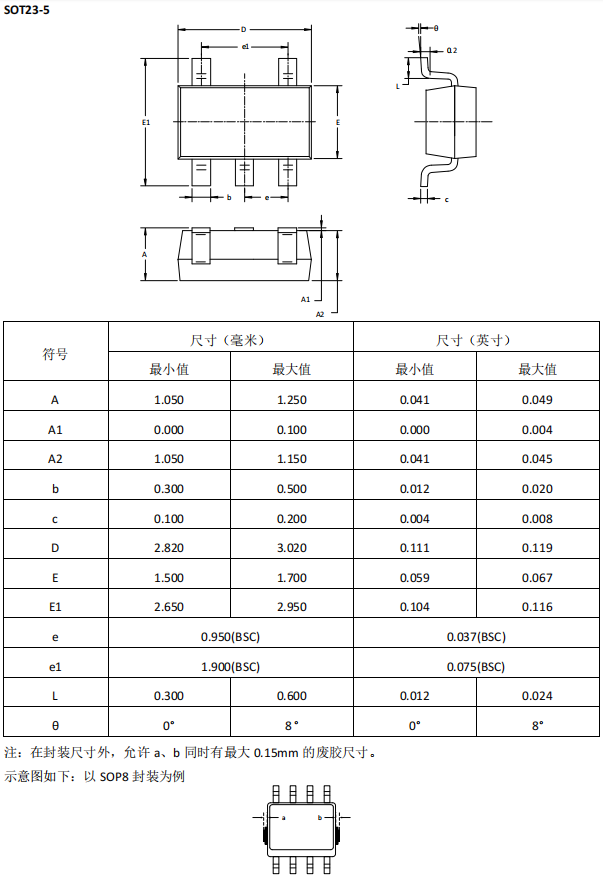

MS8923 采用 SOP8 封裝,MS8923S 采用 SOT23-5 封裝。

主要特點(diǎn)

?快傳輸延時(shí):10ns

?+5V 單電源供電或±5V 雙電源供電

?低功耗:6mA

?無最小輸入信號(hào)變化率要求

?線性區(qū)穩(wěn)定

?輸入失調(diào)電壓:0.8mV

?工作溫度范圍:-40°C?120°C

應(yīng)用

?手持及電池供電系統(tǒng)

?掃描儀和機(jī)頂盒

?高速差分線性接收器

?窗口比較器

?零交疊監(jiān)測(cè)器

?高速采樣電路

?V/F 轉(zhuǎn)換器

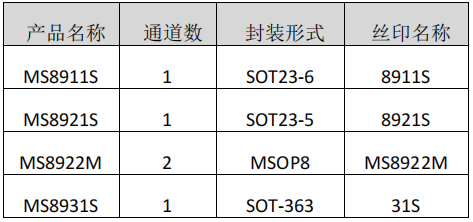

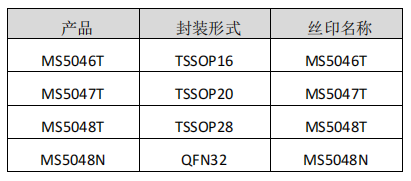

產(chǎn)品規(guī)格分類

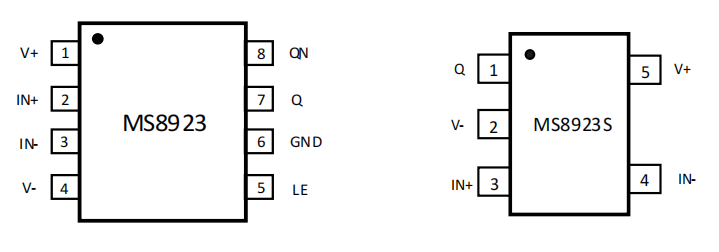

管腳圖

管腳說明

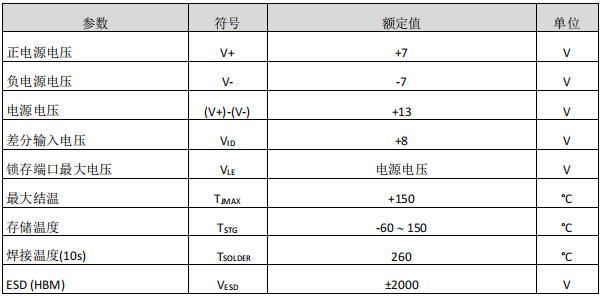

極限參數(shù)

芯片使用中,任何超過極限參數(shù)的應(yīng)用方式會(huì)對(duì)器件造成永久的損壞,芯片長(zhǎng)時(shí)間處于極限工作

狀態(tài)可能會(huì)影響器件的可靠性。極限參數(shù)只是由一系列極端測(cè)試得出,并不代表芯片可以正常工作在

此極限條件下。

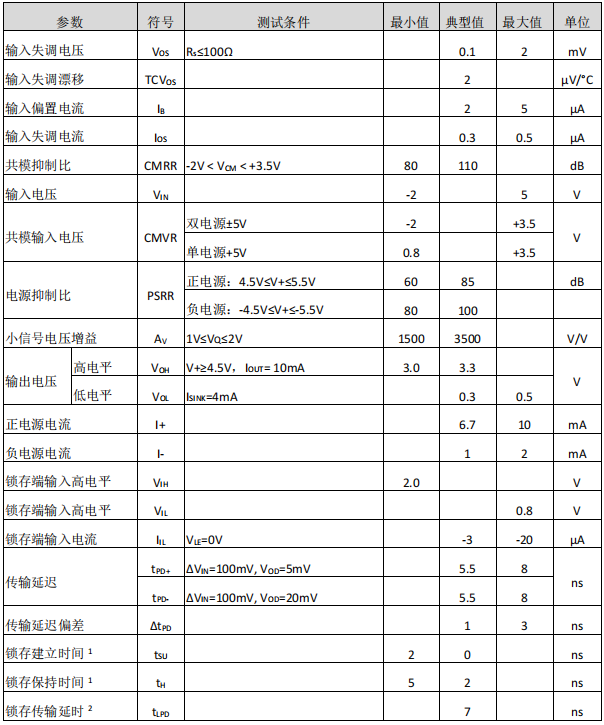

電氣參數(shù)

若無特別說明,TA= 25°C,VQ=+1.4V,V+ = +5V,V- = -5V,VLE=0V。

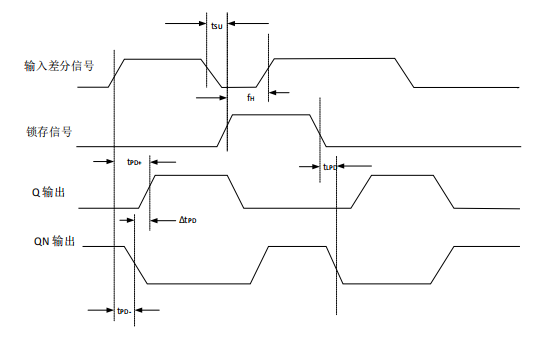

注:1. 鎖存建立時(shí)間是輸入信號(hào)先于鎖存信號(hào)的穩(wěn)定時(shí)間,保持時(shí)間是輸入信號(hào)在鎖存信號(hào)之后必須

保持不變的時(shí)間。

2. 鎖存?zhèn)鬏斞訒r(shí)時(shí)間是從鎖存信號(hào)變化到輸出響應(yīng)的時(shí)間。

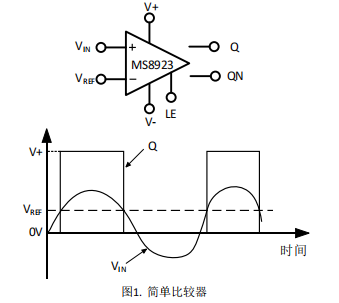

典型應(yīng)用圖

簡(jiǎn)單比較器

一個(gè)簡(jiǎn)單的比較器電路用來把輸入的模擬信號(hào)轉(zhuǎn)換成數(shù)字信號(hào)輸出。比較器比較非反向輸入端的

電壓(VIN)和反向端的基準(zhǔn)電壓(VREF),如果VIN小于VREF,輸出為低,VIN大于VREF,則輸出為高。

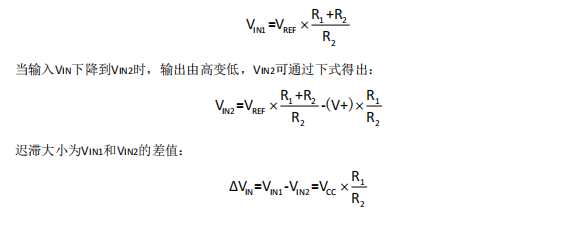

遲滯效應(yīng)

如果簡(jiǎn)單比較器的差分輸入與比較器失調(diào)電壓接近,那么比較器輸出就會(huì)出現(xiàn)波動(dòng)或則噪聲波

動(dòng),這在一個(gè)輸入電壓與另一個(gè)輸入電壓相等或很接近時(shí)容易出現(xiàn)。遲滯可以解決這個(gè)問題,遲滯可

以產(chǎn)生兩個(gè)比較閾值(一個(gè)用于上升過程,一個(gè)用于下降過程),遲滯大小就是兩個(gè)比較閾值的差。

當(dāng)兩個(gè)輸入很接近時(shí),遲滯可以使一個(gè)電壓可以迅速的超過另一個(gè)電壓。這樣,把輸入電壓移出輸出

波動(dòng)的區(qū)域。

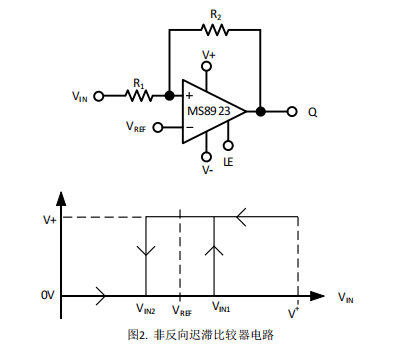

如圖2所示,遲滯可以通過兩個(gè)電阻連接到非反向端構(gòu)成,即構(gòu)成正反饋。當(dāng)輸入VIN上升到VIN1,

輸出由低變?yōu)楦撸琕IN1可通過下式得出:

輸入

MS8923/MS8923S的輸入偏置電流幾乎為零,這使得可以使用大阻抗的電路,而不需要考慮阻抗匹

配,也可以使用小電容的R–C時(shí)序電路,減小了電容的使用以及電路板空間。

電路板走線及旁路

雖然MS8923/MS8923S穩(wěn)定,并具有一定抗干擾能力,但采用合適的旁路電容和地線拾取很重

要。采用0.1μF的陶瓷電容可以提供干凈電源,最短的信號(hào)線可以減小雜散電容。

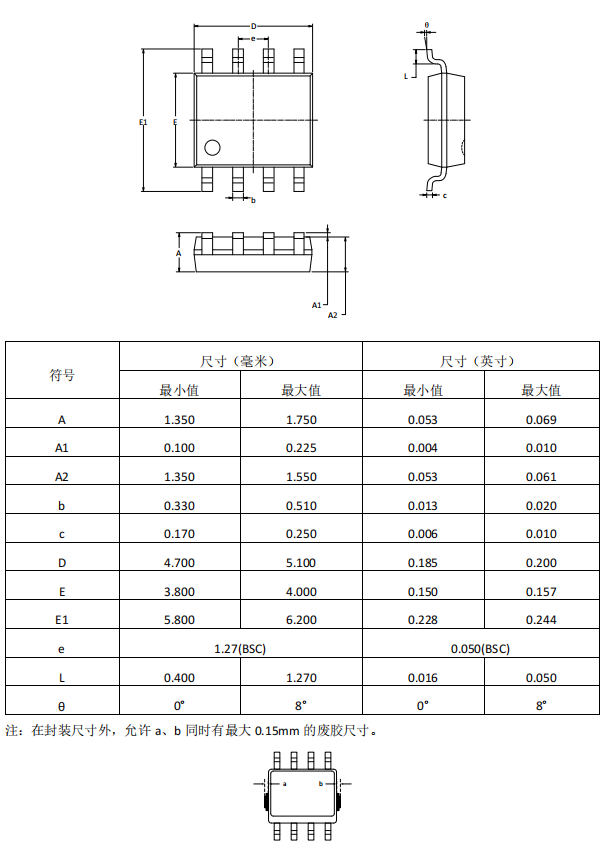

封裝外形圖

SOP8

——愛研究芯片的小王

審核編輯 黃宇

-

比較器

+關(guān)注

關(guān)注

14文章

1656瀏覽量

107307

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談瑞盟科技·MS1030——超聲波流量高精度測(cè)量電路

MS8628/8629/8630——零漂移、單電源、輸入輸出軌到軌高精度運(yùn)放

MS8911S/8921S/8922M/8931S——4ns 延時(shí)、軌到軌高速比較器

MS5198T/MS5199T——低噪聲、低功耗、16/24 位 ∑-Δ ADC

MS31051S/D——低壓 5V DC 電機(jī)驅(qū)動(dòng)

MS3111S——低壓 5V DC 電機(jī)驅(qū)動(dòng)

MS5046T/5047T/5048T/5048N——2kSPS、16bit Σ-Δ ADC

MS1242/MS1243——24bit 高精度、低功耗模數(shù)轉(zhuǎn)換器

MS5196T/MS5197T——低噪聲、低功耗、16/24 位∑-ΔADC

MS5194T/MS5195T——低噪聲、低功耗、24/16 位 ∑-Δ ADC

MS5192T/MS5193T——低噪聲、低功耗、16/24 位∑-ΔADC

MS1205N——激光測(cè)距用高精度時(shí)間測(cè)量(TDC)電路

MS1022——高精度時(shí)間測(cè)量(TDC)電路

MS3142/MS3142S 馬達(dá)驅(qū)動(dòng) IC 在自動(dòng)打蛋機(jī)研發(fā)中的神奇表現(xiàn)

MS8923/MS8923S——低壓、高精度、推挽輸出比較器

MS8923/MS8923S——低壓、高精度、推挽輸出比較器

評(píng)論